界面报错如下:

Retrieving Flash info... Initialization done, programming the memory ===== mrd->addr=0xF800025C, data=0x00000000 ===== BOOT_MODE REG = 0x00000000 Downloading FSBL... Running FSBL... Finished running FSBL. ===== mrd->addr=0xF8000110, data=0x000FA220 ===== READ: ARM_PLL_CFG (0xF8000110) = 0x000FA220 ===== mrd->addr=0xF8000100, data=0x00028008 ===== READ: ARM_PLL_CTRL (0xF8000100) = 0x00028008 ===== mrd->addr=0xF8000120, data=0x1F000200 ===== READ: ARM_CLK_CTRL (0xF8000120) = 0x1F000200 ===== mrd->addr=0xF8000118, data=0x001452C0 ===== READ: IO_PLL_CFG (0xF8000118) = 0x001452C0 ===== mrd->addr=0xF8000108, data=0x0001E008 ===== READ: IO_PLL_CTRL (0xF8000108) = 0x0001E008 Info: Remapping 256KB of on-chip-memory RAM memory to 0xFFFC0000. ===== mrd->addr=0xF8000008, data=0x00000000 ===== ===== mwr->addr=0xF8000008, data=0x0000DF0D ===== MASKWRITE: addr=0xF8000008, mask=0x0000FFFF, newData=0x0000DF0D ===== mwr->addr=0xF8000910, data=0x000001FF ===== ===== mrd->addr=0xF8000004, data=0x00000000 ===== ===== mwr->addr=0xF8000004, data=0x0000767B ===== MASKWRITE: addr=0xF8000004, mask=0x0000FFFF, newData=0x0000767B Problem in running uboot Flash programming initialization failed. ERROR: Flash Operation Failed

If that FSBL fails (example hangs in DDR Init) the your u-boot under the hood won't work (Problem in running uboot).

In the FSBL you pass to the Programmer, enable all the UART log and see if it fails.

If the error is "Problem in running uboot", I suspect the FSBL specified to the flash programmer is NOT executing properly.

Best way to debug this is to enable all the FSBL prints log and check the UART print out during flash programmer.

Does the FSBL handoff properly or the prints are incomplete?

Please report the UART log in this post so I can take a look.

Project Explorer 展开 fsbl - src,打开 fsbl_debug.h,添加调试宏

#define FSBL_DEBUG_INFO

可以看到是DDR初始化失败了。

DDR勾选 internal vref

之后在烧写过程中又报了

Start and/or end address not on sector boundary的错误

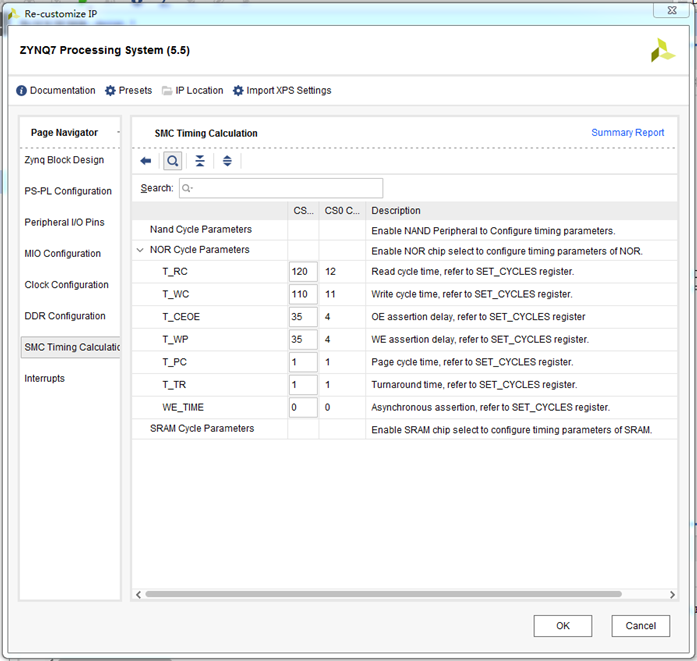

需要根据手册修改controller的SMC参数