目录:

第一章:电容

第二章:电容的种类(主板)

第三章:去耦电容和旁路电容

第四章:高速信号中耦合电容的应用

第五章:HDMI、EDP、LVDS、PCIE、SATA、USB3.0等加AC耦合电容问题综合概述

第六章:PCB上AC耦合电容的优化设计

第七章:AC耦合电容的选择

第一章:电容

1.1 电容分类

常见的电容材质有:Y5V,X5R,X7R,NPO(COG)

常见的耐压值有:6.3V,10V,16V,25V,50V

|

陶瓷电容CCAP |

钽电容TCAP |

高分子电容POSCAP |

铝电解电容SCAP |

|

|

0201 |

||||

|

0402 |

||||

|

0603 |

||||

|

0805 |

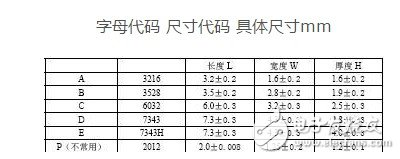

3216(A) |

|||

|

1206 |

3528(B) |

|||

|

6032(C) |

||||

|

7343(D) |

||||

|

线路设计时应该注意,POSCAP是有极性的电容器,反向电压会造成漏电流加大或短路。另外,POSCAP即使在规范、规定的条件内进行回流焊,焊接后的漏电流也有可能变大。不施加电压的高温无负荷周期试验等也会引起漏电流加大,因此规定禁止在保持高阻抗线路、耦合线路、定时线路、漏电流会带来大的影响的线路、超出额定电压的串联线路使用 |

注意事项 POSCAP的构造基本上与普通钽电解电容器相同,最大的不同是电解质采用了导电性高分子材料 |

|||

第二章:电容的种类(主板)

1、滤波电容:它接在直流电压的正负极之间,以滤除直流电源中不需要的交流成分,使直流电平滑,通常采用大容量的电解电容,也可以在电路中同时并接其它类型的小容量电容以滤除高频交流电。

2、退耦电容:并接于放大电路的电源正负极之间,防止由电源内阻形成的正反馈而引起的寄生振荡。

3、旁路电容:在交直流信号的电路中,将电容并接在电阻两端或由电路的某点跨接到公共电位上,为交流信号或脉冲信号设置一条通路,避免交流信号成分因通过电阻产生压降衰减。

4、耦合电容:在交流信号处理电路中,用于连接信号源和信号处理电路或者作为两放大器的级间连接,用于隔断直流,让交流信号或脉冲信号通过,使前后级放大电路的直流工作点互不影响。

5、调谐电容:连接在谐振电路的振荡线圈两端,起到选择振荡频率的作用。

6、衬垫电容:与谐振电路主电容串联的辅助性电容,调整它可使振荡信号频率范围变小,并能显著地提高低频端的振荡频率。

7、补偿电容:与谐振电路主电容并联的辅助性电容,调整该电容能使振荡信号频率范围扩大。

8、中和电容:并接在三极管放大器的基极与发射极之间,构成负反馈网络,以抑制三极管极间电容造成的自激振荡。

9、稳频电容:在振荡电路中,起稳定振荡频率的作用。

10、定时电容:在RC时间常数电路中与电阻R串联,共同决定充放电时间长短的电容。

11、加速电容:接在振荡器反馈电路中,使正反馈过程加速,提高振荡信号的幅度。

12、缩短电容:在UHF高频头电路中,为了缩短振荡电感器长度而串联的电容。

13、克拉波电容:在电容三点式振荡电路中,与电感振荡线圈串联的电容,起到消除晶体管结电容对频率稳定性影响的作用。

14、锡拉电容:在电容三点式振荡电路中,与电感振荡线圈两端并联的电容,起到消除晶体管结电容的影响,使振荡器在高频端容易起振。

15、稳幅电容:在鉴频器中,用于稳定输出信号的幅度。

16、预加重电容:为了避免音频调制信号在处理过程中造成对分频量衰减和丢失,而设置的RC高频分量提升网络电容。

17、去加重电容:为了恢复原伴音信号,要求对音频信号中经预加重所提升的高频分量和噪声一起衰减掉,设置RC在网络中的电容。

18、移相电容:用于改变交流信号相位的电容。

19、反馈电容:跨接于放大器的输入与输出端之间,使输出信号回输到输入端的电容。

20、降压限流电容:串联在交流回路中,利用电容对交流电的容抗特性,对交流电进行限流,从而构成分压电路。

21、逆程电容:用于行扫描输出电路,并接在行输出管的集电极与发射极之间,以产生高压行扫描锯齿波逆程脉冲,其耐压一般在1500伏以上。

22、S校正电容:串接在偏转线圈回路中,用于校正显象管边缘的延伸线性失真。

23、自举升压电容:利用电容器的充、放电储能特性提升电路某点的电位,使该点电位达到供电端电压值的2倍。

24、消亮点电容:设置在视放电路中,用于关机时消除显象管上残余亮点的电容。

25、软启动电容:一般接在开关电源的开关管基极上,防止在开启电源时,过大的浪涌电流或过高的峰值电压加到开关管基极上,导致开关管损坏。

26、启动电容:串接在单相电动机的副绕组上,为电动机提供启动移相交流电压,在电动机正常运转后与副绕组断开。

27、运转电容:与单相电动机的副绕组串联,为电动机副绕组提供移相交流电流。在电动机正常运行时,与副绕组保持串接。

第三章:去耦电容和旁路电容

在电子电路中,去耦电容和旁路电容都是起到抗干扰的作用,电容所处的位置不同,称呼就不一样了。对于同一个电路来说,旁路(bypass)电容是把输入信号中的高频噪声作为滤除对象,把前级携带的高频杂波滤除,而去耦(decoupling)电容也称退耦电容,是把输出信号的干扰作为滤除对象。

原理

去耦电容用在放大电路中不需要交流的地方,用来消除自激,使放大器稳定工作。从电路来说,总是存在驱动的源和被驱动的负载。如果负载电容比较大,驱动电路要把电容充电、放电,才能完成信号的跳变,在上升沿比较陡峭的时候,电流比较大,这样驱动的电流就会吸收很大的电源电流,由于电路中的电感,电阻,这种电流相对于正常情况来说实际上就是一种噪声,会影响前级的正常工作。这就是耦合。

3.1 旁路电容Bypass Capacitor

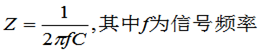

电容的一个重要的电器特性是"通交流,隔直流",其电抗的计算公式如下:

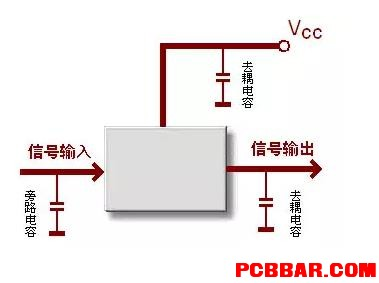

旁路电容的作用就是将系统中的高频噪声旁路到GND。一般是在电源引脚和GND之间并联一些容值较小的(典型值0.1uF)电容,如图 2所示,用于将高频噪声短路到GND,从而避免噪声进入器件的供电引脚。

滤除高频噪声是旁路电容最主要的功能,但是如果考虑一下电容是如何完成这个功能的,或者说电容是如何做到通交流,隔直流的。其实本质也是电容作为一个电能的储能器件,在两极板间电压差很快增大时,给电容充电;电压差减小时,电容放电。从这个角度分析的话,旁路电容也可以看成一种小的电能储存器(Energy Reservoir),

2.去耦电容De-coupling Capacitor

第四章:高速信号中耦合电容的应用

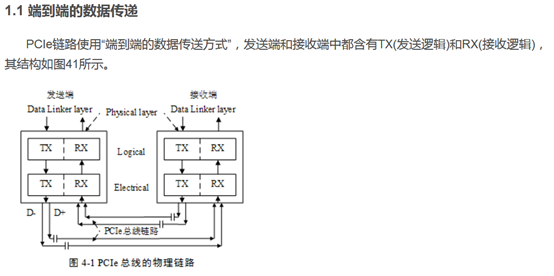

4.1 交流耦合与直流耦合

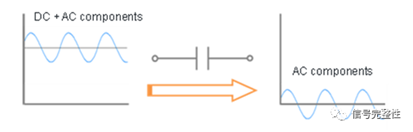

- 交流耦合(AC Coupling):就是通过隔直电容耦合,去掉了直流分量

- 直流耦合(DC Coupling):就是直流、交流一起过,不去掉直流分量。

- 比如在3V的直流电平上叠加一个1Vpp的弦波,如果用直流耦合,看到的是以3V为基准,+/-0.5V的正弦波;如果用交流耦合,看到的是以0V为基准,+/-0.5V的正弦波

4.2.为什么高频需要AC耦合电容

4.2.1 AC电容耦合的好处

(1) 主要就是提供直流偏压,改善了噪声容限。

(2) 使用电容耦合,可以让前后级电路的直流通路阻断,从而使选择静态工作点方便

4.2.2 什么情况下需要AC耦合电容

一般当我们连接有不同的供电电压的两个系统时或者支持热插拔时,高速信号可能会采用电容耦合的方式。

例如采用AC耦合总线:DP、 EDP 、HDMI、PCIE、USB、SATA

4.2.3 直接耦合

高频直接耦合的也很多,例如:PEG(显卡)、DMI、MIPI就是直接耦合;简言之,在需要隔离直流分量时用电容

第五章:HDMI、EDP、LVDS、PCIE、SATA、USB3.0等加AC耦合电容问题综合概述

5.1 USB3.0的TX信号AC加耦合电容,为什么USB2.0上面不加AC耦合电容呢?

USB3.0、USB3.1都是有数据编码的,数据是连续的,采用AC耦合可以更好抑制共模噪声。USB2.0要兼容原来的1.0和1.1,正负线上有同时为高或为低的状态,不能用AC耦合。

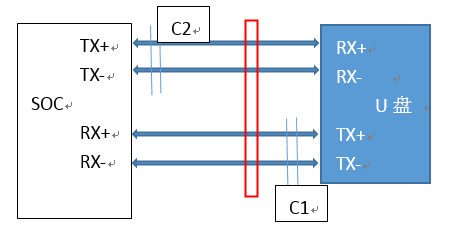

5.2为什么PCIE3.0和USB3.0的RX不加AC耦合电容呢?

其实看下图主板RX端也要加AC耦合电容的,根据规范要求各个Device在TX发送端都要加AC耦合电容,所以主板RX对应的U盘的TX端其实也加了AC耦合电容

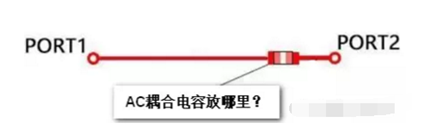

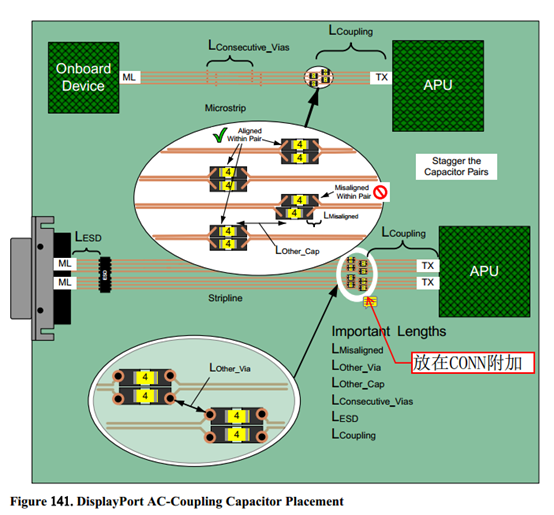

5.3 AC耦合电容摆放的位置

电容看成一个阻抗不连续点(所以要求尽量跟传输线匹配),如果靠近接收端放,相同的反射系数下,信号经过通道衰减之后再反射会比一开始就反射的能量小。所以大多数的串行链路都要求靠接收端放,使用ADS 仿真也可以发现放在接收端眼图质量要好。另外,在信号传输过程中,也可能串扰进去一

些直流分量,导致接收出问题,所以对于高速差分信号(要求交流)一般在接收端加入耦合电容。耦合电容容值标准上有要求,太大太小都不好。

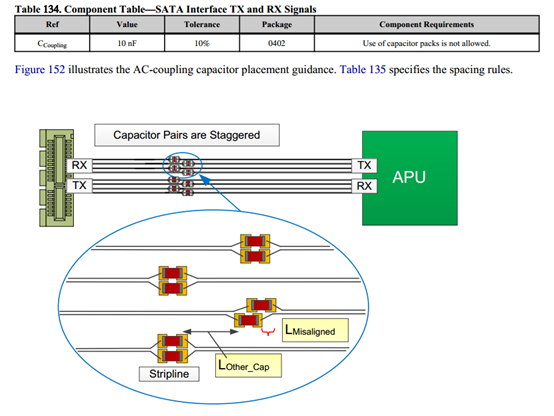

2、在SATA 信号传输的过程中会有衰减,传的距离越长衰减会越厉害,所以会给他一个载波(也就是直流分量),在进入IC 或者SATA device 后再用串电容的方法把直流分量滤掉,这样做会有比较好的信号质量,也就是隔直作用。

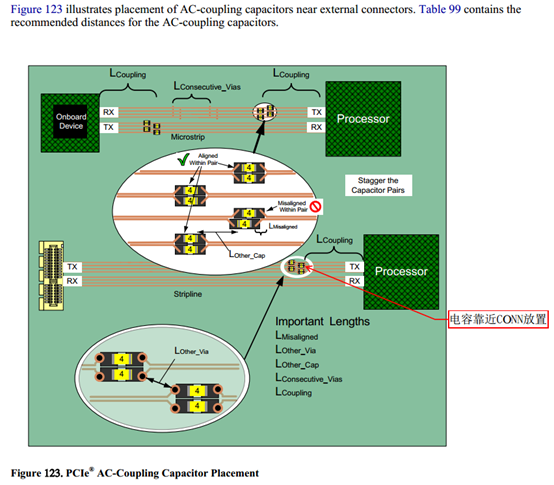

3、PCIE 放在发送端是协议规定的, 记得放在近端TX 是给detector 做充电检测device 用的。

4、有人又问了,可是为什么PCIE 是要求放发送端啊?其实仔细看PCIE 规范是说如果是两块板连接时,要发在发送的那块板上,且靠近连接器处。如果发送接收在同一块板上,那就靠近各自的接收端

最后,总结一下ac 耦合电容摆放注意事项:

1.按照design guideline 要求放置

2.没有guideline,如果是IC 到IC,请靠近接收端放置

3.如果是IC 到连接器,请靠近连接器放置

4.尽可能选择小的封装尺寸,减小阻抗不连续

5.电容的ESR ESL(特别重要)尽量小。

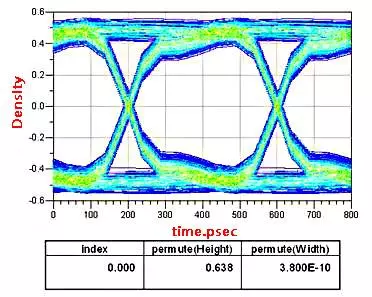

5.4 AC耦合电容摆放位置实验对比

在低速电路设计中,这颗电容可以等效成理想电容。而在高频电路中,由于寄生电感的存在以及板材造成的阻抗不连续性,实际上这颗电容不能看作是理想电容。这里信号频率2.5G,通道长度4000mil,AC耦合电容的位置分别在距离发送端和接收端200mil的位置。我们看一下仿真出的眼图的变化。

图1:AC耦合电容靠近发送端的眼图

图2:AC耦合电容靠近接收端的眼图

显然,这颗AC耦合电容靠近接收端的时候信号的完整性要好于放在发送端。我的理解是这样的,非理想电容器阻抗不连续,信号经过通道衰减后反射的能量会小于直接反射的能量,所以绝大多数串行链路要求这颗AC耦合电容放在接收端。但也有例外,笔者之前做板对板连接时遇到过这个问题,查PCIE规范发现如果是两个板通常放置在发送端上,此时还利用到了AC耦合电容的另外一个作用——过压保护。比如说SATA,所以通常要求靠近连接器放置。

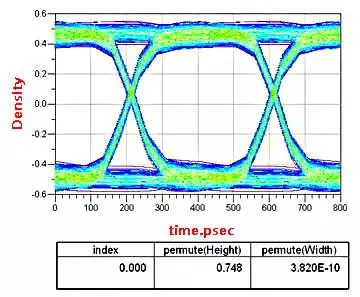

解决了放置的问题,另一个困扰大家的就是容值的选取了。这样说,我们的整个串行链路等效出的电阻R是固定的,那么AC耦合电容C的选取将会关系到时间常数(RC),RC越大,过的直流分量越大,直流压降越低。既然这样,AC耦合电容可以无限增大吗?显然是不行的。

图3:AC耦合电容增大后测量到的眼图

同样的位置,与图2相比可以看出增大耦合电容后,眼高变低。原因是“高速”使电容变的不理想。感应电感会产生串联谐振,容值越大,谐振频率越低,AC耦合电容在低频情况下呈感性,因此高频分量衰减增大,眼高变小,上升沿变缓,相应的JITTER也会增大。通常建议AC耦合电容在0.01uf~0.2uf之间,项目中0.1uf比较常见。推荐使用0402的封装

第六章:PCB上AC耦合电容的优化设计

再从PCB设计上分析一下这颗电容的优化设计。实际在项目中,与AC耦合电容的位置、容值大小这些可见因素相比,更加难以捉摸的是板材本身(包括焊盘的精度、铜箔的均匀度等)以及焊盘处的寄生电容对信号完整性的影响。我们知道,高频信号必须沿着有均匀特征阻抗的路径传播,如果遇到阻抗失配或者不连续的情况时,部分信号会被反射回发射端,造成信号的衰减,影响信号的完整性。项目中,这种情况通常会出现在焊盘或者是板载连接器处。

解决这个问题要从两个方面入手。

(1)首先在板材的选取上,我们在应用中通常选用高性能的ROGERS板材,罗杰斯的板材在铜箔厚度的控制上非常精确,均匀的铜箔覆盖大大降低了阻抗的不连续性。

(2)镂空处理:然后在消除焊盘处的寄生电容上,业内常见的办法是在焊盘处做隔层处理(挖空位于焊盘正下方的参考平面区域,在内层创建铜填充),通过增大焊盘与其参考平面(或者是返回路径)之间的距离,减小电容的不连续性。原理是:电容的PAD较走线宽,阻抗小,增加参考平面距离,增大阻抗使阻抗匹配。

6.1隔层处理前后实验对比

通过仿真对比一下ROGERS板材做精确隔层处理前后的信号完整性。

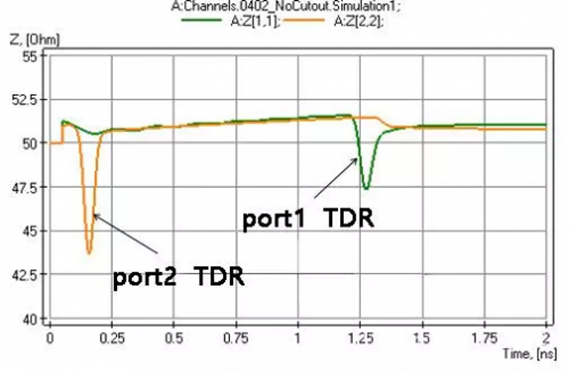

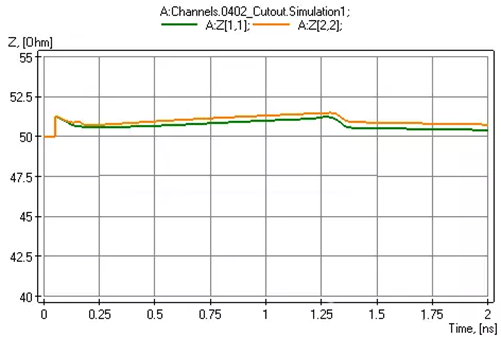

图6-1:做隔层处理前的TDR

图6-2:做隔层处理后的TDR

图6-1图6-2对比,发现未处理之前阻抗的跳跃很明显,隔层处理后的阻抗改善很多,几乎没有任何阶跃与不连续。

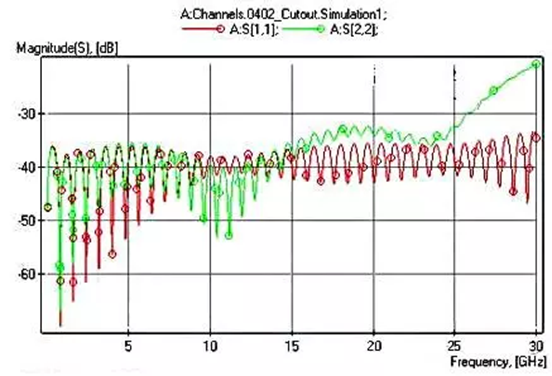

图6-3:做隔层处理前的回波损耗

图6-4:做隔层处理后的回波损耗

图6-3图6-4对比,在用ROGERS板材做隔层处理之后,相比未做隔层处理回波损耗下降到-30dB之内,大大降低了回波损耗,保证了信号传输的完整。

我的

第七章:AC耦合电容的选择

6.1通用建议:

(1) USB3.0:100Nf

(2) DP/ HDMI:AC耦合电容值范围75—200nF,建议100nF;

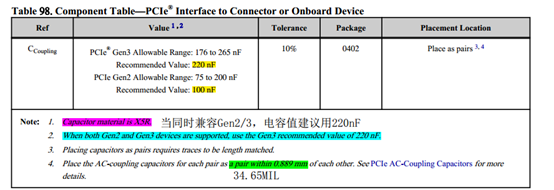

(3) PCIE Gen2: AC耦合电容值范围75—200nF,建议100nF;

(4) PCIE Gen3:AC耦合电容值范围176—265nF,建议220nF;

(5) SATA:10nF

6.2 理论计算:

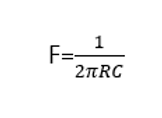

首先要看电容的频率、温度等特性并且选择低ESR/ESL的电容。对于电容值的选择是要通过计算来选的,如下所示:

这里的F是截止频率(定义电压为输入电压的0.707倍时的频率),R是传输线的阻抗,C是AC耦合电容。

当然在选择电容时,其通带的最小频率要比传输信号的最小频率要小才好,假设信号的最小频率为Fmin,则频率值为F:

F=Fmin/20

当取值为F时,99.88%的信号均会通过。

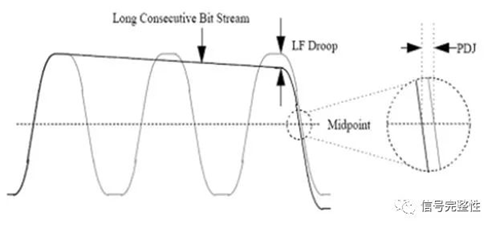

前面介绍了,虽然AC耦合电容有其好处,也会导致边沿变缓慢,放置AC耦合电容时,会引起阻抗的变化,就存在一个阻抗不连续点。同时,也会引入码型相关抖动,即当电路传输的信号中出现连续的“1”或“0”时,会出现下图所示的直流电平压降,这就会影响眼高。

如何才能减小这个直流压降降低呢?

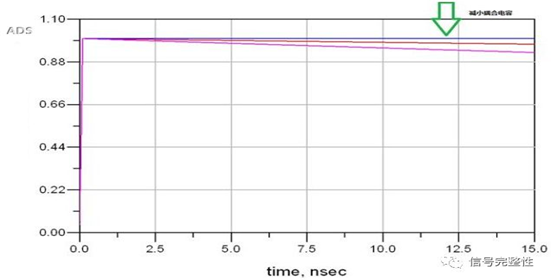

这和RC时间常数有关,RC值越大(充电时间越长,单位时间电容充电少,分压小),能通过的直流分量就越多直流压降越小。由于链路中等效电阻是相对固定的,只能调节耦合电容值了。如下图所示电容值越大,压降越小。

紫色的电容值最大,红色的电容值次之,粉色的电容值最小。

那我们就把电容无限加大吧!

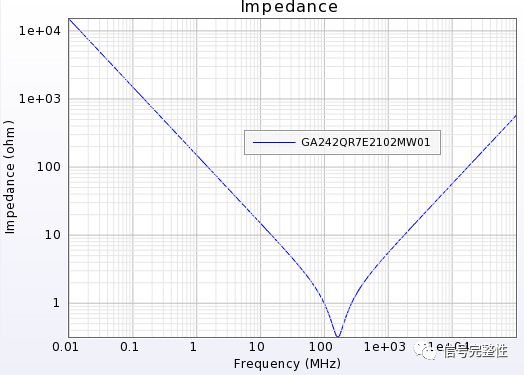

答案是:No,不行!因为,实际安装后的电容不是理想电容,除了ESR,ESL,还有安装电感,所以就存在一个串联谐振频率。电容在串联谐振频率之前呈容性,之后呈感性。如下图所示:

电容值越大,谐振频率越小,电容在较低频率就会呈现感性,这样会造成信号高频分量衰减增大,同样会使眼高减小,上升沿变缓,jitter增加。

所以选择AC耦合电容时要综合以上两点考量,一般业界都推荐0.01uF~0.2uF,最常见的就是0.1uF的电容。对于电容封装的选择不建议使用大于0603的封装,最好是0402的,或者更小。