在实际的项目工程中,基本上都是在Modelsim进行功能仿真后,直接进行板级调试(用signaltap调试),但是中规中矩的后仿真也不能不会。操作步骤如下:

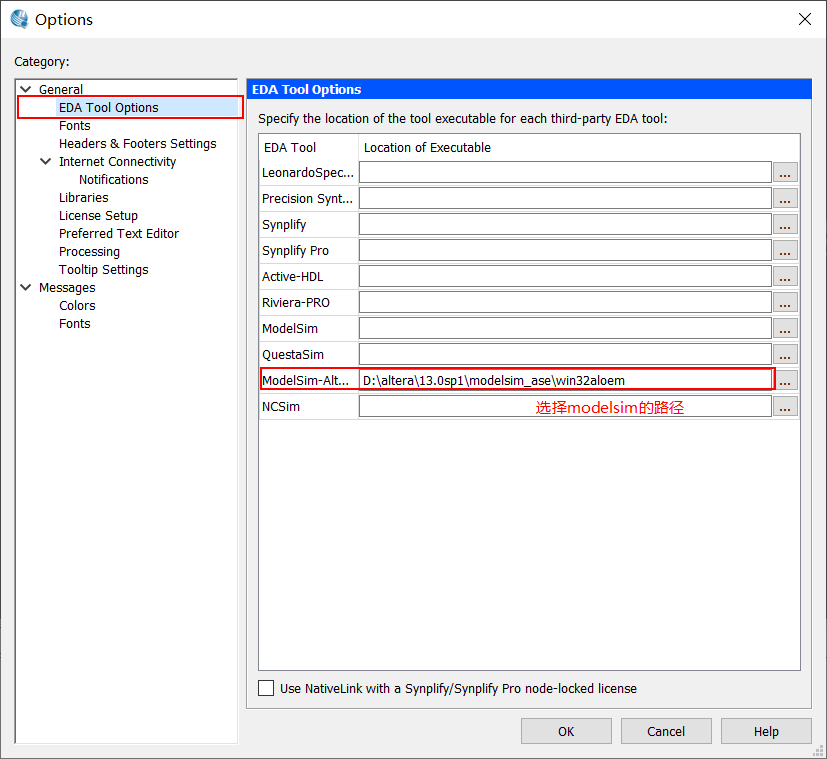

1.将quartus II与其自带的Modelsim-Altera进行关联,quartus II软件中【Tools】--->【Options】,按图1进行操作

图1

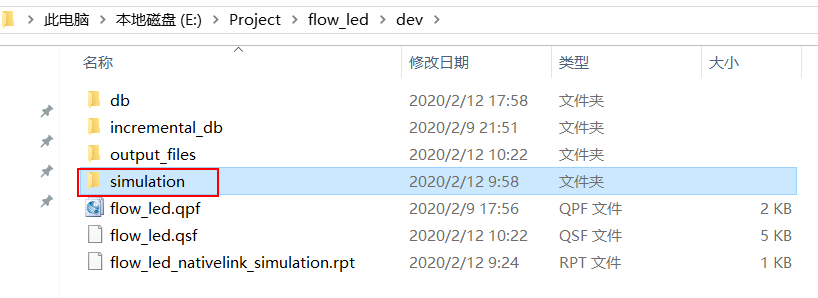

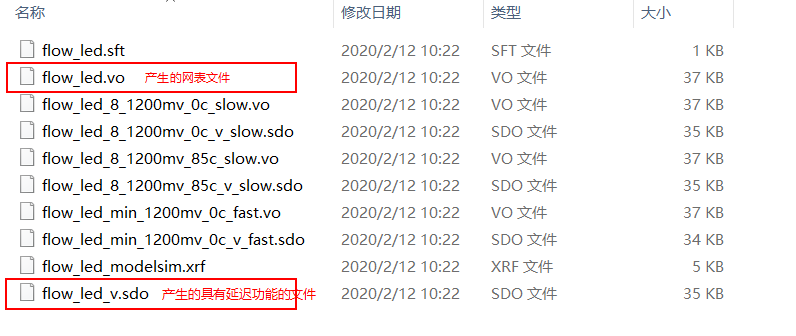

2.在quartus II软件中进行全编译,这时会在工程文件夹产生“simulation”文件夹,打开并接着打开“modelsim文件夹”,这时里面会出现10个文件,其中“.vo”和“.sdo”是时序仿真需要的文件,将他们粘贴到modelsim的工程文件夹中。

图2

图3

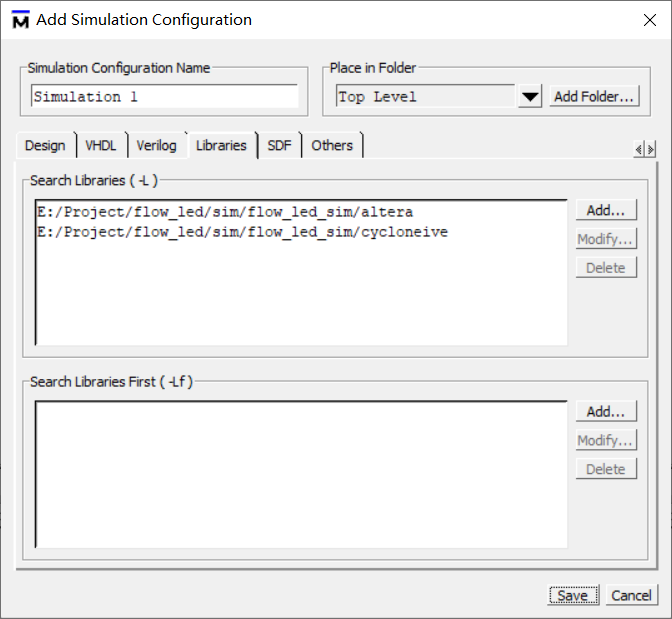

3.接下来还需要Altera的器件库

其中Altera的器件库文件在:D:altera13.0sp1modelsim_asealteraverilogaltera

D:altera13.0sp1modelsim_asealteraverilogcycloneive

图4

4.将testbench文件和“.vo”文件加到工程上,然后编译,然后右键选择【Add to project】-->【Simulation Configuration】,选择【Work】中的"xxx_tb"文件,然后选择【Libraries】中加载刚在粘贴的2个Altera器件库,然后在【SDF】中加载刚才粘贴的“xx.sdo”文件,然后点【Save】,最后点击“Simulation”即可进行时序仿真。如图5 、6、7所示:

图5

图6

图7