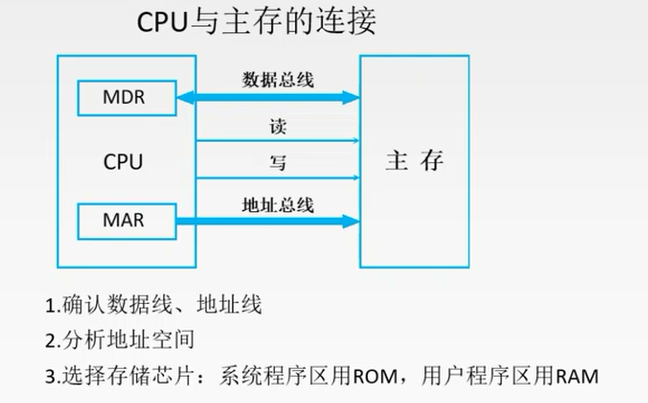

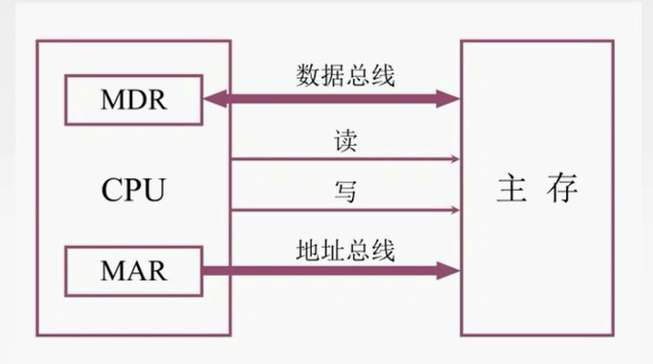

主存储器与CPU的连接

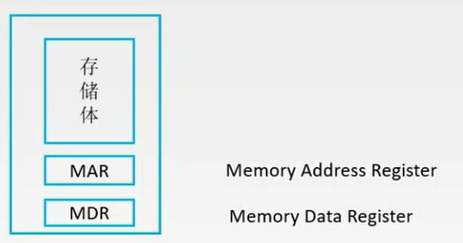

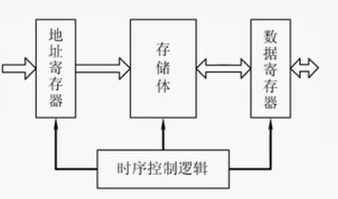

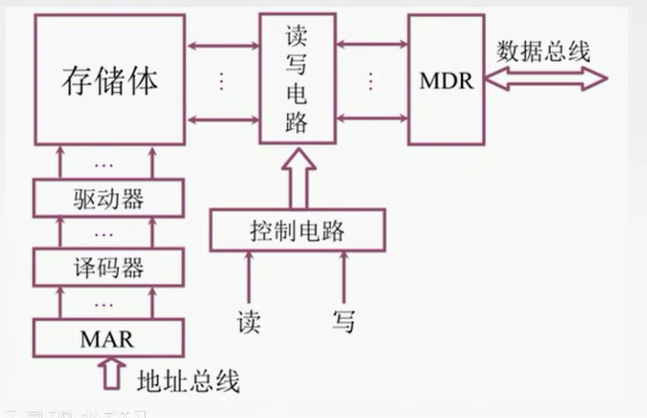

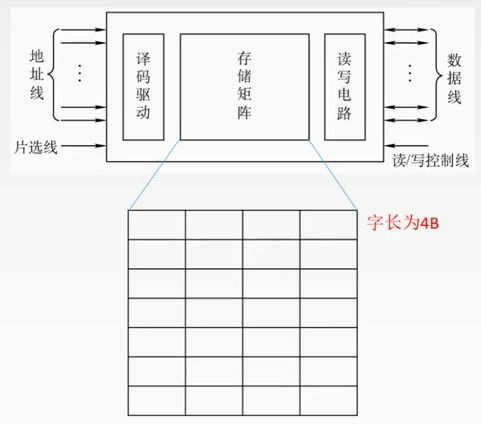

主存储器(简化结构)

主存简单模型

连接原理

3类

数据总线、地址总线、控制总线

从存储器中读出一个信息字:

- 首先CPU把这个信息字的地址送到MAR

- 然后经过地址总线到主存

- 在通过控制总线发出读命令

- 主存接到读命令后,就知道把这个地址的数据读出

- 根据CPU决定将数据送到哪,通过数据总线

写一个数据到主存:

- CPU要把信息字所在的主存单元的地址经过MAR送到地址总线

- 然后在把这个信息字送到MDR

- 然后向主存发送一个写命令

- 主存收到写命令后

- 把数据总线上的信息写到相应地址线指出的储存单元中

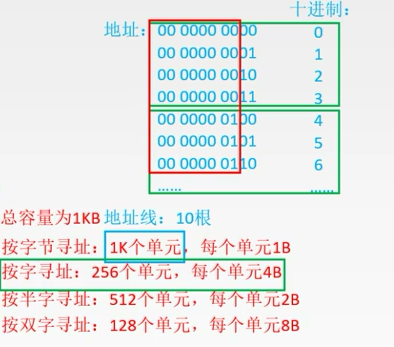

主存地址单元分配(比较重要)

主存地址分配

总容量1KB

按字节寻址:1K个单元,每个单元1B,1K=1024,十根地址线

按字寻址:256个单元,每个单元4B,高位看成组号,后面跟两位

按半子寻址:512个单元,每个单元2B

按双字寻址:128个单元,每个单元8B

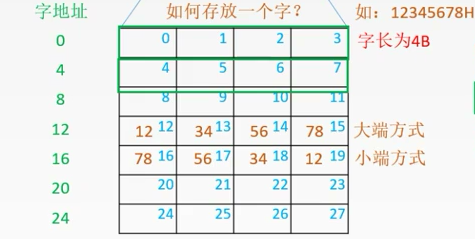

如何存放一个字?如12345678H

大端方式:高位字(12)节作为字地址

小端方式:低位字(78)节做为字地址

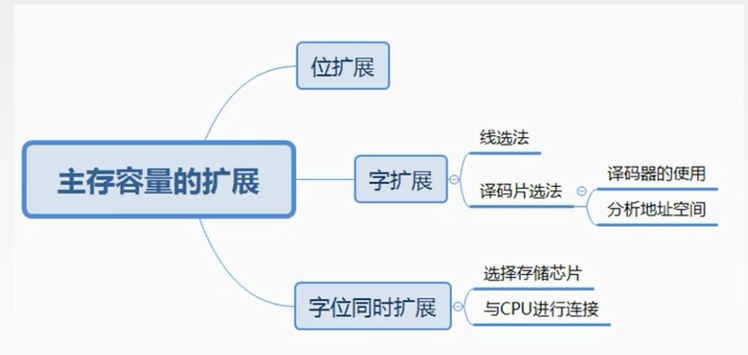

主存储容量的扩展

由于单个芯片的容量总是有限的。

需要在字和位两个方面扩充。

位扩展法,字扩展法,字位扩展法。

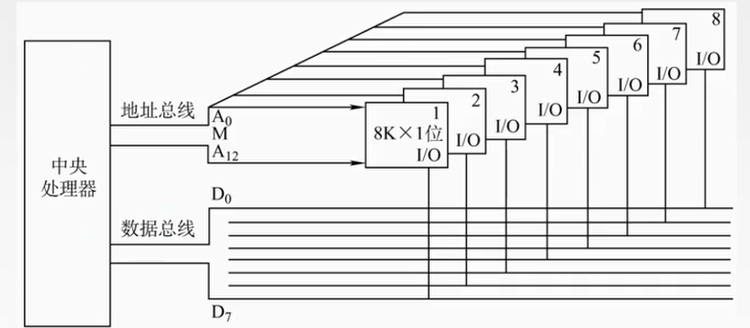

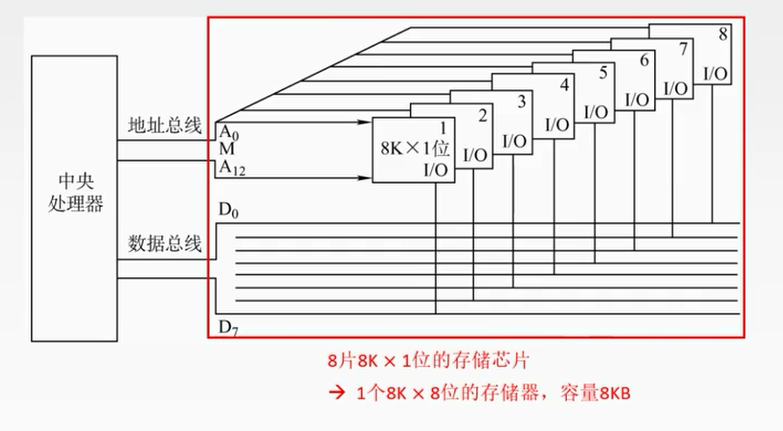

位扩展

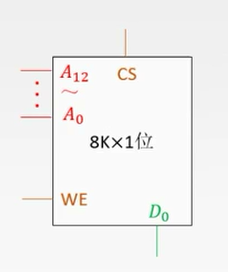

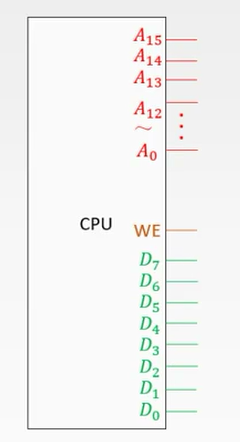

这个是8K*1位,即13根地址线和1位数据线。

CPU要求:8位的数据线,16位的地址线

如何进行连接?

CS是高电平有效,所以要选择到他要给个1

这样显然是不够的,cpu有8位的数据线,而存储芯片只有1位,不满足存储容量的要求。

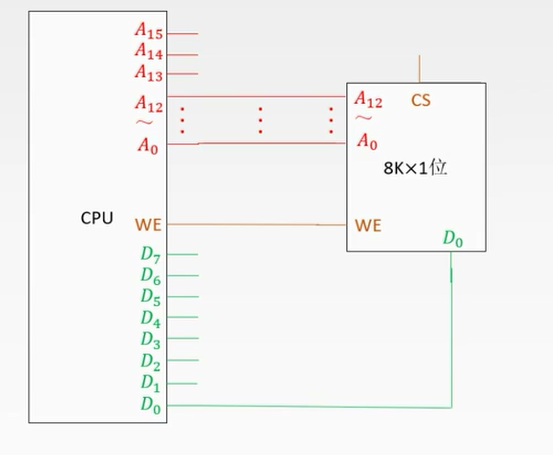

在加一块芯片

8块芯片进行扩展

相当于并联在一起。

一个8K*8位的存储器。

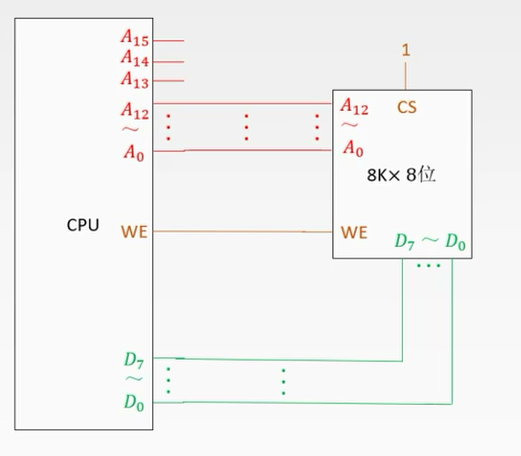

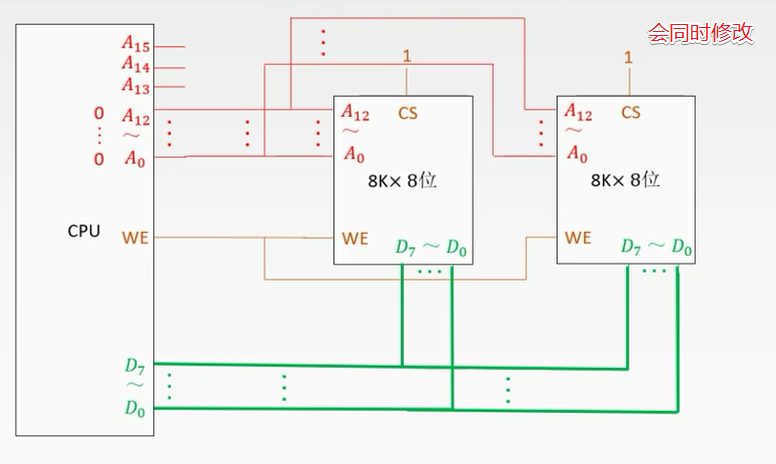

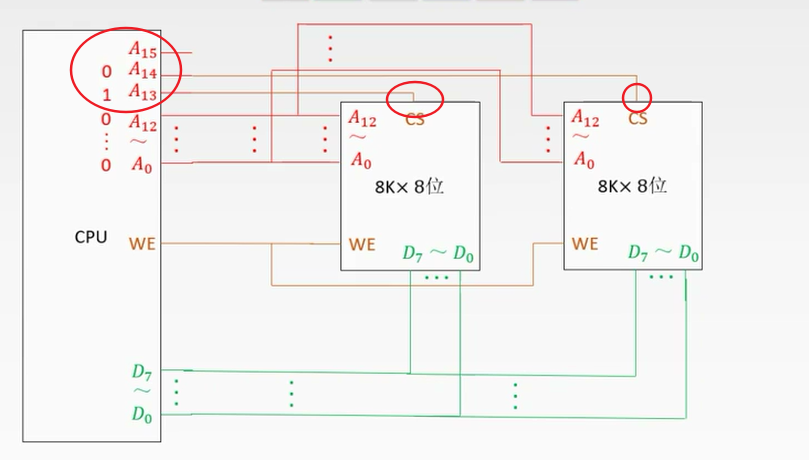

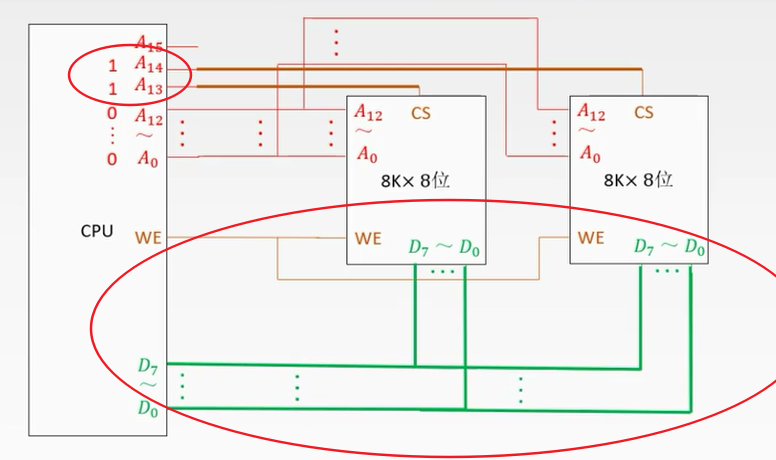

字扩展

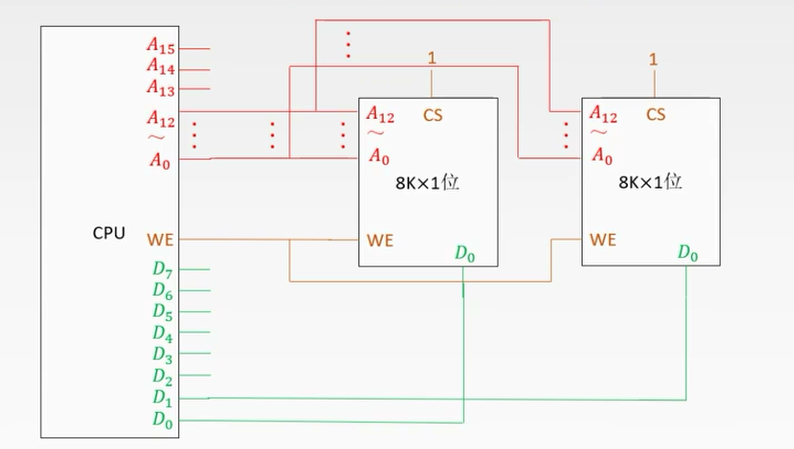

存储芯片是8K*8位的,CPU也是8位的数据线

会不知道哪一个数据

使用片选线来进行控制。

但是还是会遇到同样的问题,如果是11的话,两个的数据都会被操作了。

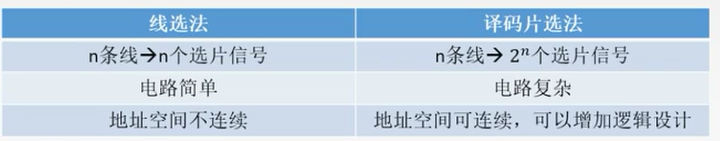

线选法:A14 A13只能为01或10,n条线->n个选片信号

地址:01x xxxx xxxx xxxx、10x xxxx xxxx xxxx

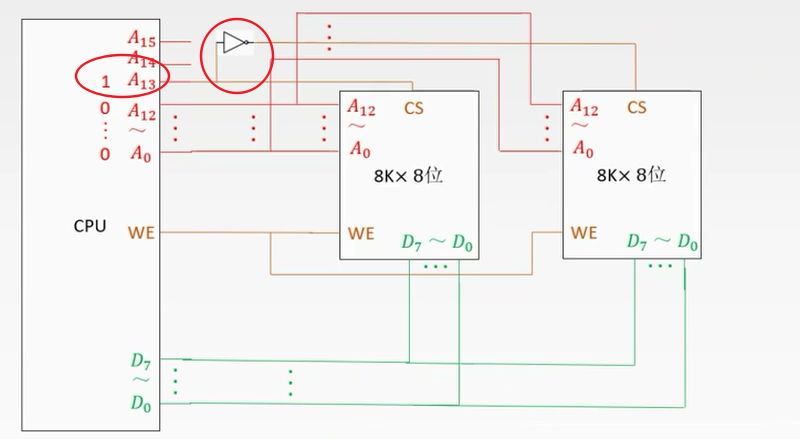

改进:用一个非门

地址1x xxxx xxxx xxxx、0x xxxx xxxx xxxx

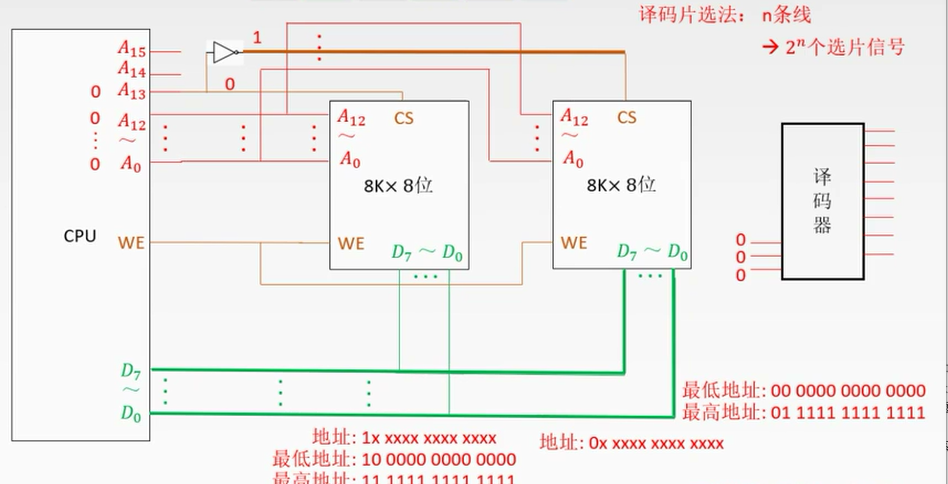

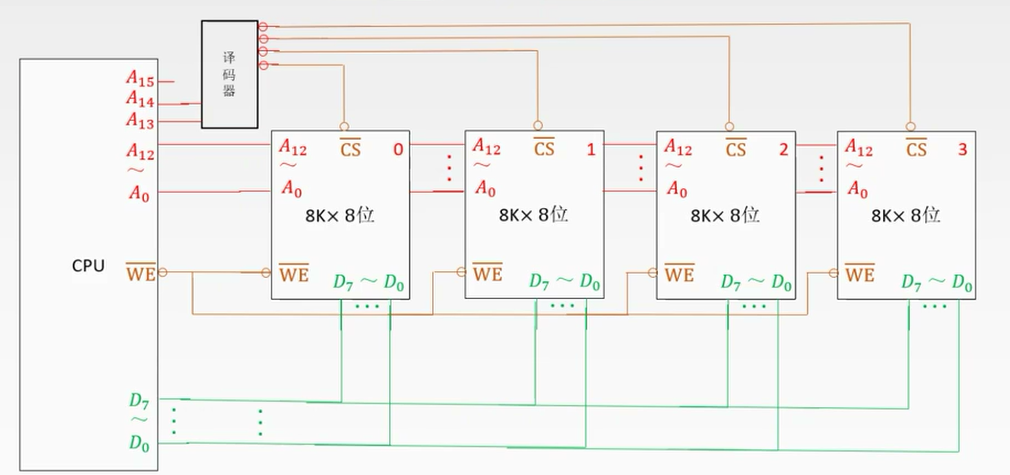

译码片选法:n条线->2^n个选片信号

译码器。

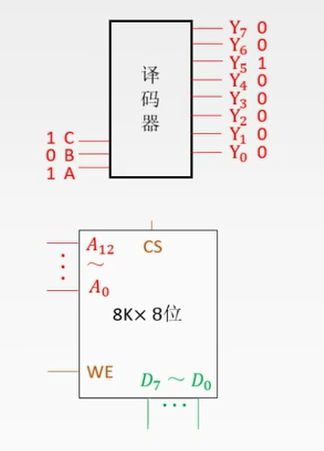

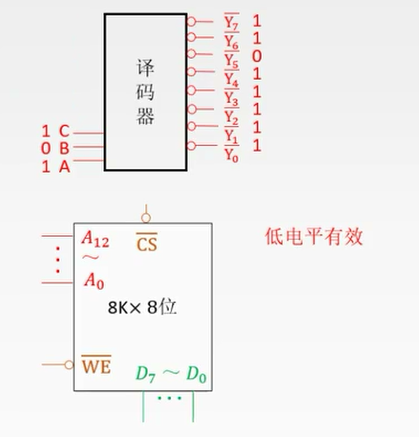

译码器

高电平有效,1

低电平有效,0

3位地址选8块芯片。

注意圈圈。

使能端,EN,还有可能有多个使能端。使译码器工作。

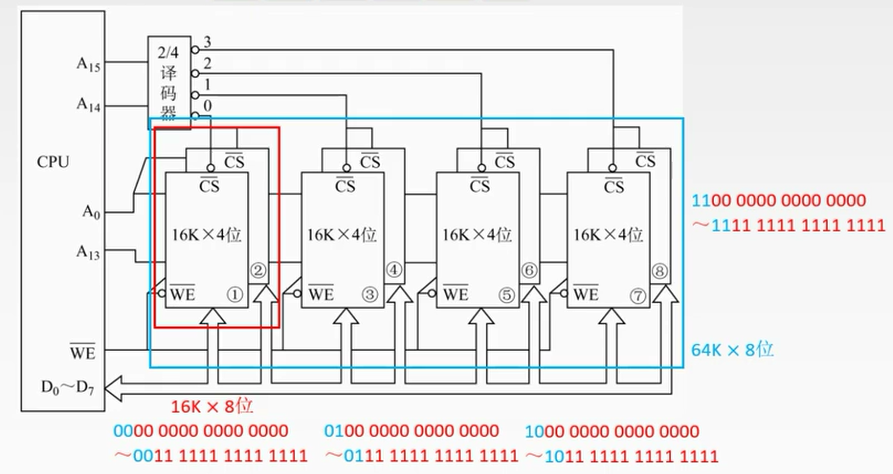

将译码器利用到字扩展

00,01,10,11

对比

字位同时拓展

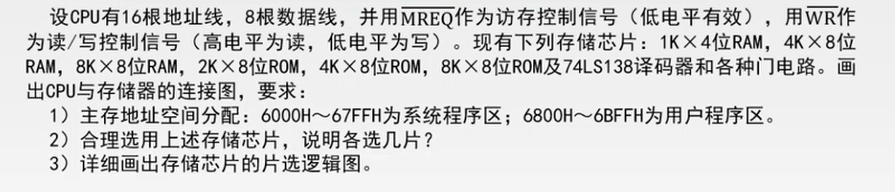

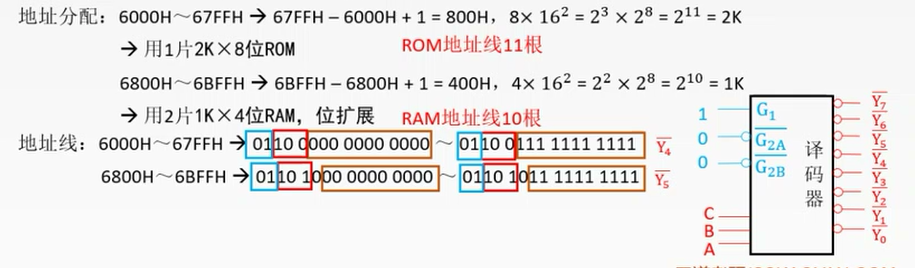

例题

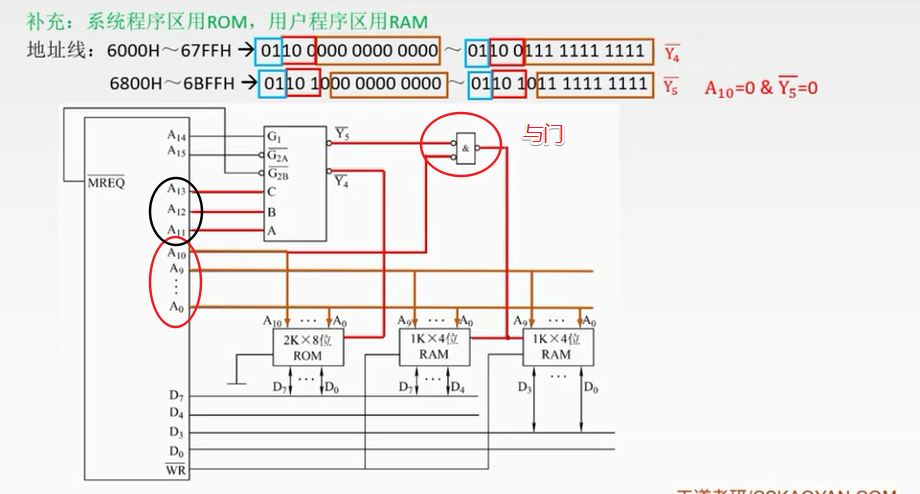

系统程序区用ROM,用户程序区用RAM

1.确认地址线、数据线、选择存储芯片

数据线:CPU数据线8根 -> 存储器位数应扩展为8位

回顾