前言

最近群内同学问到:啥是阻塞,啥是非阻塞。实际电路中有这玩意儿吗?

个人觉得阻塞非阻塞是仿真电路下的描述,实际电路中是没有这个描述的。

实际的电路中只有组合逻辑和时序逻辑,不可能存在谁阻塞了谁。只是仿真中需要特别注意。

按照书上的描述:阻塞相当于软件中的顺序执行,非阻塞相当于并发执行。

类比为阻塞就是一个人干活,如果一条语句为一个活,那么先干前面的活再干后面的活。非阻塞就是多个人一起干活,每一条语句都是一个人在干活,则为并发。

流程

以下对几种情况进行了相应的测试。

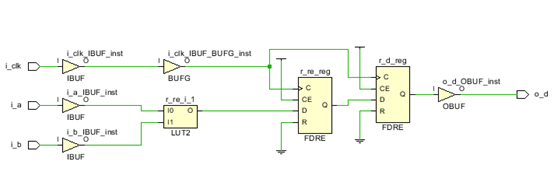

(1)时序逻辑使用非阻塞。(业界正确用法)

推断结果:

综合结果:

对于上述逻辑,相当于多打了一拍。

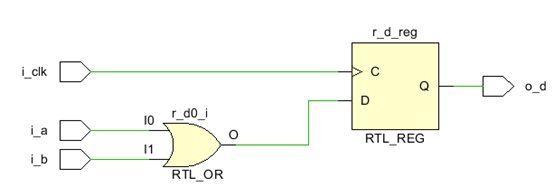

(2)时序逻辑使用阻塞。

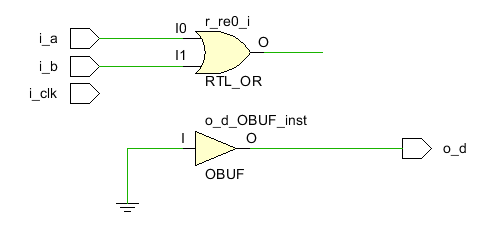

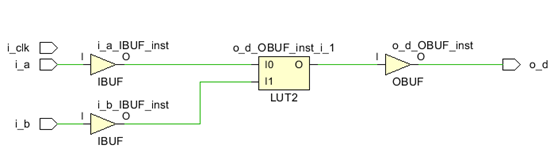

推断结果:

综合结果:

可以看到,中间逻辑被打平,优化掉了。

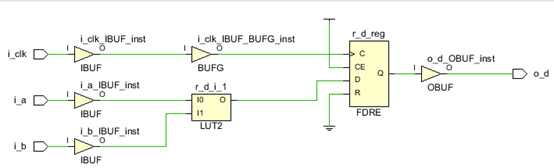

(3)组合逻辑使用非阻塞。

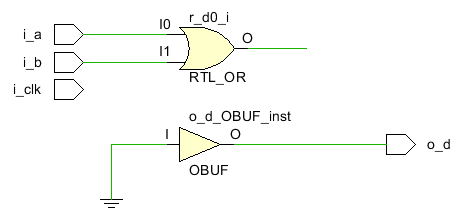

推断结果:

综合结果:

可以看到,推断的结果可能跟实际上是不一致的,代码中置了初始值,当然对实际组合电路没啥卵用,只是仿真中指定固定态而已,只供参考,实际以综合后结果为准。可以看到就是个或门的LUT。

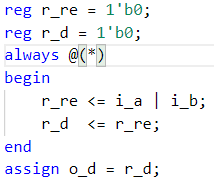

(4)组合逻辑使用阻塞。(业界正确用法)

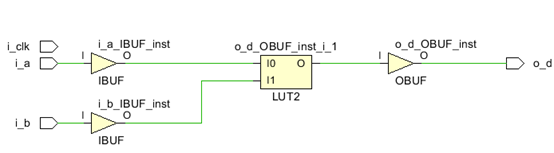

推断结果:

综合结果:

可以看到,推断的结果可能跟实际上是不一致的,只供参考,实际以综合后结果为准。可以看到就是个或门的LUT。

结论

所以,根据实际测试结果来看,时序逻辑使用阻塞,会导致中间态被优化。组合逻辑用啥都无所谓。本句话仅表示实际电路,不代表仿真如此。

vivado的推断阔能是不正确的,以综合结果为准。

写代码遵循业界规则,否则可能给自己埋坑。

写代码只需记住:时序逻辑就是数据流。组合逻辑就是物理连线。世界豁然开朗。

写综合代码只需遵循:

(1)组合逻辑用阻塞赋值。

(2)时序逻辑用非阻塞赋值。

(3)不要在一个块语句中混用阻塞非阻塞。

以上。