前言

实际开发过程中,可能会使用到一些函数,如果在不同子模块中重复定义,则会导致代码冗余。

而使用SV语法则可以把函数定义在包中,包是单独的一个文件,子模块只需要include这个文件即可使用函数。

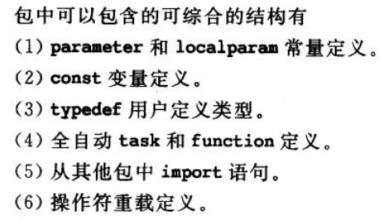

而包中可以包含哪些定义?

流程

以下操作需要两个文件:definition.sv 和 demo_sv.sv文件

(1)definition文件内容:包含位宽计算函数clogb2

`ifndef DFFS_DONE

`define DFFS_DONE

package p_demo;

function integer clogb2 (input integer depth);

begin

for (clogb2=0; depth>0; clogb2=clogb2+1)

depth = depth >>1;

end

endfunction

endpackage

import p_demo::*;

`endif

`include "definitions.sv"

module demo_sv (

input logic i_clk,

output logic l_b

);

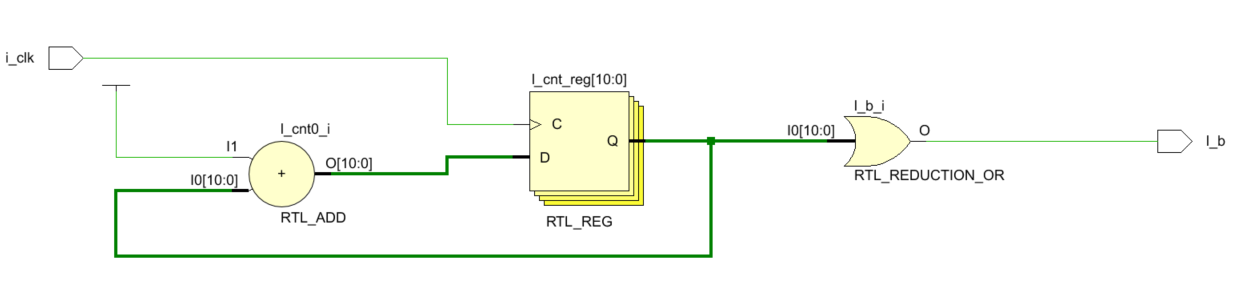

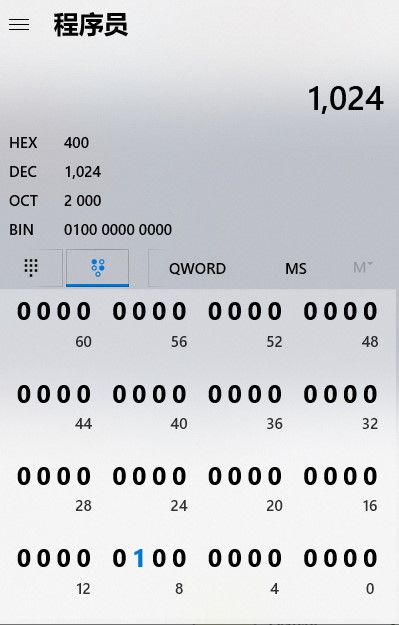

logic [clogb2(1024)-1:0] l_cnt = '0;

always_ff @(posedge i_clk)

begin

l_cnt <= l_cnt + 'd1;

end

assign l_b = | l_cnt;

endmodule:demo_sv

(4)在包中可以定义parameter等,使用跟verilog类似。

`ifndef DFFS_DONE

`define DFFS_DONE

package p_demo;

localparam p_width = 4;

endpackage

import p_demo::*;

`endif

`include "definitions.sv"

module demo_sv (

input logic i_clk,

output logic l_b

);

logic [p_width-1:0] l_cnt = '0;

always_ff @(posedge i_clk)

begin

l_cnt <= l_cnt + 'd1;

end

assign l_b = | l_cnt;

endmodule:demo_sv

以上。