首先写一个自己的库:

- #include "../MyAPI.h"

- #include <cstdlib>

- #include <ctime>

- int getRandom(int boundary)

- {

- if (boundary <= 0 )

- {

- return 0;

- }

- srand((unsigned)time(NULL));

- return rand() % boundary;

- }

这里的MyAPI.h是库对应的头文件(这里用../MyAPI.h是因为库文件源代码在lib目录下,而头文件跟lib目录在同级目录):

- int getRandom(int boundary);

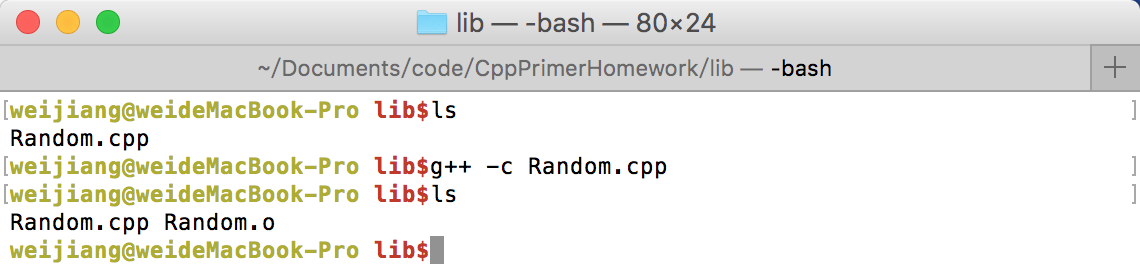

2. 接着要编译这个库,在这之前需要将源文件编译成.o文件:

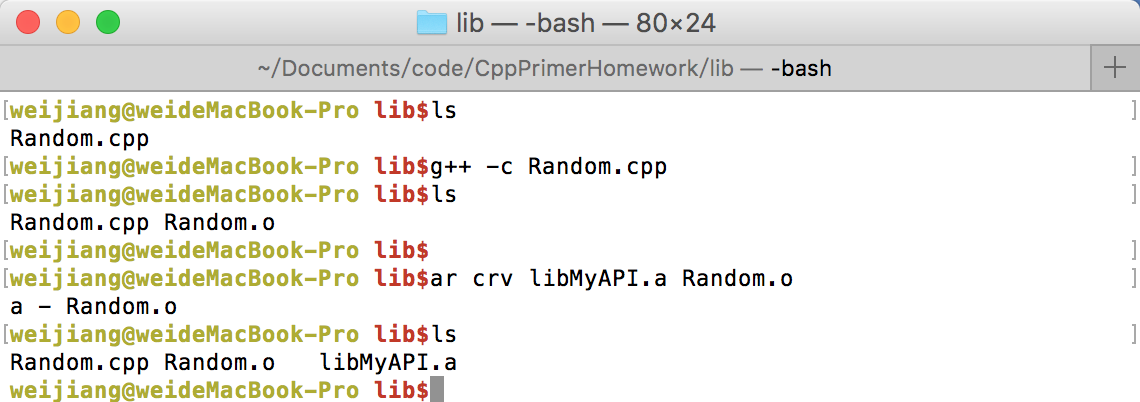

3. 之后再将.o文件打包成lib,在类Unix系统中,静态库是.a文件:

4. 之后就是使用这个lib库了,下面是使用该库的源代码:

- #include "basic.h"

- int main()

- {

- cout << getRandom(20) << endl;

- }

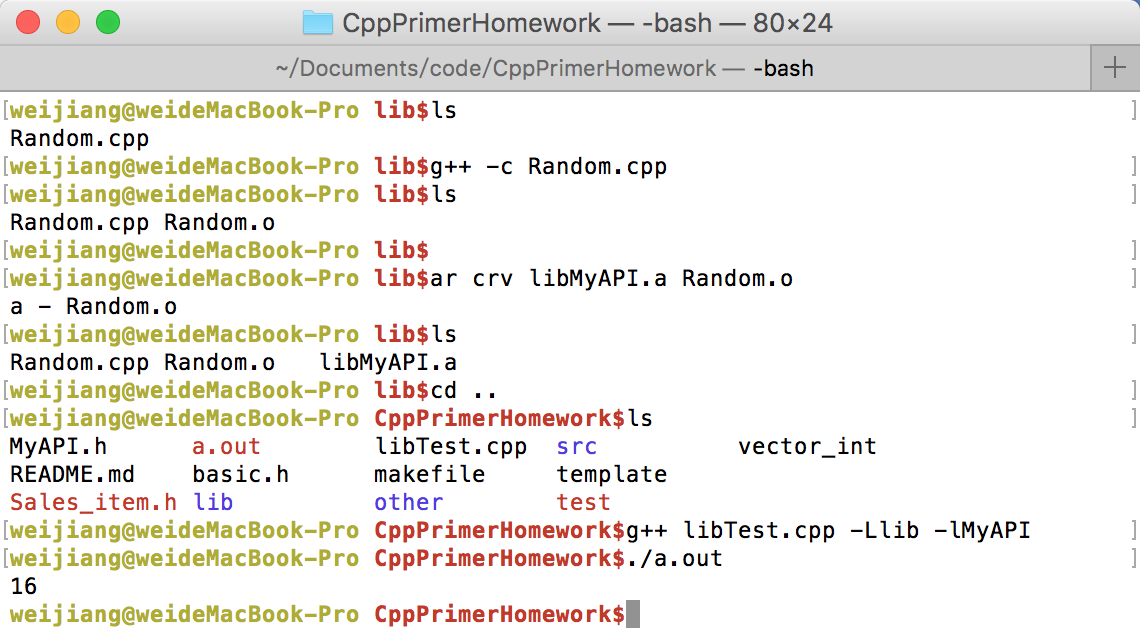

5. 源代码中只需要包含头文件就可以了,重点在于编译的时候,下面是编译命令:

这里需要注意两点:

1) -L参数指定包含lib的目录;-l指定lib名;

2)lib名也需要注意,名称是libMyAPI.a,但是使用时不需要加lib和.a后缀。

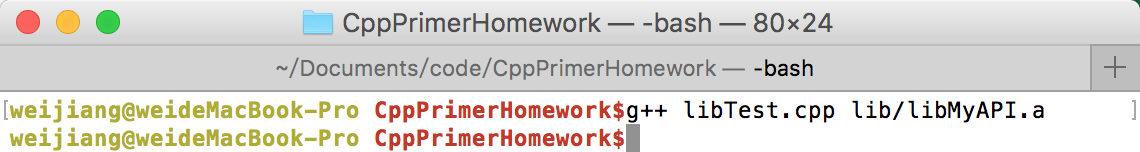

当然也可以不使用-L -l等选项,直接使用lib全称:

之后生成的a.out就可以使用了。

这里之所以提到-L和-l参数,原因是在写makefile时,-L和-l会带来更多的便利。

以上是一个简单的例子。

也可以写一个makefile文件来做这个,下面是一个makefile的例子:

- #####################################################################

- ## file : test makefile for build current dir .cpp ##

- ## author : ##

- ## date-time : ##

- #####################################################################

- CC = gcc

- CPP = g++

- RM = rm -rf

- ## debug flag

- DBG_ENABLE = 1

- ## source file path

- SRC_PATH := .

- ## target exec file name

- TARGET := test

- ## get all source files

- SRCS += $(wildcard $(SRC_PATH)/*.cpp)

- ## all .o based on all .c

- OBJS := $(SRCS:.cpp=.o)

- ## need libs, add at here

- LIBS := MyApi

- ## used headers file path

- INCLUDE_PATH := .

- ## used include librarys file path

- LIBRARY_PATH := lib

- ## debug for debug info, when use gdb to debug

- ifeq (1, ${DBG_ENABLE})

- CFLAGS += -D_DEBUG -O0 -g -DDEBUG=1

- endif

- ## get all include path

- CFLAGS += $(foreach dir, $(INCLUDE_PATH), -I$(dir))

- ## get all library path

- LDFLAGS += $(foreach lib, $(LIBRARY_PATH), -L$(lib))

- ## get all librarys

- LDFLAGS += $(foreach lib, $(LIBS), -l$(lib))

- ## c++11 support

- CFLAGS += -std=c++11

- all: build

- build:

- $(CPP) -c $(CFLAGS) $(SRCS)

- $(CPP) $(CFLAGS) -o $(TARGET) $(OBJS) $(LDFLAGS)

- $(RM) $(OBJS)

- clean:

- $(RM) $(OBJS) $(TARGET)

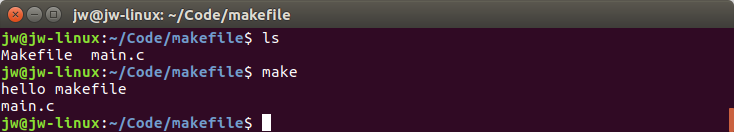

运行make命令之后,make程序会在当前目前下寻找Makefile文件,根据Makefile文件中的内容执行具体的操作。

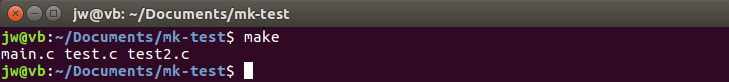

执行make命令后的结果如下:

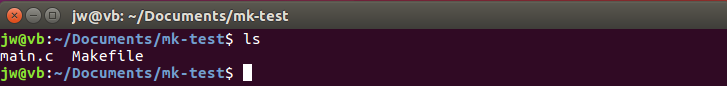

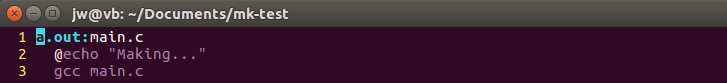

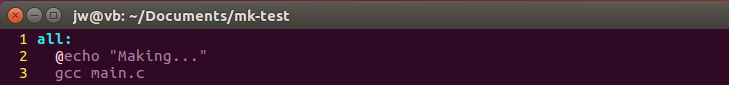

Makefile的基础是如下的部分:

- targets:prerequisites

- commands

a.out是targets,目标;

main.c是prerequisites,依赖;

剩余的部分开头是一个TAB,他们是命令;

make执行命令的条件是依赖比目标要新。

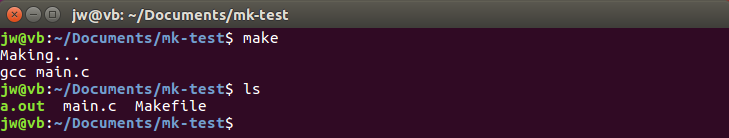

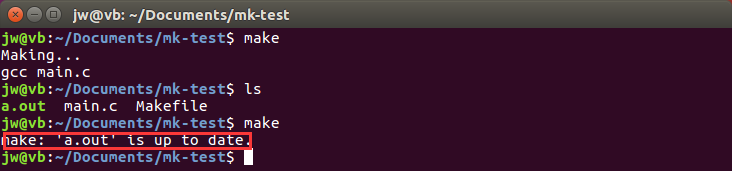

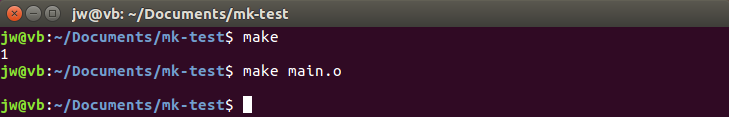

如果在上例执行后再运行make,结果如下:

这是因为main.c没有修改过,它比a.out要旧。

需要注意,目标和依赖都可以是多个,而只要任意依赖新于目标,都会导致命令重新执行。

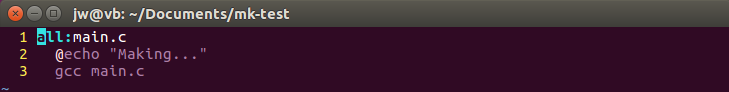

以上示例中,目标是一个文件,但是它还可以是其它的。比如一个标签:

all就是一个标签。

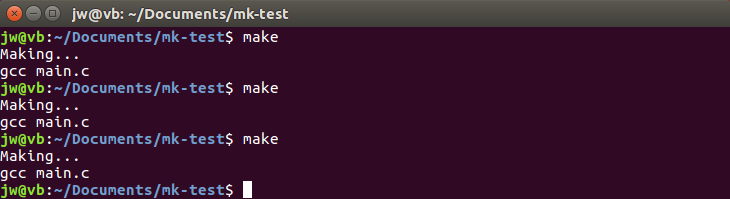

标签永远比依赖要旧,即其下的命令一直会执行:

甚至可以没有依赖:

all对应命令也会一直执行。

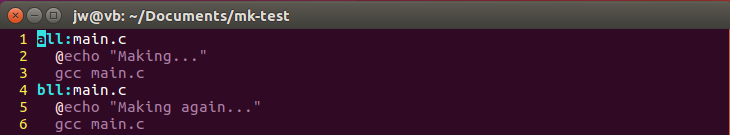

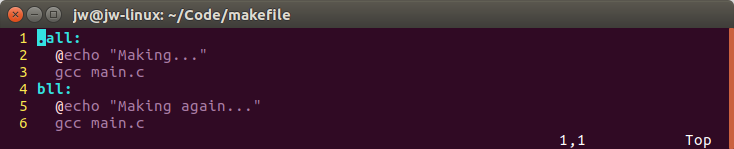

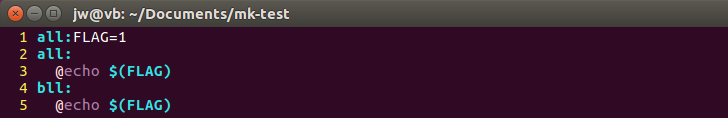

标签可以有多个,但是它并不是顺序执行,make只会执行第一个遇到的标签。如下面的Makefile文件:

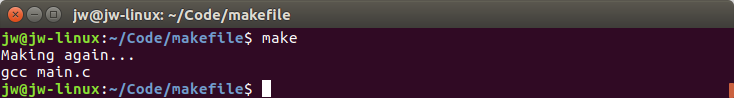

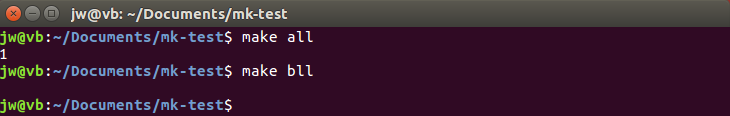

执行make的结果如下:

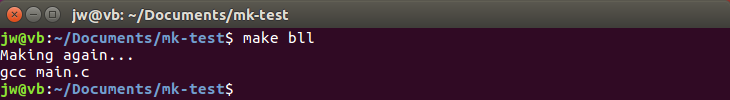

可以看到只有all标签会被执行。如果要执行bll,就需要显式地指定:

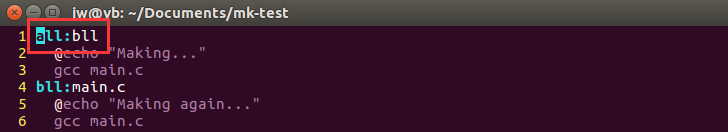

标签之间可以互相依赖:

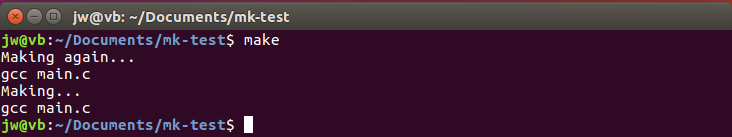

执行的结果如下:

因为all依赖于bll,而bll又依赖于main.c,因此这里的执行顺序就是先执行bll对应的命令,然后再执行all对应的命令。

还有一种情况,如果在标签之前加上“.”,则make的时候会跳过它,即使它是第一个遇到的标签:

make执行结果如下:

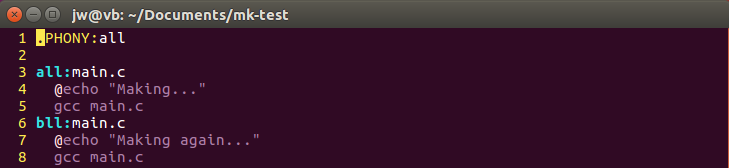

标签在Makefile文件中又称为伪目标,不应该与真正的目标文件具有相同的名字,而为了避免这种情况,Makefile提供了一个关键字.PHONY,用于声明伪目标。

像下面这个样子:

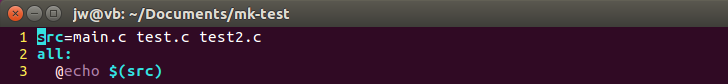

变量

Makefile文件中的变量就是一个个的字符串。

访问变量使用$(xx),其中xx是变量名。

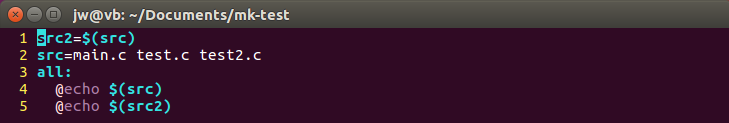

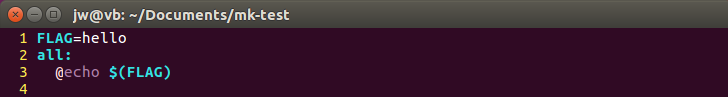

下面是一个例子:

执行的结果是:

变量的赋值可以使用普通的"=",它有一个特点,如下例所示:

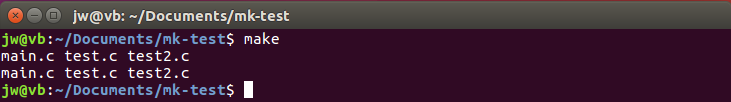

执行的结果是:

即,Makefile中使用=定义的变量可以访问到之后定义的变量。使用=得到的变量称为recursively expanded variable。

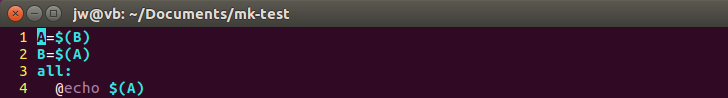

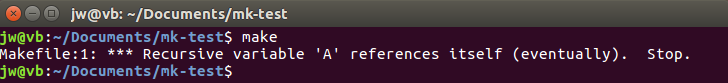

它有一个缺点就是会导致循环赋值,比如下面的例子:

为了避免这种情况,Makefile提供了另一个赋值操作符":=",称为Simply expanded variables。

它更接近于一般意义上的赋值,当:=右边引用了其它的变量,而该变量还没有定义或者要到之后才会定义,那么返回的就是空字符串。

另外的赋值操作符还有:

“+=”:这是给变量追加值。

"?=":首先判断变量是否存在,如果不存在就赋值成右边的值,如果存在了,就什么也不做。

与变量赋值相关的还有几个指示符:

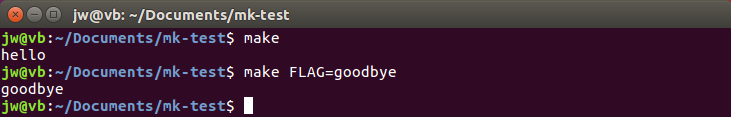

override:这个指示符出现的原因是,一般定义的变量会被make命令行中的参数覆盖,而使用了override的变量则不会。下面是一个例子:

在未使用override的情况下:

可以看到FLAG参数被make命令行中的参数替代了。

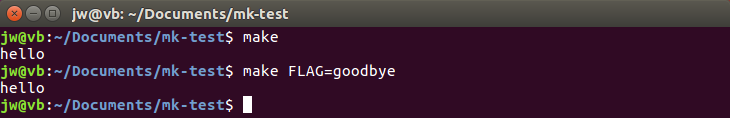

如果在定义变量的时候使用了override的话:

变量的值将不会受到make命令行参数的影响。

export:用于向下层的Makefile文件传递参数。默认情况下,只有在make命令行中的参数才会向下传递,但是使用export之后,在当前Makefile文件中定义的变量也会向下传递了。

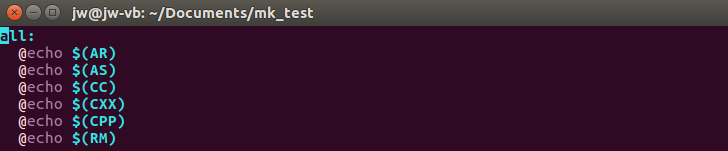

Makefile中还存在几类特殊的变量:

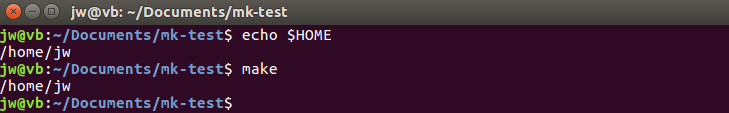

系统环境变量:make执行时会引入部分的环境变量,它们在Makefile中可以访问:

从结果可以看到Makefile中可以识别HOME这个系统环境变量。

需要注意的是,并不是所有的系统环境变量都可以在Makefile中使用,比如BASH就不行。具体怎么区分的,不知道。

目标变量:它是针对某一个目标存在的变量,可以算作是局部变量。它的定义如下:

- targets:xx=yy

从中可以看到FLAG只针对all存在,在bll中无法访问到。

还需要注意,FLAG不仅只在all中生效,它引发的所有的规则中FLAG都存在。

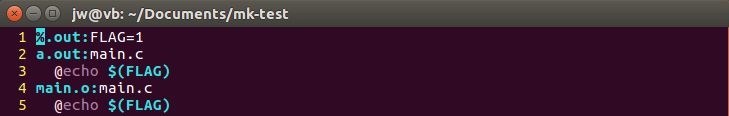

模式变量:它其实是目标变量的延伸。其中定义的变量对满足模式的所有目标都可见。下面是一个例子:

上例中的a.out满足%.out的模式,所以FLAG有效,而对于main.o就无效了。

自动化变量:它们是一组样式奇怪的变量,也属于局部变量,下面是其中的几个:

$@ :表示目标集;

$< :表示依赖中的第一个名字,如果依赖是模式的话,则表示满足模式的所有依赖;

$? :表示所有比目标新的依赖集;

$^ :表示依赖集;

$(@D) :表示$@的目录部分;(还有其它版本的,如$(<D),略)

$(@F) :表示$@的文件部分;(还有其它版本的,如$(<F),略)

自动化变量还有很多,不一一介绍了。

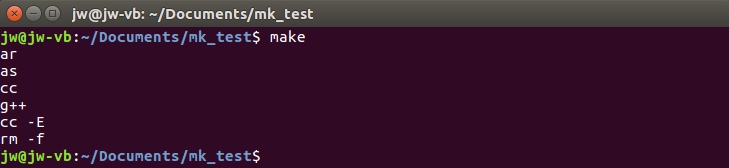

还有一个类型的变量,属于make执行时可以使用的与命令相关的变量,比如如下的:

执行的结果如下:

这类变量还有很多,这里不一一说明。

函数

函数的格式如下:

- $(<fucn><params>)

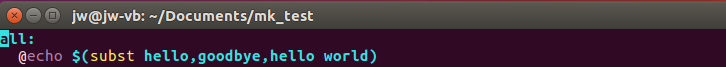

以下是一个简单的示例:

make后得到的结果是goodbye world。

Makefile中的函数将在Makefile基础——函数中详细介绍。

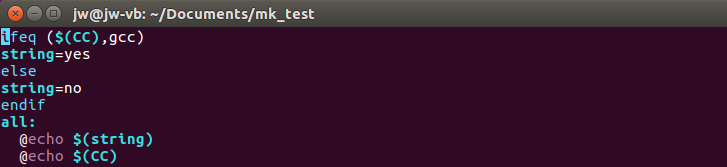

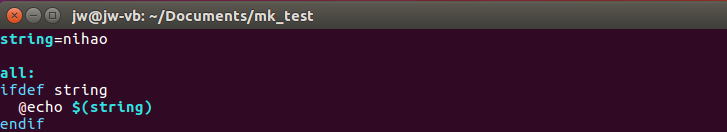

控制语句

Makefile中的控制语句有以下的一些:

- ifeq/ifneq

- else

- endif

- ifdef/ifndef

- else

- endif

函数的基础请参考Makefile基础。

字符串处理函数

- $(subst <from>,<to>,<text>)

作用:将text中的from替换成to,并返回修改后的text(当然也有可能没有被修改)。

- $(patsubst <pattern>,<replacement>,<text>)

- $(strip <string>)

- $(findstring <find>,<in>)

- $(filter <pattern...>,<text>)

- $(filter-out <pattern...>,<text>)

- $(sort <list>)

- $(word <n>,<text>)

- $(wordlist <s>,<e>,<text>)

- $(words <text>)

- $(firstword <text>)

文件名操作

- $(dir <names...>)

- $(nodir <names...>)

- $(suffix <names...>)

- $(basename <names...>)

- $(addsuffix <suffix>,<names...>)

- $(addprefix <prefix>,<names...>)

- $(join <list1>,<list2>)

- $(abspath <names...>)

结构函数

- $(foreach <var>,<list>,<text>)

- $(if <condition>,<then-part>,<else-part>)

call函数

- $(call <expression>,<param1>,<param2>...)

origin函数

- $(origin <var>)

shell函数

- $(shell <cmd>)

作用:执行cmd命令。相当于`cmd`。

eval函数

- $(eval <text>)

似乎是展开text,作为Makefile的一部分。但是为什么要这么做,为什么不直接写text,不明白。。。

告警/错误函数

- $(error <tetx>)

- $(warning <text>)

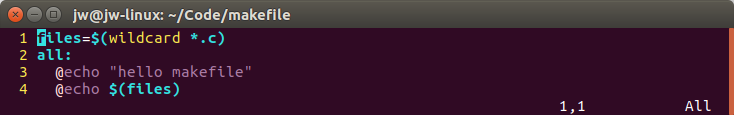

wildcard函数

- $(wildcard pattern...)

运行make之后的结果: