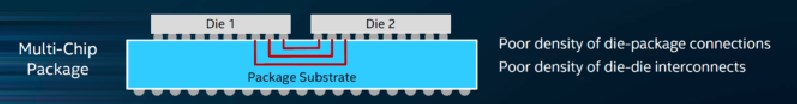

1. 传统多芯片模块封装技术

Die 2 Die的通信是通过基板电路实现的,优点是可靠,缺点是集成的密度比较低。是一种非常原始的方式。

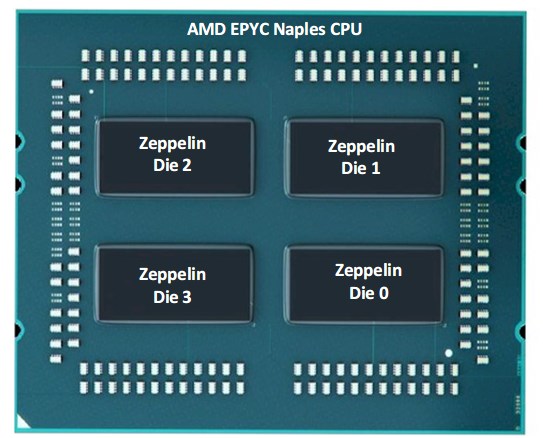

例子:amd Naples 的四个Chiplet之间的通信也是使用这种方式。

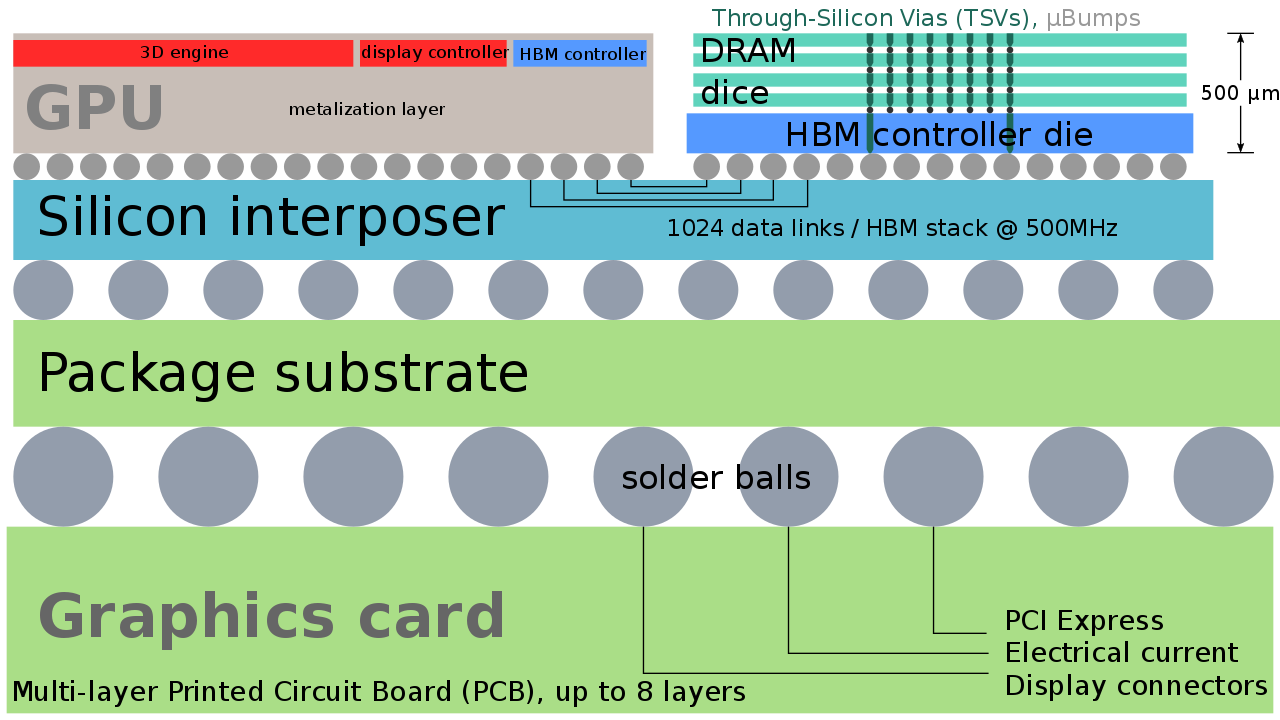

2. 使用硅中介层的封装技术 -2.5D封装

Silicon Interposer起承上启下的作用

缺点是:增加了厚度,增加了成本,所有Die出去的型号都要通过TSV技术过孔原本不必要,增加了成本。

目前工业界大部分的单封装的处理器基本都是这种封装技术。

例子:某GPU,左侧是计算引擎,右侧是堆叠的HBM内存,两者使用的是硅中介的方式互联。

TSMC称为是Chip on Wafer on Substrate技术,是一种使用硅中介和TSV技术的2.5D封装技术,简称CoWoS。

例如Nviaia p100使用的是这种技术

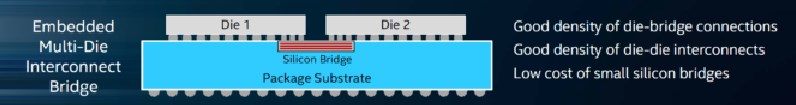

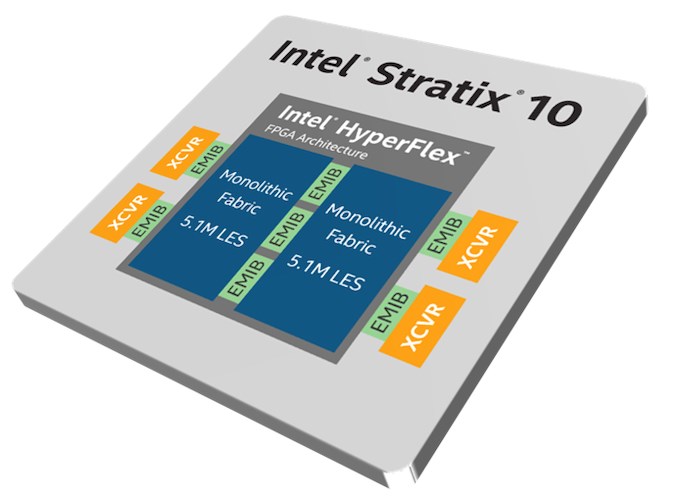

3. EMIB Embedded Multi-Die Interconnect Bridge 嵌入式多芯片互联封装技术-intel专有的2.5D封装

取消了中介,只增加一种桥叫做Silicon Bridge;

优点是:没有中介层不增加封装厚度;Die2Die通信才走Bridge,其他的走封装基底,不需要TSV,降低了成本;Die2Die更近,速度更高,损耗更小;

例子:Intel的FPGA产品 Stratix使用了EMIB将自己的计算核心和内存芯片联系在一起。

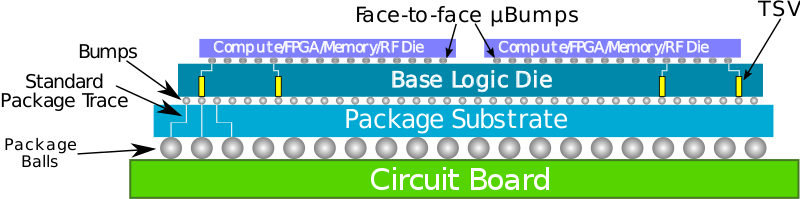

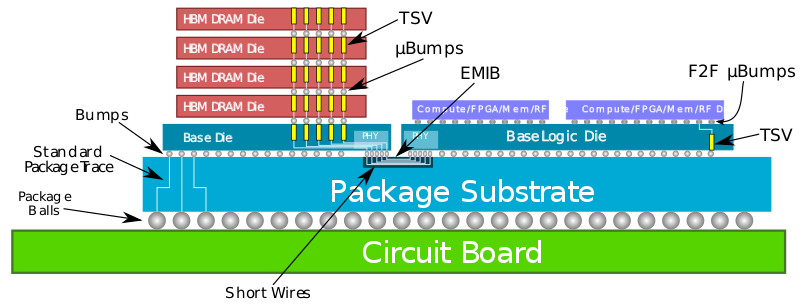

4. Foveros封装技术,英特尔专用2019年才有概念。

为了应对AMD的核心暴增,在一个大芯片上集成多核难度越来越大,未来的趋势肯定是Chiplet互联的方式,像AMD 的ROME那样

die和die在硅片上的通信成本比较小,在硅片下的基底上的通信需要考虑布线和距离一般成本更高

这种封装技术着重将多个die放在另外一个die之上,并且面对面的放置,进一步缩短连线,降低时延。

但是Foveros不是代替EMIB的,而是可以EMIB共存,Foveros更加注重的是向上的扩展,EMIB更加注重的是横向扩展。

例如:左边的HBM的die和右边的Foveros的封装之间通过EMIB互联。

左边的内存是3D Stack,结合Foveros一定程度是将整个芯片进化到3D封装了。

据称Intel将会在自己2020年发布的GPU卡上使用这种3D封装的技术。

参考文献:

前三种对比图片:

Intel对自家的EMIB技术的优势的介绍

Wikichip上对foveros的介绍

知乎上对前三种技术的优劣势的对比

CoWoS技术的介绍

名词解释:

Package Substrate 基板封装

Through Silicon Vias 过孔技术