静态时序分析和动态时序仿真各有什么特点

回答一:

IC时序验证用两种方法实现:一是动态时序分析,即根据电路中提取的延时参数,通过仿真软件动态的仿真电路以验证时序是否满足要求。二是静态时序分析,即通过分析设计中所有可能的信号路径以确定时序约束是否满足时序规范。

动态时序分析的时序确认通过仿真实现,分析的结果完全依赖于验证工程师所提供的激励。不同激励分析的路径不同,也许有些路径(比如关键路径)不能覆盖到,当设计规模很大时,动态分析所需要的时间、占用的资源也越来越大。

静态时序分析根据一定的模型从网表中创建无向图,计算路径延迟的总和,如果所有的路径都满足时序约束和规范,那么认为电路设计满足时序约束规范。静态时序分析的方法不依赖于激励,且可以穷尽所有路径,运行速度很快,占用内存很少。它完全克服了动态时序验证的缺陷,适合大规模的电路设计验证。对于同步设计电路,可以借助于静态时序分析工具完成时序验证的任务。

回答二:

动态时序分析就是通常我们所说的仿真,该仿真可以验证功能,也可以验证时序,首先确定测试向量,输入硬件模型,进行仿真。由于为了完整地测试每条路径的功能或者时序是否都满足,测试向量需要很大,也不能保证100%的覆盖率。如果到了门级的仿真将非常消耗时间。

静态时序分析只能分析时序要求而不能进行功能验证。不需要测试向量,能比动态时序分析快地多的完成分析。静态时序分析只能对同步电路进行分析,而不能对异步电路进行时序分析。但是它却可以验证每一条路径,发现时序的重大问题,比如建立时间和保持时间冲突,slow path以及过大的时钟偏移。

静态时序分析的优缺点

静态时序分析可以大大提高仿真时间,并能100%覆盖所有的路径。它通过预先计算所有的延时来提高速度。包括内部门延时以及外部的线延时。静态时序分析并不是简单的把各个延时相加,而是引入真值表,分析各种输入情况下所有可能经过的路径,而且能识别flase path。但是由于在深亚微米的工艺条件下,静态时序分析不能完整的把所有影响延时的因素给包含进去,因此在关键路径方面,便可以用STA工具导出关键路径的spice网表,用门级或者管级仿真工具进行电路仿真,以确定时序的正确性。

关于后仿真

步骤: 1.没有违例情况和功能报错

2.log对应文件的延时反标确认加入

3.波形正确

一定要同时确认violation和功能

① 出现时序violation但是功能正确的情况处理:

首先寻找关于make对应产生的log文件.然后找到有violation的位置,对应描述有setup、hold等在xx 例化模块在xx ns出现问题。

其次在post.v文件中找到对应的例化模块,在inc_lib的路径找到对应的输入输出描述。Z,ZN,Q,QN表示输出,其余表示输入。在verdi里面找到该cell对应的信号。在inc_lib的smic 0.13um的verilog模型库找到对应的输入输出关系,确定信号名对应的后仿真名称。在verdi里面将报的violation时间输入,对应前仿真结果,观察violation产生的原因。

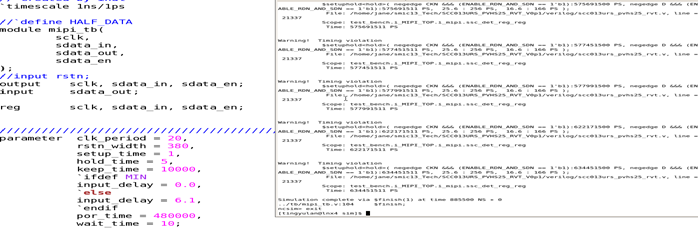

例如上次遇到ssc_det_reg_reg模块显示如图所示的时序违例情况

如图所示,当周期为20的时候,出现仿真时ssc_det_reg_reg的hold时间不足。首先要清楚我们无法修改setuptime和holdtime。Setup Time是时钟上升沿之前的数据所需要的(最小)有效时间,Hold Time是时钟上升沿之后的数据所需要的(最小)有效时间。

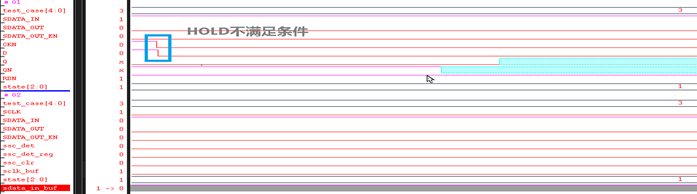

检查波形时发现由于D(ssc_det)的信号和clk的下降沿离的太近,HOLD时间不满足,造成QN(ssc_det_reg)出现亚稳态,所以QN信号显示为未知状态从而造成了这个时间violation。下面是波形图。

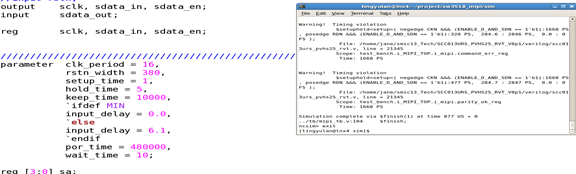

为了解决这个问题,只能延长时钟周期或者缩短input_delay.将时钟周期修改为19.2的原因是最大工作的频率要在52Mhz,为了留有余量,所以周期不能大于19.2.同时将input_delay缩短为5.4.这样修改之后没有时序问题.检查功能波形也正确.这个后仿真PASS.

②出现没有violation但是仿真结果错误的情况处理:

当没有violation出现时,我去查看功能,发现功能全部失败。如此一来,我需要加载debussy波形观察哪里出现问题。

通过观察,发现state没有正确的调到读状态,造成此原因的信号观察,发现dt_cnt和rev_dat的对应出现了问题。排查后发现,如图中虚线处所示,由于SSC信号没有按照应该的时间拉低,导致sclk第二个时钟没有被dt_cnt读进去,发现问题后,通过将周期修改大一些之后,解决了这个问题。

如何正确的观察后仿真是否正确:

1.没有violation

2.log文件中延时反标是否成功加入

3.txt文件有反馈的case正确

4.没有反馈的case的debussy是否正确