要将数据总线(2位或更多位宽度)从一个时钟域移到另一个时钟域,我们有几种处理方法。一下有几种方法可以采取。

1、格雷码:如果数据总线是单调计数器(即仅递增或递减),我们可以将其转换为格雷码,该格雷码具有跨时钟域的能力(在某些定时条件下)

2、数据冻结:如果数据总线是非单调的,则使用标志向其他域发出信号以捕获值(在源时钟域中冻结该值)。

3、数据突发:如果数据总线具有许多需要跨越时钟域的连续值,请使用异步FIFO,在其中您从源时钟域中推送值,并从另一个域中读取值。

一、第3种方法为例

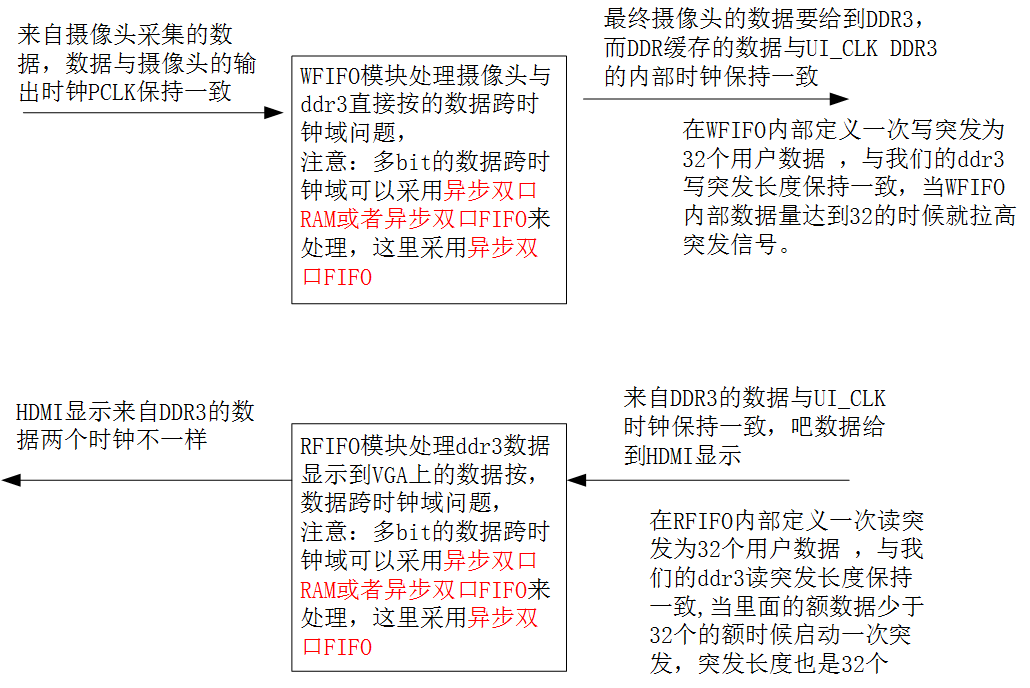

假设数据的流程为:

因为采取的数据一般为多bit 而且连续的数据,摄像头的时钟下的数据转换到ddr3始终下的数据,而ddr3的数据转换到vga始终下的数据。所以在摄像头采集模块与ddr3模块之间需要一个异步双口WFIFO,而在ddr3与vga之间需要一个异步双口的RFIFO。来完成数据在这几个时钟域之间的转换。一下给出一种方案;