数字电路设计的抽象层次:器件->电路->门->模块->系统

时钟偏差对全局信号都可能产生影响,是高性能大系统的设计关键。

集成电路的成本:固定成本+可变成本;固定成本可理解为研发成本,非重复的成本;可变成本可理解为生产制造(芯片成本和封测成本)过程中产生的成本,与良率也有关,控制芯片面积能够有效且直接的控制芯片成本。

一个门电路要想具有再生性,其VTC(电压传输特性)应当具有一个增益大于1的过渡区,以及增益小于1的合法区域,如下图:

封装可按照封装材料,互连层数量,散热方式进行分类:

封装材料:陶瓷封装、塑封(高分子聚合物)

NMOS与PMOS,以增强型为例,NMOS VGS>Vth时导通,PMOS |VGS|>|Vth|时导通,且VGS<0。

CMOS反相器电压传输特性(VTC)推导:

上式为CMOS上下管需要遵守的规则。

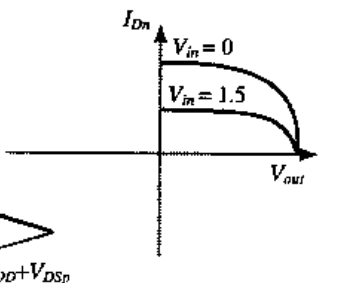

结合上式得到,下图为CMOS中上官PMOS部分不同栅极输入电压下,下管NMOS电流与输出电压的关系

为了使NMOS和PMOS的传输特性能够符合上式DC成立,需要根据二者的V-I曲线找到交叉点,使其满足DC平衡

找到上图中的DC平衡交叉点,并提取绘制得到CMOS的电压传输特性如下图,可以看出CMOS的电压传输特性具有再生性

其中res表示呈电阻特性

PMOS和NMOS的电流方向问题:

源極的源是指載流子的起點;漏極的漏是指載流子的終點。載流子從源極出發,穿過溝道,到達漏極,從外部看,載流子最終從漏極漏出去了。顯然,NMOS和PMOS的載流子是不同的,因此導致了令人困惑的電流方向問題。盯住載流子即可,別被電流方向迷惑。

可以簡單地認為,柵極和襯底間的電壓超過閾值後,漏極和源極就接通了,而電流大小則是由柵漏源三極間的電壓決定。因為MOS是對稱結構,所以源極和漏極無區別且可互換。

關於D和S,也就是漏和源,其實是從工藝角度觀察的結果。在MOS中,有兩種載流子,一種是電子,另一種是空穴,標記為N和P。顯然,NMOS的載流子是電子,PMOS的載流子是空穴。NMOS導通後,電子從源極進入溝道,從漏極離開。因為電子的運動方向與電流方向相反,所以電流從NMOS的漏極流向源極。相反地,在PMOS中,雖然空穴也是從源極進入溝道,從漏極離開,但空穴的運動方向與電流方向一致。因此,電流從PMOS的源極流向漏極。

CMOS中,通过上拉网络和下拉网络的互斥来保证静态下无直通电流,即上拉网络和下拉网络的导通状态总是相反。这意味着上拉网络和下拉网络存在对偶关系---串联对并联。https://blog.csdn.net/weixin_39550410/article/details/110299615

动态逻辑和静态逻辑的一些理解参考:http://bbs.eetop.cn/forum.php?mod=viewthread&tid=404635&page=1

差分传输管逻辑:与静态CMOS逻辑类似,都能构成门电路,不同的是,CMOS的输入只用于控制对偶网络的栅极,而差分传输管逻辑中NMOS的栅漏作为输入,通过下面几个传输逻辑可以总结出:对于NMOS组成的传输电路,逻辑表达式与NMOS电路的对应关系如下:以F=AB的NMOS电路图为例,F由上下NMOS形成的AND门求OR之后得到,F=AB则有F=AB+B(`B),则可以得到上下AND门的栅极和漏极分别上(B,A),(`B,B) 其他的逻辑电路推导类似。

传输门逻辑:结合NMOS强0和PMOS强1的特点,并联得到

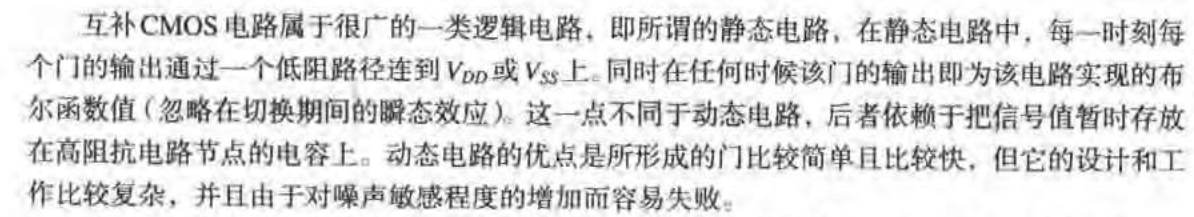

静态CMOS电路和动态CMOS电路:静态CMOS电路的输出节点保持低阻抗,动态电路的输出存放在高阻抗电路节点的电容上。静态电路的输出完全依赖于输入,输入不变,则输出不变,动态电路的输出不仅依赖于输入,还与系统动态时钟相关,若有不满足的条件,则可以保持原状态,而不跟随输入的变化而变化。

双稳态电路:锁存器,寄存器,触发器等;偶数个反相器串联能够实现锁存功能。

单稳态电路:可用作脉冲发生器

不稳电路:用作VCO压控振荡器,奇数个带有延时的反相器可实现一个VCO,延时td,反相器数量N,则振荡周期为2*td*N。*2的原因是当第一个反相器的输入为高时,该输入经过td*N后将会被反馈拉低,输入低时同理,则由高低电平组成的一个周期为2*N*td。

组合逻辑和时序逻辑的区别和联系

关于触发器锁存器以及寄存器的一些博客:

组合逻辑无反馈无记忆,当前的输出只与当前输入有关。

时序逻辑由组合逻辑+触发器组成,有反馈有记忆,当前的输出不仅与当前输入有关,还与之前的输出有关。

锁存器latch:电平敏感,有反馈,有记忆,当使能信号有效时,输出透明于输入,当使能信号无效时,输出通过反馈接到输入端来建立双稳态(这种双稳态建立方式是静态的),由于在使能信号有效期间,输入输出之间是透明的,因此,输入的空翻将会引起输出的跳变,这对后级是致命的,会导致系统的不稳定。latch一般存在于组合逻辑中,在RTL编程过程中,组合逻辑的条件不完备(如:if else语句中的else缺省导致系统需要在缺省处保持原有状态,或case语句中的赋值不完全,与if-else类似)都会导致latch,同时latch对设计是不友好的,因为在编译综合过程中,编译器可能会将latch优化掉(因为组合逻辑不允许有记忆有反馈,latch的存在会打破这种规则),导致前仿真和后仿真的结果不一致。在组合逻辑中避免ltch的方法有:1、完善输出的条件,确保没有输出到输入的反馈回路;2、改用时序逻辑来实现,时序逻辑应对这种情况生成的是触发器,是友好型的存储逻辑。

触发器flip-flop:边沿敏感,有反馈,有记忆,数据的传输发生在时钟信号跳变时(因此需要关注建立时间Ts和保持时间Th等以确保能够采样到有效稳定的输入)。

数字系统的时序分类:信号可以根据它们与本地时钟的关系来分类,在预先定义好的时钟周期上翻转的信号相对于系统时钟可分为同步的,中等同步的或者近似同步的。反之,可以在任意时间发生翻转的信号称为异步信号。

时钟偏差是由时钟路径的静态不匹配以及时钟在负载上的差异造成的