概述

MCS-51单片机片内集成了各种存储器和I/O功能部件,但有时根据应用系统的功能需求,片内的资源还不能满足需要,还需要外扩存储器和I/O功能部件(也称I/O接口部件),这就是通常所说的MCS-51单片机的系统扩展问题。

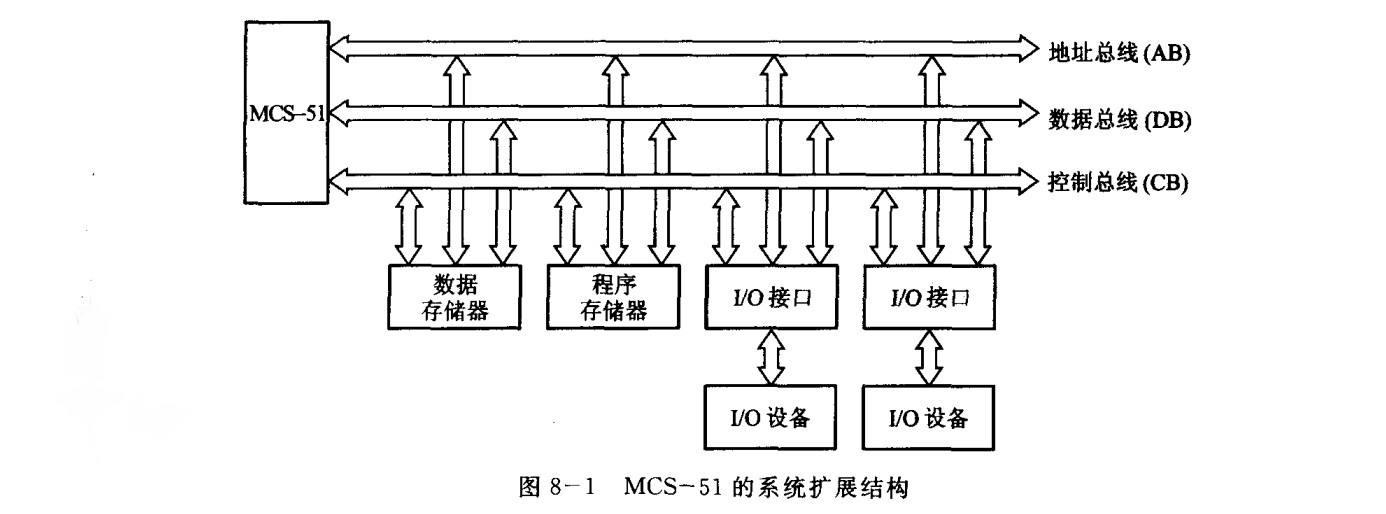

MCS-51系统扩展的内容主要有外部存储器的扩展(外部存储器又分为外部程序存储器和外部数据存储器)和I/O接口部件的扩展。本章介绍MCS-51单片机如何扩展外部存储器,有关I/O接口部件的扩展将在下一章介绍。MCS-51系统扩展结构如图8-1所示。

由图8-1可以看出:系统扩展是以MCS-51单片机为核心进行的。扩展内容包括扩展程序存储器(ROM)、数据存储器(RAM)、I/O接口部件及I/O设备等。

MCS-51单片机外部存储器结构,采用的是哈佛结构,即程序存储器的空间和数据存储器的空间是截然分开的。还有一种外部存储器的结构,它是程序存储器和数据存储器合用一个空间的结构:普林斯顿结构。例如,MCS-96单片机的存储器结构就是采用普林斯顿结构。

MCS-51单片机数据存储器和程序存储器的最大扩展空间各为64 KB,扩展后,系统形成了 2个并行的64 KB外部存储器空间。

由图8-1可以看出,扩展是通过系统总线进行的,通过总线把MCS-51单片机与各扩展部分连接起来,并进行数据、地址和控制信号的传送。因此,要进行系统扩展首先要构造系统总线。

系统总线及总线构造

系统总线

所谓总线,就是连接计算机各部件的一组公共信号线。MCS-51使用的是并行总线结构,按其功能通常把系统总统分为三组,即:

- 地址总线(Address Bus,简写AB)

地址总线用于传送单片机发出的地址信号,以便进行存储单元和I/O端口的选择。地址总线是单向的,只能由单片机向外送出。地址总线的数目决定着可直接访问的存储单元的数目。例如,”位地址,可以产生地址的数目为2”个连续地址编码,因此可以访问2”个存储单元,即通常所说的寻址范围为2”个地址单元。MCS-51单片机最多可以扩展64 KB,即65536个地址单元,因此,地址总线为16条。 - 数据总线(Data Bus,简写DB)

数据总线用于在单片机与存储器之间或单片机与I/O之间传送数据。单片机系统数据总线的位数与单片机处理数据的字长一致。MCS-51单片机是8位字长,所以,数据总线的位数也是8位的。数据总线是双向的,可以进行2个方向的传送。 - 控制总线(Control Bus,简写CB)

控制总线实际上就是一组控制信号线,包括单片机发出的,以及从其它部件传送给单片机的。对于一条具体的控制信号线来说,其传送方向是单向的,但是由不同方向的控制信号线组合的控制总线则表示为双向。

由于单片机系统采用总线结构形式,可以大大减少单片机系统中传输线的数目,提高了系统的可靠性,增加了系统的灵活性。此外,总线结构也使扩展易于实现,各功能部件只要符合总线规范就可以很方便地接入系统,实现单片机的

系统扩展。

构造系统总线

既然单片机的扩展系统是并行总线结构,因此单片机系统扩展的首要问题就是构造系统总线,然后再往系统总线上“挂”存储器芯片或I/O接口芯片,“挂”存储器芯片就是存储器扩展,“挂” I/O接口芯片就是I/O扩展。

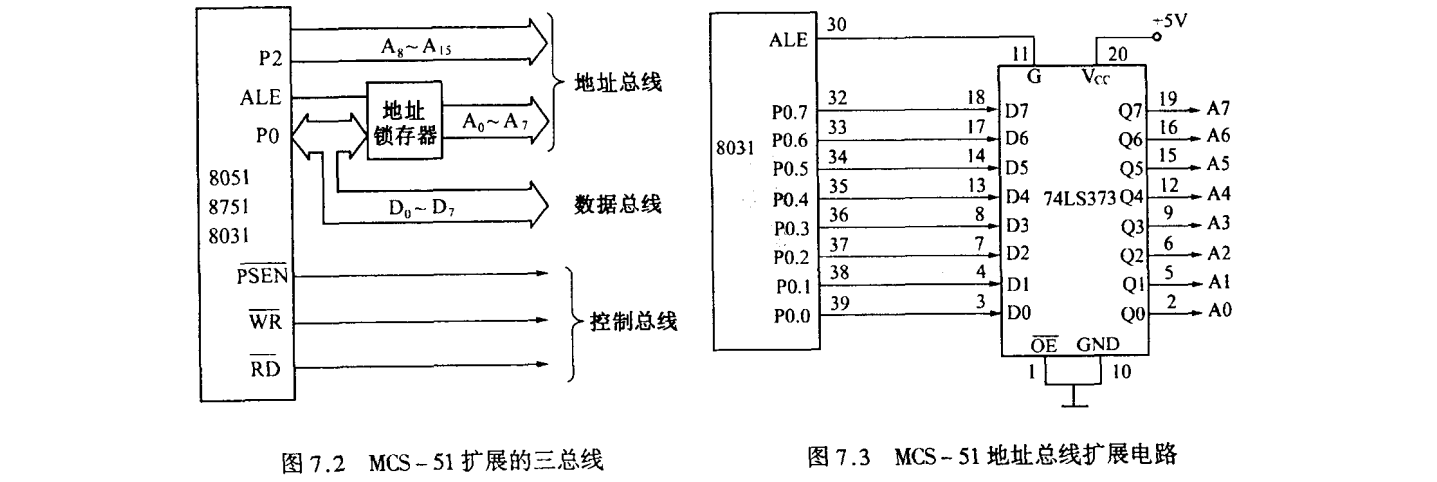

MCS-51单片机受引脚数目的限制,数据线和低8位地址线是复用的,而P0口线兼用。为了将它们分离出来,以便同单片机片外的扩展芯片正确的连接,需要在单片机外部増加地址锁存器,从而构成与一般CPU相类似的片外三总线,如图7.2所示。

地址锁存器一般采用74LS373,采用74LS373的地址总线的扩展电路如图7.3所示。

由MCS-51的P0 口送出的低8位有效地址信号是在ALE(地址锁存允许)信号变高的同时出现的,并在ALE由高变低时,将出现在P0 口的地址信号锁存到外部地址锁存器74LS373中,直到下一次ALE变高时,地址才发生变化,随后,P0 口又作为数据总线口。

下面说明总线的具体构造方法。

-

以P0 口作低8位地址/数据总线锁存器

因为P0口即作低8位地址线,又作数据线(分时复用),因此,需要增加一个8位锁存器。在实际应用时,先把低8位地址送锁存器暂存,然后再由地址锁存器给系统提供低8位地址,而把P0 口线作为数据线使用。实际上,MCS-51单片机的P0口的电路设计已考虑了这种应用要求,P0口线内部电路中的多路转接电路MUX以及地址/数据控制就是为此目的而设计的。

-

以P2 口的口线作高位地址线

如果使用P2 口的全部8位口线,再加上P0 口提供的低8位地址,便可形成完整的16位地址总线,使单片机系统的寻址范围达到64KB。但在实际应用系统中,高位地址线并不固定为8位,需要用几位就从P2 口中引出几条口线。 -

控制值号线

除了地址线和数据线之外,在扩展系统中还需要一些控制信号线,以构成扩展系统的控制总线。这些信号有的是单片机引脚的第一功能信号,有的则是第二功能信号。其中包括:- 使用ALE信号作为低8位地址的锁存控制信号。

- 以PSEN信号作为扩展程序存储器的读选通信号。

- 以EA信号作为内外程序存储器的选择控制信号。

- 以RD和WR信号作为扩展数据存储器和I/O 口的读选通、写选通信号。

可以看出,尽管MCS-51单片机有4个并行的I/O 口,共32条口线,但由于系统扩展的需要,真正作为数据I/O使用的,就剩下P1 口和P3 口的部分口线了。

单片机系统的串行扩展技术

随着单片机技术的发展,并行总线扩展(利用3组总统AB、DB、CB进行的系统扩展)已不再是单片机唯一的系统扩展结构了,随着集成电路芯片的集成度和结构的发展,近年来除并行总线扩展技术之外,又出现了串行总线扩展技术。

串行扩展技术具有显著的优点,一般地说,串行接口器件体积小,因而,所占用电路板的空间,仅为并行接口器件的10%,明显地减少了电路板空间和成本。串行接口器件与单片机接口时需要的I/O 口线很少(仅需3-4根),极大地简化了器件之间的连接,进而提高了可靠性。

串行扩展是是通过串行接口实现的,这样可以减少芯片的封装引脚,降低成本,简化了系统结构,增加系统扩展的灵活性。为了实现串行扩展,一些公司(例如PHILIPS和ATMEL公司等)已经推出了非总线型单片机芯片,并且具有SPI(Serial Periperal Interface)三线总线和PC公用双总统的两种申行总线形式。与此相配套,也推出了相应的串行外围接口芯片。

但是,一般串行接口器件速度较慢,在大多数应用的场合,还是并行扩展法占主导地位。在进行系统扩展时,应对单片机的系统扩展能力、扩展总线及扩展应用特点有所了解,这样才顺利的完成系统扩展任务。

读写控制、地址空间分配和外部地址锁存器

存储器拓展的读写控制

外扩的RAM芯片既能读出又能写人,所以通常都有读写控制引脚,记为OE和WE。外扩RAM的读写控制引脚分别与MCS-51的RD和WR引脚相连。

外扩的EPROM在正常使用中只能读出,不能写入,故EPROM芯片没有写入控制引脚,只有读出引脚,记为OE,该引脚与MCS-51单片机的歯J引脚相连。

存储器地址空间分配

在实际的单片机应用系统设计中,既需要扩展程序存储器,往往又需要扩展数据存储器。

在MCS-51扩展多片的程序存储器、数据存储器芯片的情况下,如何把外部各自的64KB的空间分配给各个芯片,并且使程序存储器的各个芯片之间、数据存储器(I/O接口芯片也作为数据存储器一部分)各芯片之间,地址不能发生重叠,以使单片机读、写外部存储器时,避免发生数据冲突。这就是存储器的地址空间的分配问题。

存储器的地址空间分配,实际上就是使用系统提供的地址线,通过适当连接,最终达到一个存储器单元只对应一个地址的要求。

MCS-51通过地址总线发出的地址是用来选择某一个存储器单元,在外扩的多片存储器芯片中,MCS-51要完成这种功能,必须进行两种选择:一是必须选中该存储器芯片(或I/O接口芯片),这称为片选。只有被“选中”的存储器芯片才能被MCS-51读出或写入数据。二是必须选择出该芯片的某一单元,称为单元选择。为了芯片选择(片选)的需要,每个存储器芯片都有片选信号引脚,因此芯片的选择的实质就是如何通过MCS-51的地址线来产生芯片的片选信号。

通常把单片机系统的地址笼统地分为低位和高位地址,存储器芯片的某一存储单元选择使用低位地址,剩下的高位地址才作为芯片选择使用,因此芯片的选择都是使用高位地址线。

实际上,在16位地址线中,高、低位地址线的数目并不是固定的,我们只是把用于存储单元选择所使用的地址线,都称为低位地址线,剩下多少就有多少高位地址线。存储器地址空间分配除了考虑地址线的连接外,还讨论各存储器芯片在整个存储空间中所占据的地址范围,以便在程序设计时正确地使用它们。

常用的存储器地址分配的方法有两种:线性选择法(简称线选法)和地址译码法(简称译码法),下面分别予以介绍。

线选法

线选法就是直接利用系统的高位地址线作为存储器芯片(或I/O接口芯片)的片选信号。为此,只需把用到的高位地址线与存储器芯片的片选端直接连接即可。

线选法的优点是电路简单,不需要地址译码器硬件,体积小,成本低。缺点是可寻址的器件数目受到限制,故只用于不太复杂的系统中。另外,地址空间不连续,每一个存储单元的地址不唯一,这会给程序设计带来一些不方便。

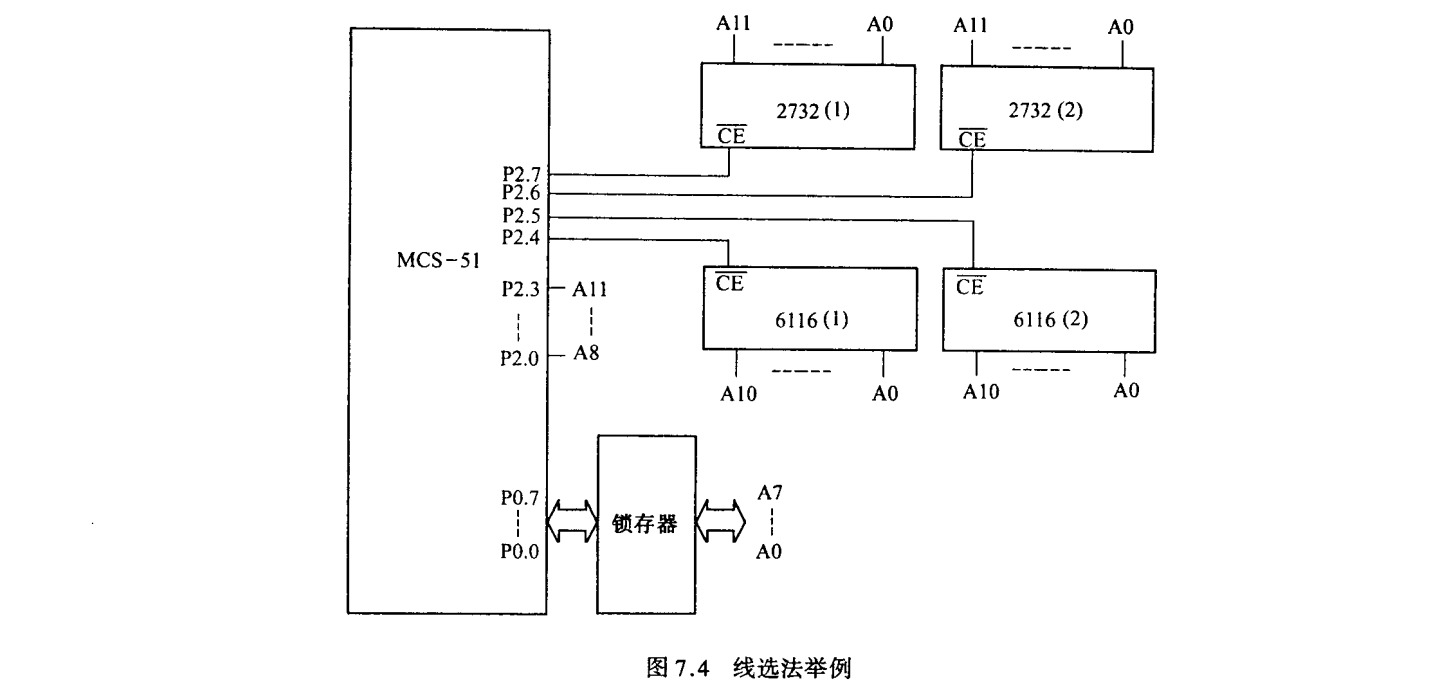

下面通过一个具体例子,来说明线选法的具体应用。

假设某一单片机系统,需要外扩8KB的EPR0M(2片2732),4KB的RAM(2片6116),这些芯片与MCS -51单片机的接口电路如图7.4所示,这里只画出与地址分配有关的地址线连线。

先看程序存储器2732与MCS-51的连接。由于2732是4KB的程序存储器,有12根地址线A11 ~ A0,它们分别与单片机的P0口及P2.0-P2.3相连,从而实现4K字节单元的选择(存储单元选择使用低位地址)。电于系统中有2片程序存储器,存在2片程序存储器芯片之间相区别的问题,2732(1)片选CE接A15(P2.7),2732(2)片选端赤接A14(P2.6)(片选使用高位地址),当要选中某个芯片时,单片机P2 口对应的片选信号引脚应为低电平,其它引脚一定要为高电平。这样才能保证一次只选中一片,而不会再选中其它同类存储器芯片,这就是所谓的线性选址法,简称线选法。

再来看数据存储器与单片机的接口。数据存储器也有2片芯片需要区别。这里用P2.5和P2.4分别作为这2片芯片的片选信号。当要选中某个芯片时,单片机P2 口对应的片选信号引脚应为低电平,其它引脚一定要为高电平。由于6116是2KB的,需要11根地址线作为存储单元的选择,而剩下的P2 口线(P2.4-P2.7)正好作为片选线。

从图7.4中可以看出,程序存储器2732的低2KB和数据存储器6116的地址是重叠的。那么会不会MCS-51发出访问2732某个单元的地址时,同时也会选中6116的的某个单元,这样MCS-51就会同时选中两个单元,从而发生数据冲突,产生错误呢?

这种情况,完全不用担心,虽然两个单元的地址是一样的,但是MCS-51发给两类存储器的控制信号是不一样的。如果访问的是程序存储器,则是PSEN信号有效;如果访问的是数据存储器,则是RD或WR信号有效。以上控制信号是由MCS-51执行访问外部程序存储器或访问外部数据存储器的指令产生,任何时刻只能执行一种指令,产生一种控制信号,所以不会产生数据冲突的问题。

通过上面的讨论,可以得出一个重要的结论:MCS-51单片机外扩程序存储器和数据存器的地址空间可以重叠,只是注意程序存储器和程序存储器之间,数据存储器和数据存储器之间,千万不要发生地址重叠。现在再来看两个程序存储器的地址范围。

现在再来看两个程序存储器的地址范围。

2732(1)的地址范围:

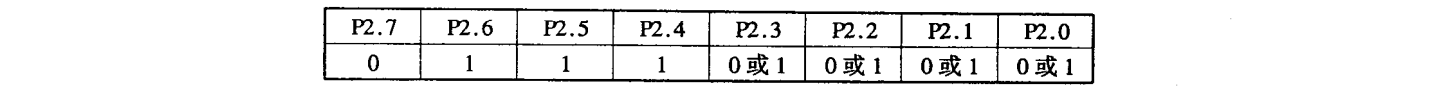

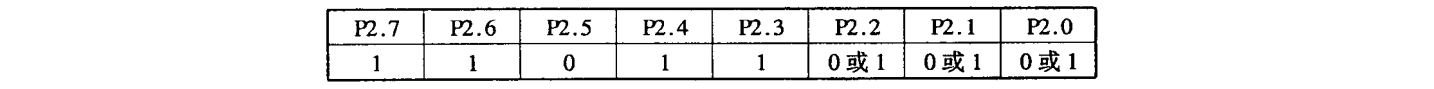

选中2732(1)时,P2 口(高8位的地址)各引脚的状态为:

由上面介绍可见高8位的地址变化范围:70H ~ 7FH

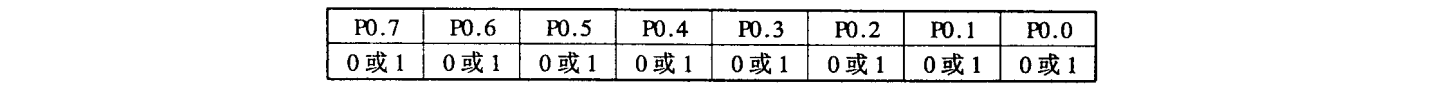

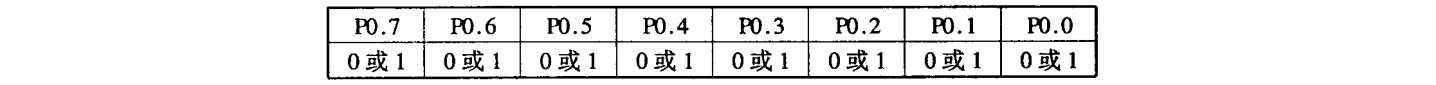

由上可见低8位的地址变化范围:00H ~ FFH

所以2732(1)的地址范围变化范围为:7000H~7FFFH

2732(2)的地址范围:

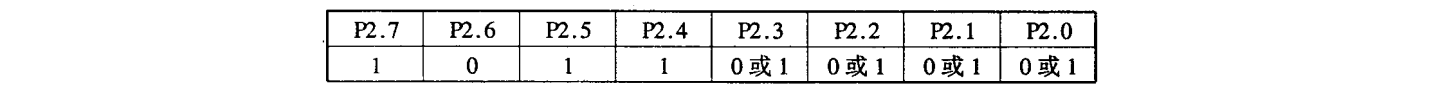

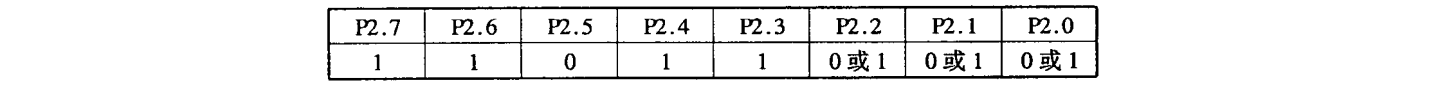

选中2732(2)时,P2 口(高8位的地址)各引脚的状态为

由上可见高8位的地址变化范围:BOH-BFH

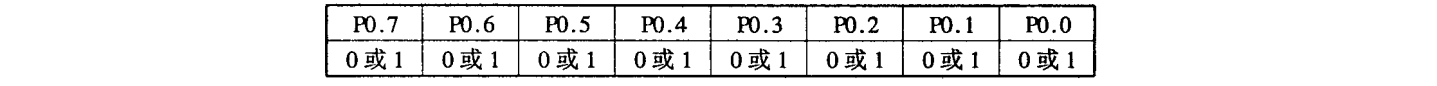

由上可见低8位的地址变化范围:00H~ FFH

所以2732(2)的地址的变化范围为:B000H- BFFFH

现在再来看两个数据存储器的地址范围。

6116(1)的地址范围:

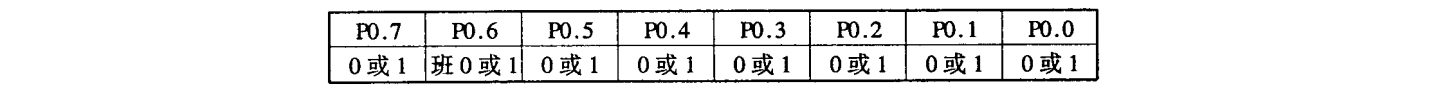

选中6116(1)时,P2 口(高8位的地址)各引脚的状态为:

由上可见高8位的地址变化范围:ECH ~ EFH

由上可见低8位的地址变化范围:00H ~ FFH

所以6116(1)的地址范围变化范围为:EC00H~EFFFH

6116(2)的地址范围:

选中6116(2)时,P2 口(高8位的地址)各引脚的状态为:

由上可见高8位的地址变化范围:D8H~ DFH

由上可见低8位的地址变化范围:00H~FFH

所以6116(2)的地址范围变化范围为:D800H-DEFFH

由上面介绍可见,线选法的特点是简单明了,不需要另外增加硬件电路。但是,这种方法对存储器空间的利用是断续的,不能充分有效地利用存储空间,扩展的存储器容量有限,只适用于外扩的芯片数目不多,规模不大的单片机系统的存储器扩展。

译码法

译码法就是使用译码器对MCS-51的高位地址进行译码,译码器的译码输出作为存储器芯片的片选信号。这是一种最常用的存储器地址分配的方法,它能有效的利用存储器空间,适用于大容量多芯片的存储器扩展。

译码电路可以使用现成的译码器芯片。最常用的译码器芯片有:74LS138(3- 8译码器)7415139(双2-4译码器)7415154(4- 16译码器),它们的CMOS芯片分别为:74HC138、74HC139、74HC154。它们使用灵活,完全可根据设计者的要求来组合译码,产生片选信号。

若全部地址都参加译码,称为全译码;若部分地址参加译码,称为部分译码,部分译码存在着部分存储器地址空间相重叠的情况。

下面我们以7415138为例。来介绍如何进行地址分配。例如要扩8片8KB的RAM 6264,如何通过74LS138把64K空间分配给各个芯片?

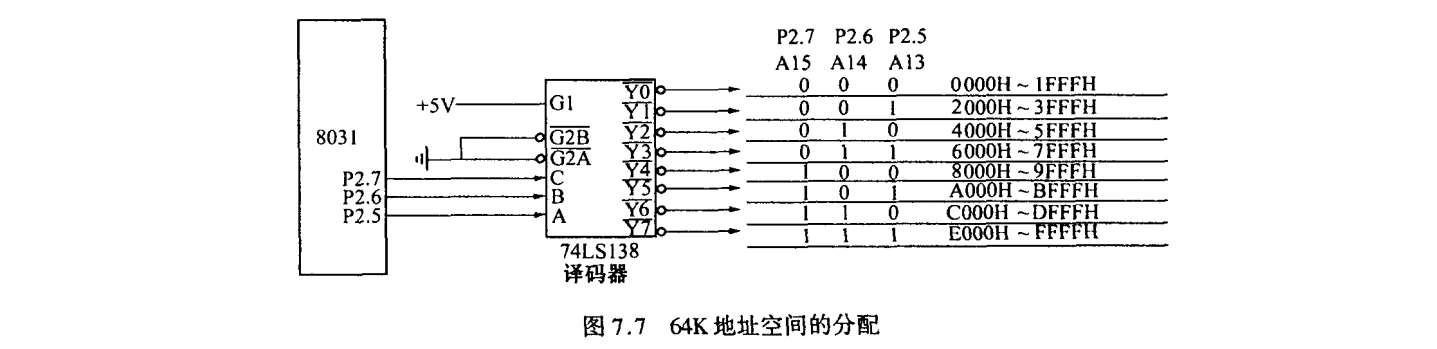

由7415138真值表可知,把G1接到+ 5V,G2A,G2B接地,P2.7、P2.6、P2.5 分别接到 74LS138 的 C、B、A 端,P2.4 ~ P2.0,P0.7 ~ P0.0 这13根地址线接到8片6264的A12 - A0脚。

由于对高3位地址译码,这样译码器有8个输出Y0 ~ Y7,分别接到8片6264的片选端,而低13位地址(P2.4~ P2.0.P0.7 ~ P0.0)完成对6264存储单元的选择。这样就把64K存储器空间分成8个8K空间了。64K地址空间的分配如图7.7所示。

这种除了单元选择的地址线外,剰余的高位地址线全部参加译码的方式称为全地址译码方式。由于采用的是全地址译码方式,MCS-51单片机发地址码时,每次只能唯一地选中一个存储单元。这样,同类存储器之间根本不会产生地址重叠的问题。

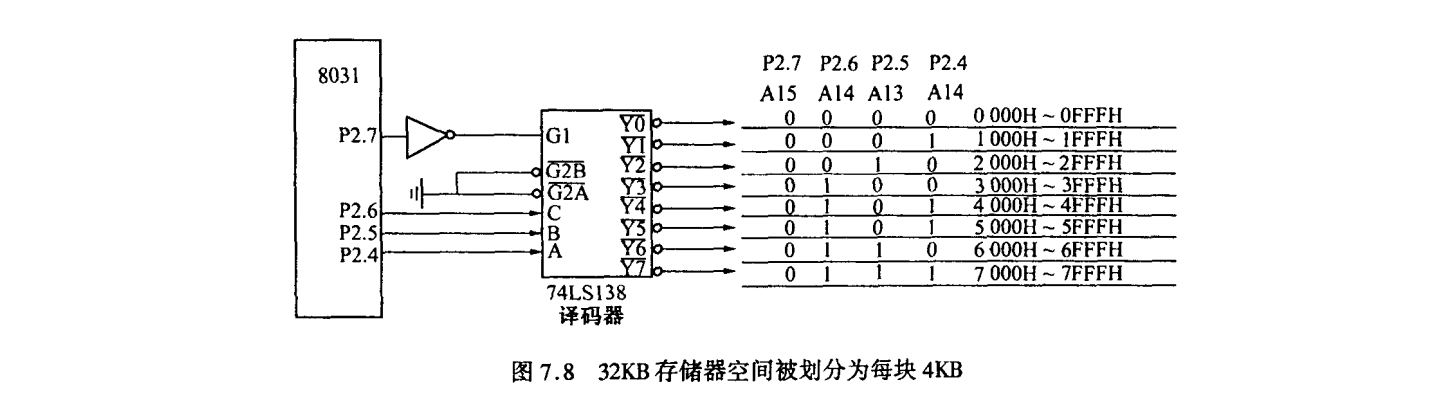

如果用74LS138把64K空间全部划分为每块4KB,如何划分呢?由于4KB空间需要12根地址线进行单元选择,而译码器的输入有3根地址线(P2.6~P2.4),P2.7没有参加译码,P2.7发出的0或1决定了选择64KB存储器空间的前32K还是后32K,由于P2.7没有参加译码(高位地址没有全部参加译码,就不是全译码方式),这样,前后两个32K空间就重叠了。

但是在实际的应用设计时,32KB存储器空间在大部分情况下是够用的。那么,这32KB空间利用74LS138译码器可划分为8个4KB空间。如果把P2.7通过一个非门与74LS138译码器的G1端连接起来,如图7.8所示,这样就不会发生两个32K空间重叠的问题了。这时,选中的是64K空间的前32K空间,地址范围为0000H ~ 7FFFH。如果去掉图7.8中的非门,地址范围为8000H ~ FFFFH。把译码器的输出连到各个4K存储器的片选端,这样就把32K的空间划分为8个4K空间。P2.3 ~ P2.0.P0.7 ~ P0.0实现对单元的选择,P2.6 ~ P2.4通过74LS138译码器的译码实现对存储器的片选。

如果利用741S138译码器实现每块为2KB的划分,这晚产生4个16K存储器空间的划分。如果把P2.7同74IS138译码器的G1端相连,P2.6同G2A端相连,这样一来就把64K空间固定为4个16K空间中的一个。改变P2.7.P2.6同译码器G1端、G2A端连接的逻辑,即可改变选中4个16K空间中的某一个。译码器的8个输出,即把16KB空间划分为2KB 一个的存储空间了。读者可自己画出这部分电路以及译码器输出的对应地址范围。

外部地址锁存器

MCS-51单片机受引脚数的限制,数据线和地址线是复用的,由P0口线兼用。为了将它们分离出来,以便同单片机片外的扩展芯片正确的连接,需要在单片机外部増加地址锁存器。目前,常用的地址锁存器芯片有:74LS373、8282、74I&73等。

程序存储器EPROM拓展

程序存储器一般采用只读存储器,因为这种存储器在电源关断后,仍能保存程序(我们称此特性为非易失性的),在系统上电后,CPU可取出这些指令予以重新执行。只读存储器简称为ROM(Read Only Memory)。ROM中的信息一旦写入之后,就不能随意更改,特别是不能在程序运行的过程中写入新的内容,故称之为只读存储器。

向ROM中写入信息叫做ROM编程。根据编程的方式不同,ROM分为以下几种:

- 掩膜ROM

掩膜ROM是在制造过程中编程。因编程是以掩膜工艺实现的,因此称为掩膜ROM。这种芯片存储结构简单,集成度高,但由于掩膜工艺由于成本较高,因此只适合于大批量生产。在批量大的生产中,一次性掩膜生产成本才是很低的。 - 可编程 ROM(PROM)

PROM(可编程只读存储器)芯片出厂是并没有任何程序信息,是由用户用独立的编程器写入的。但PROM只能写入一次,写入内容后,就不能再进行修改。 - EPROM

EPROM是用电信号编程,用紫外线擦除的只读存储器芯片。在芯片外壳上的中间位置有一个圆形窗口,通过这个窗口照射紫外线射就可擦除原有的信息。 - E2PROM( EEPROM)

这是一种用电信号编程,也用电信号擦除的ROM芯片,对E2PROM的读写操作与RAM存储器几乎没有什么差别,只是写入的速度慢一些。但断电后能够保存信息。 - Flash ROM

Flash ROM又称闪烁存储器,或称快擦写ROMo Flash ROM是在EPROM、E2PROM的基础上发展起来的一种只读存储器。是一种非易失性、电擦除型存储器。其特点是可快速在线修改其存储单元中的数据,标准改写次数可达1万次,而成本却比普通e2prom低得多,因而可大量替代E2PROM。与E2PROM相比,E2PROM的写入的速度较慢。但是,Flash ROM的读写速度都很快,存取时间可达70ns。由于其性能比E2PROM要好,所以目前大有取代E2PROM的趋势。

EPROM芯片介绍

程序存储器的扩展可根据需要来使用上述的各种只读存储器的芯片,但使用比较多的是EPROM E2PROM,下面首先对常用的EPROM芯片进行介绍。

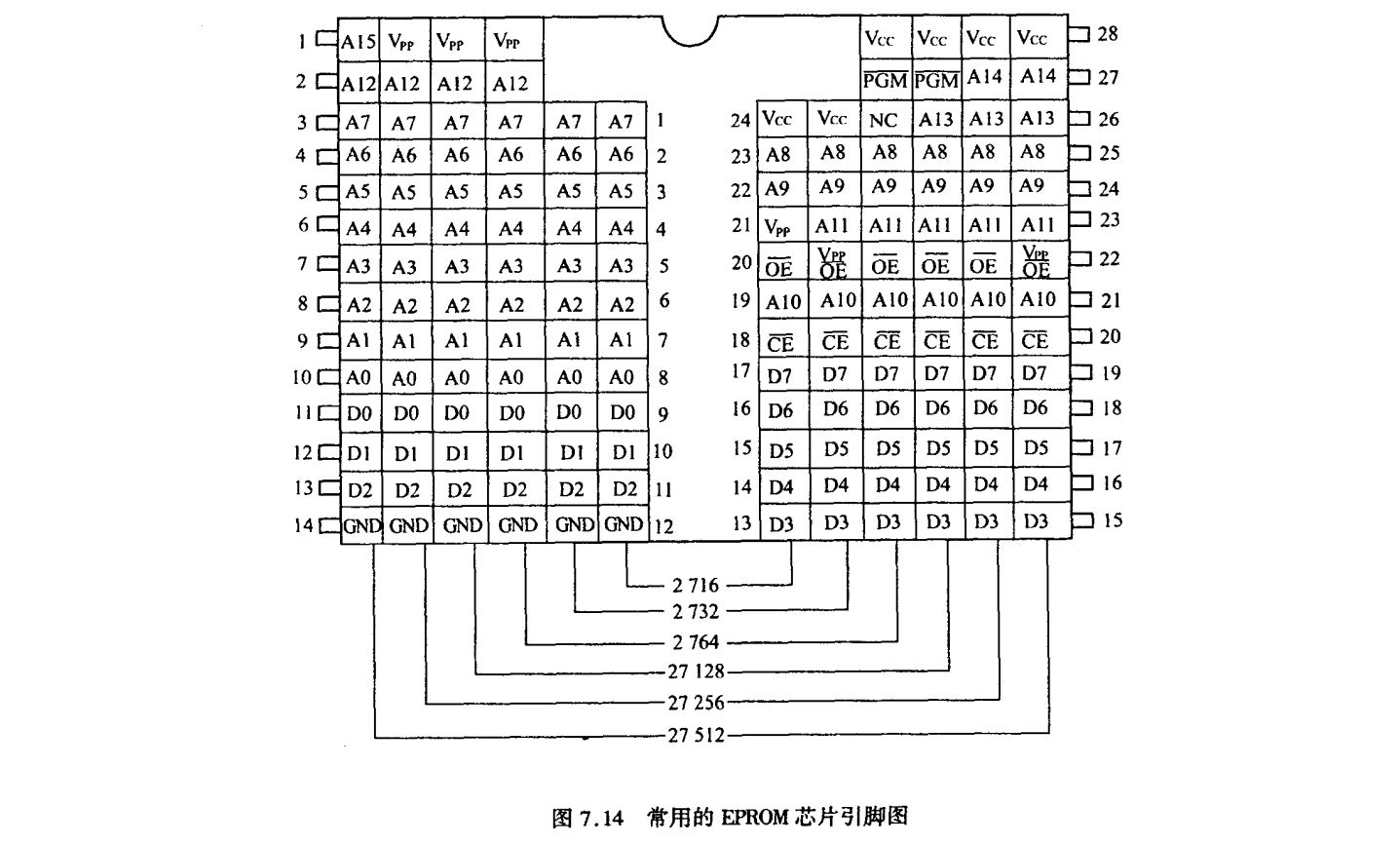

EPROM 的典型芯片是 27 系列产品,例如,2716(2KB x 8)、2732(4KB x 8)、2764(8KB x 8)、27128( 16KB x8)、27256(32KB x 8)、27512(64KB x 8)。型号名称“27”后面的数字表示其位存容量。如果换算成字节容量,只需将该数字除以8即可。

随着大规模集成电路技术的发展,大容量存储器芯片的产暈剧増,售价不断下降。大容量存储器芯片的性价比明显增高,而且由于有些厂家已停止生产小容量的芯片,使市场上某些小容量芯片的价格反而比大容量芯片还贵(例如,目前2716.2732已经停止生产,在市场上已经很难买到)。所以,在扩展程序存储器设计时,应尽量采用大容量的芯片。这样,不仅可以使电路板的体积缩小,成本降低,还可以降低整机功耗和减少控制逻辑电路,从而提高系统的稳定性和可靠性。

常用的EPRW芯片

27系列EPROM的芯片的引脚如图7.14所示。

在图7.14中的芯片的引脚功能如下:

A15 ~ A0:地址线引脚。地址线引脚的数目由芯片的存储容量来定,用来进行单元选择。

D7~D0:数据引脚

CE:片选输入端

OE:输出允许控制端

PGM:编程时,加编程脉冲的输入端

Vpp:编程时,编程电压(+ 12V或+ 25V)输入端

Vcc:+5V,芯片的工作电压。

GND:数字地。

NC:无用端

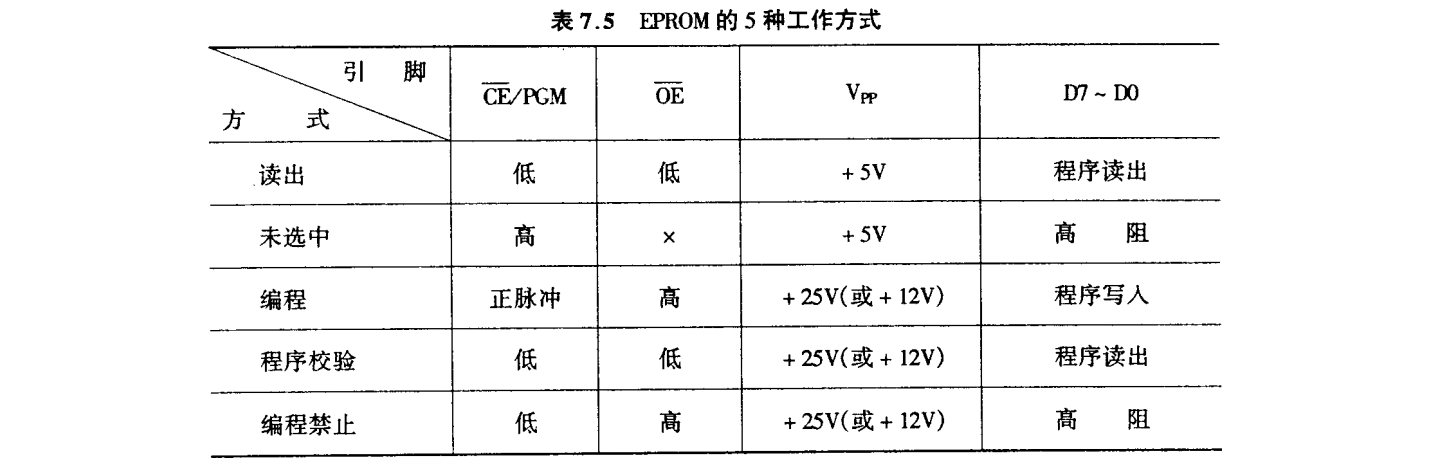

EPROM芯片的工作方式

EPROM 一般都有5种工作方式,由CE、OE、PGM各信号的状态组合来确定。5种工作方式如表7.5所示。

- 读出方式

一般情况下,EPROM工作在这种方式。工作在此种方式的条件是使片选控制线CE为低,同时让输出允许控制线OE为低,Vpp为+ 5V,就可将EPROM中的指定地址单元的内容从数据引脚D7~D0上读出。 - 未选中方式

当片选控制线CE为高电平时,芯片进入未选中方式,这时数据输出为高阻抗悬浮状态,不占用数据总线。EPROM处于低功耗的维持状态。 - 编程方式

在Vpp端加上规定好的高压,CE和OE加上合适的电平(不同的芯片要求不同),就能将数据线上的数据写入到指定的地址单元。此时,编程地址和编程数据分别由系统的A15-A0和D7-D0提供。 - 编程校验方式

在Vpp端保持相应的编程电压(高压),再按读出方式操作,读出编程固化好的内容,以校验写入的内容是否正确。 - 编程禁止方式

本工作方式输出呈高阻状态,不写入程序。

程序存储器的操作时序

访问程序存储器的控制信号

MCS-51单片机访问片外程序存储器时,所用的控制信号有:

- ALE——用于低8位地址锁存控制。

- PSEN——片外程序存储器“读选通”控制信号。PSEN接外扩EPROM的OE引脚。

- EA——片内、片外程序存储器访问的控制信号。EA=1时,访问片内程序存储器;当EA=0时,访问片外程序存储器。

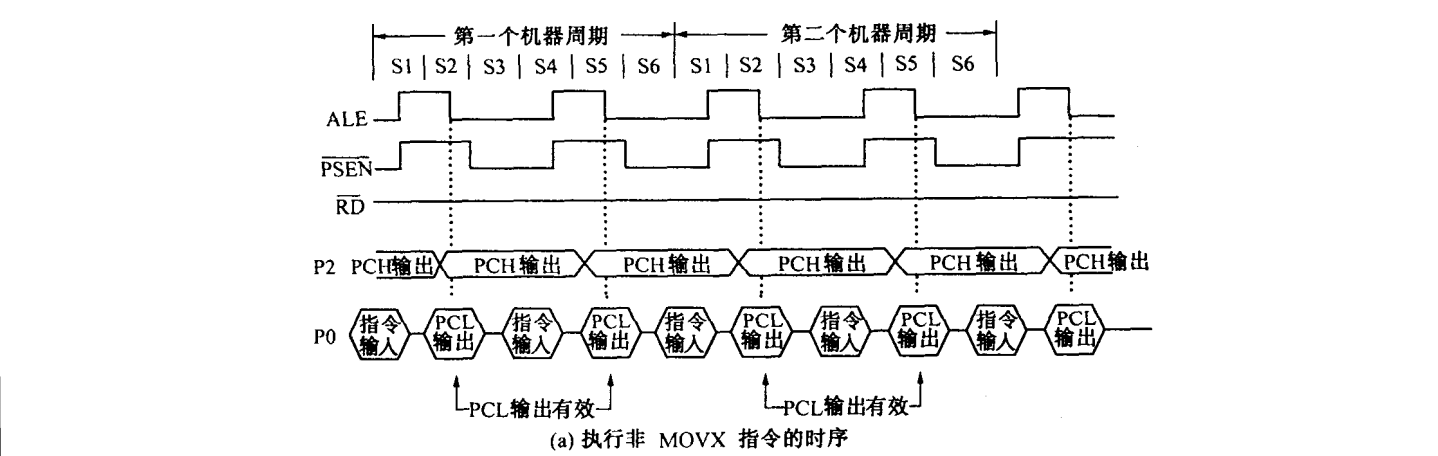

如果指令是从片外EPROM中读取的,除了ALE用于低8位地址锁存信号之外,控制信号还有PSEN,PSEN接外扩EPROM的OE脚。此外,还要用到P0口和P2 口,P0口分时用作低8位地址总线和数据总线,P2 口用作高8位地址线。相应的时序图如图7.15所示。

操作时序

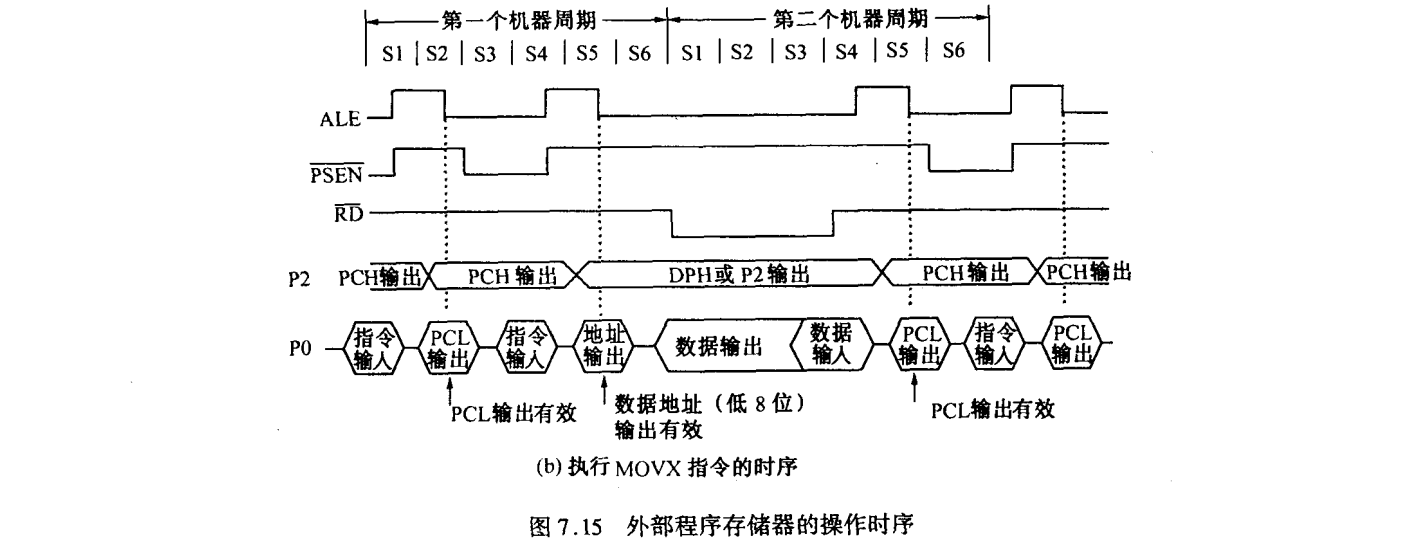

由于MCS-51单片机中ROM和RAM是严格分开的,因此,对片外ROM的操作时序分为两种情况:执行非MOVX指令的时序,如图7.15(a)所示;执行MOVX指令的时序,如图7.15(b)所示。

-

应用系统中无片外RAM

无片外RAM,则不用执行MOVX指令。在执行非MOVX指令时,P0 口作为地址/数据复用的双向总线,用于输入指令或输出程序存储器的低8位地址PCL。P2 口专门用于输出程序存储器的高8位地址PCH。

P2 口具有输出锁存功能;而P0 口输出地址外,还要输入指令,故要用ALE来锁存P0 口输岀的地址PCL。在每个机器周期中,允许地址锁存信号ALE两次有效,在ALE下降沿时,锁存出现在P0 口上的低8位地址PCL。同时,PSEN也是每个机器周期中两次有效,用于选通片外程序存储器,将指令读入片内。

系统无片外RAM时,此ALE有效信号以振荡器频率的1/6出现在引脚上,它可以用作外部时钟或定时脉冲信号。

-

应用系统中接有片外RAM

在执行访问片外RAM的MOVX指令时,程序存储器的操作时序有所变化。

其主要原因在于,执行MOVX指令时,16位地址应转而指向数据存储器,操作时序如图7.15(b)所示。在指令输入以前,P2 口、P0 口输出的地址PCH、PCL指向程序存储器;在指令输入并判定是MOVX指令后,ALE在该机器周期S5状态锁存的P0 口的地址不是程序存储器的低8位,而是数据存储器的地址。

若执行的是“MOVX A,@DPTR”或“MOVX @DPTR,A”指令,则此地址就是DPL(数据指针的低8位);同时,在P2 口上出现的是DPH(数据指针的高8位)。若执行的是“MOVX A,@Ri”或“MOVX @Ri,A”指令,则Ri的内容为低8位地址,而P2 口线上将是P2 口锁存器的内容。在同一机器周期中将不再出现PSEN有效取指信号,下一个机器周期中ALE的有效锁存信号也不复岀现;而RD/WR有效时,P0 口将读/写数据存储器中的数据。

由图7.15(b)可以看出:

- 将ALE用作定时脉冲输出时,执行一次MOVX指令会丢失一个脉冲。

- 只有在执行MOVX指令时的第二个机器周期期间,地址总线才由数据存储器使用。

典型的EPROM接口电路

使用单片EPROM的扩展电路

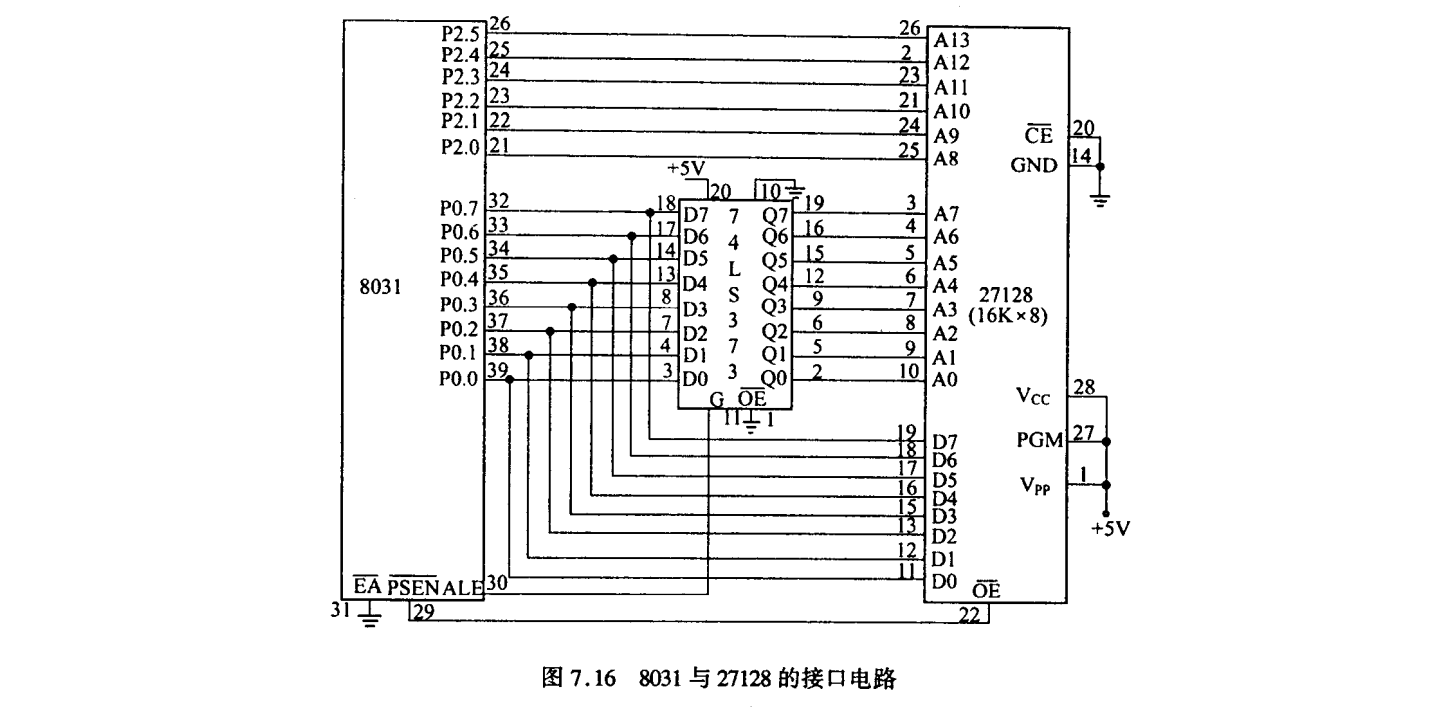

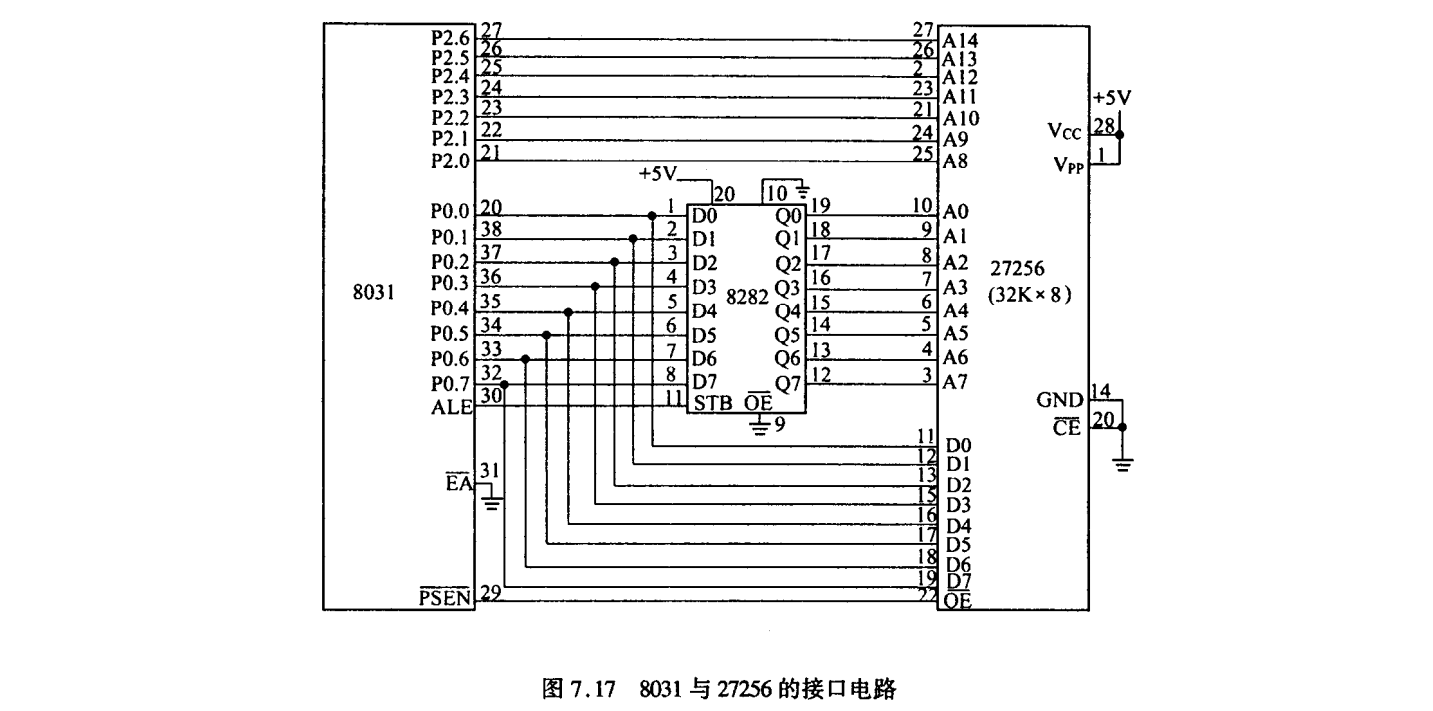

由于2764与27128引脚的差别仅在26脚上,2764的26脚是空脚,27128的26脚是地址线A13,因此在设计外扩存储器电路时,应选用27128芯片设计电路。在实际应用时,可将27128换成2764,系统仍能正常运行,反之,则不然。图7.16给出了 MCS-51外扩16K字节EPROM的27128的电路图。图7.17给岀了 MCS-51外扩32K字节的EPROM 27256的线路图。

注意在图7.16、图7.17中的两种地址锁存器的用法。

使用多片EPROM的扩展电路

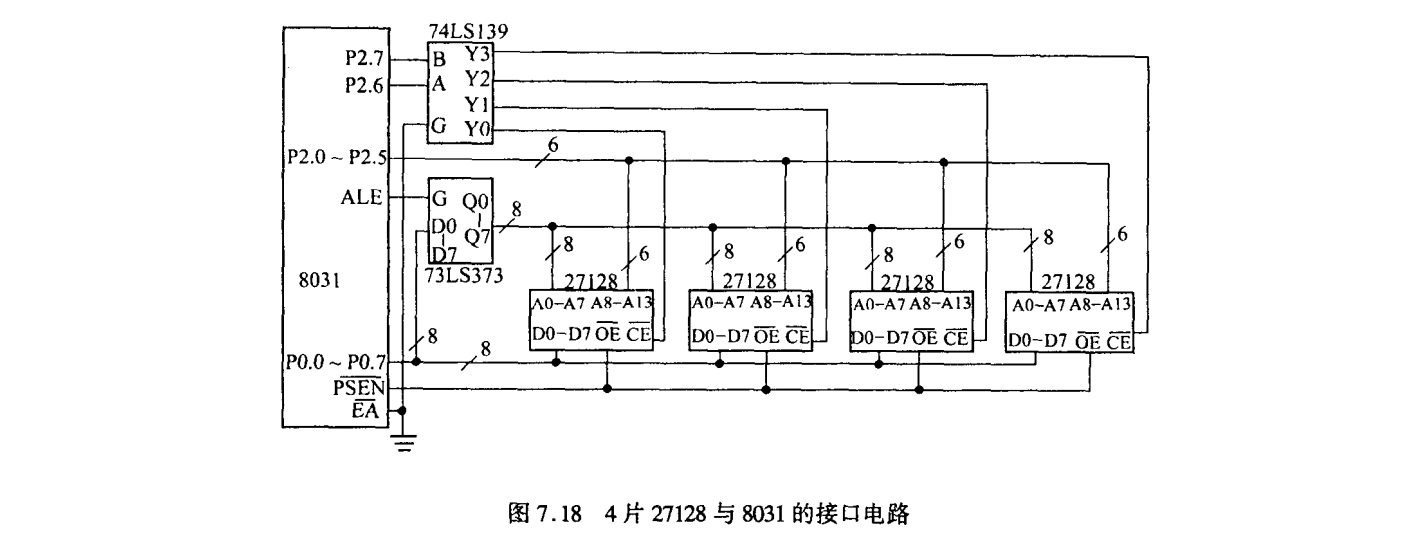

与单片EPROM扩展电路相比,多片EPROM的扩展除片选线CE外,其他均与单片扩展电路相同。图7.18给出了利用4片27128EPROM扩展成64K字节程序存储器的方法。片选信号由译码选通法产生。4片27128各自所占的地址空间,请读者自己分析。

静态数据存储器的拓展

MCS-51单片机内部有128个字节RAM。在实际应用中,仅靠片内RAM往往不够用,必须扩展外部数据存储器。常用的数据存储器有静态存储器(SRAM)和动态存储器(DRAM),在单片机应用系统中,外扩的数据存储器都采用静态数据存储器。

所扩展的数据存储器空间地址,由P2 口提供高8位地址,P0 口分时提供8位地址地址和用作8位的双向数据总线。片外数据存储器RAM的读和写由8031的RD(P3.7)和WR(P3.6)信号控制,而片外程序存储器EPROM的输出允许端(OE)由PSEN信号控制。尽管与E-PROM共处同一地址空间,但由于控制信号不同,故不会发生总线冲突。

常用的静态RAM(SRAM)芯片

单片机系统中常用的SRAM芯片的典型型号有:6116(2K x 8),6264 ( 8K x 8),62128( 16K x 8) ,62256(32K x 8)。它们都用单一+5V电源供电,双列直插封装,6116为24引脚封装,6264、62128、62256为28引脚封装。

SRAM的各引脚功能如下:

A0-A14:地址输入线。

D0~D7:双向三态数据线。

CE:片选信号输入线,低电平有效。对玉6264芯片,当26脚(CS)为高电平时,且衣为低电平时才选中该片。

OE:读选通信号输入线,低电平有效。

WE:写允许信号输入线,低电平有效。

Vcc:工作电源+5 Vo

GND:地线。

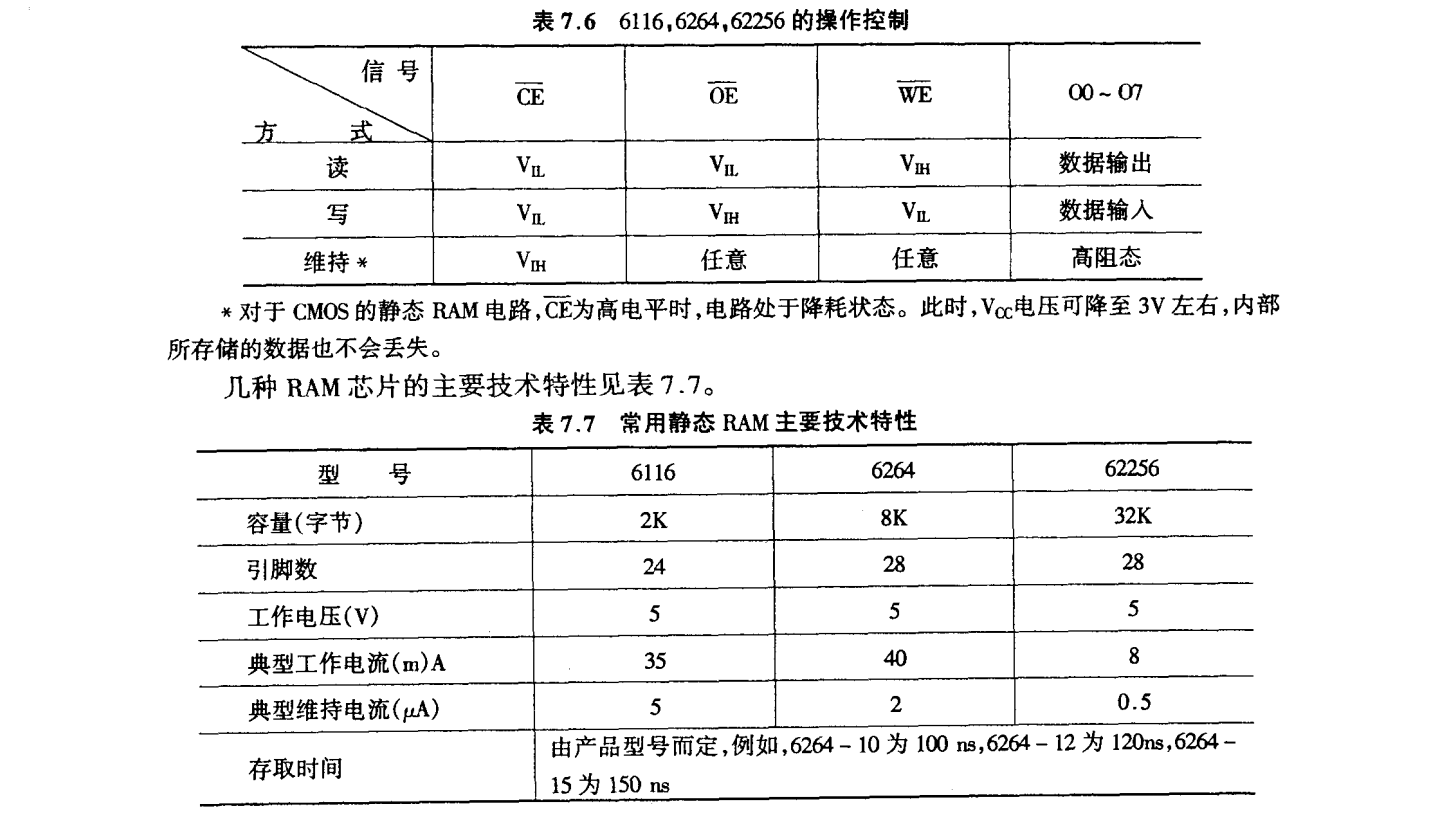

静态RAM存储器有读出、写入、维持三种工作方式,这些工作方式的操作控制如表7.6所示。

外扩数据存储器的读写操作时序

NTCS-51对外扩RAM读和写两种操作时序的基本过程是相同的。所用的控制信号有ALE、RD(读)和WR(写)。

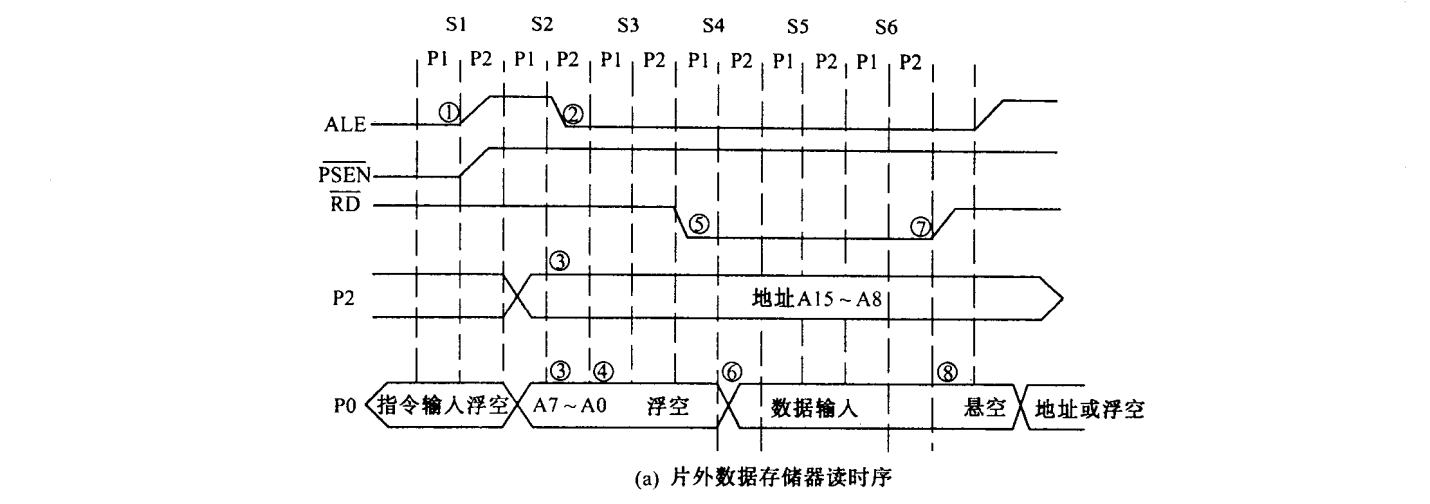

读片外RAM操作时序

8031单片机若外扩一片RAM,应将其WR引脚与RAM芯片的WE引脚连接,而引脚与芯片况引脚连接。ALE信号的作用与8031外扩EPROM作用相同,即锁存低8位地址。读片外RAM周期时序如图7.20(a)所示。

在第一个机器周期的S1状态,ALE信号由低变高①,读RAM周期开始。在S2状态,CPU把低8位地址送到P0 口总线上,把高8位地址送上P2 口 (在执行“MOVX A, @DPTR”指令阶段时才送高8位;若是“MOVX A, @Ri”则不送高8位)。

ALE的下降沿②用来把低8位地址信息锁存到外部锁存器74LS373内③。而高8位地址信息一直锁存在P2 口锁存器中。

在S3状态,P0总线变成高阻悬浮状态④。在S4状态,而信号变为有效⑤(是在执行“MOVX A @DFIR'后使而信号有效),而信号使得被寻址的片外PAM略过片刻后把数据送上P0 口总线⑥,当而回到高电平后⑦,P0总线变为悬浮状态。至此,读片外RAM周期结束。

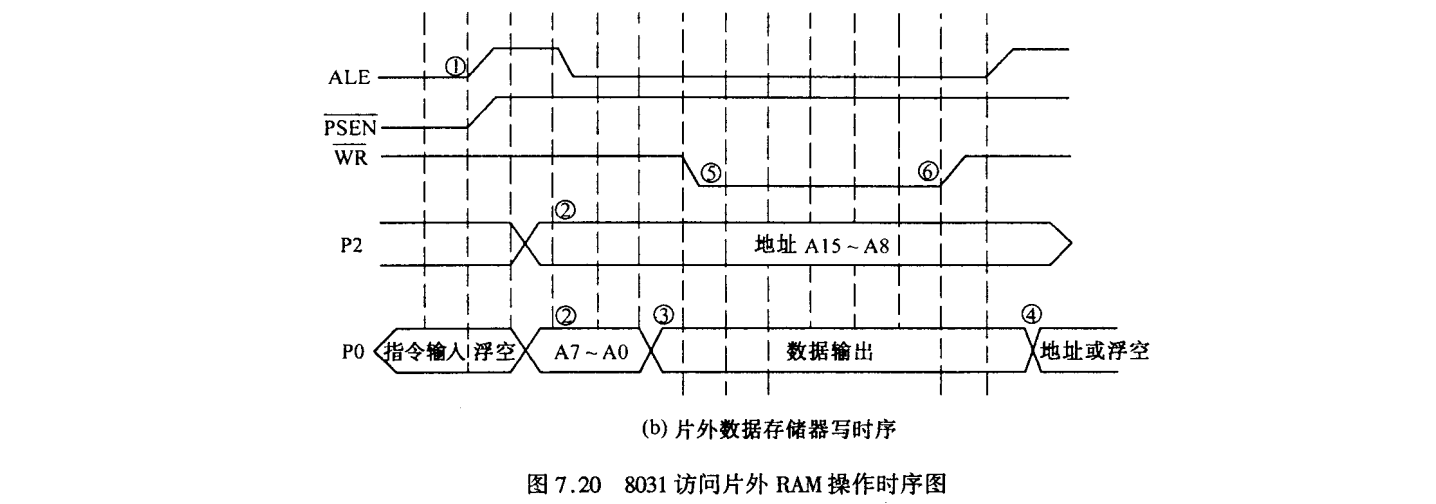

写片外RAM操作时序

向片外RAM写(存)数据,是8031执行“MOVX @DPTR,A”指令后产生的动作。这条指令执行后,在8031的WR引脚上产生WR信号有效电平,此信号使RAM的WE端被选通。

写片外RAM的时序如图7.20(b)所示。开始的过程与读过程类似,但写的过程是CPU主动把数据送上P0 口总线,故在时序上,CPU先向P0总线上送完低8位地址后,在S3状态就将数据送到P0总线③。此间,P0总线上不会出现高阻悬浮现象。

在S4状态,写控制信号WR有效,选通片外RAM,稍过片刻,P0上的数据就写到RAM内了。

典型的外扩数据存储器的接口电路

扩展数据存储器空间地址同外扩程序存储器一样,由P2 口提供高8位地址,P0 口分时提供低8位地址和8位双向数据总线。片外SRAM的读和写由8031的RD(P3.7)和WR(P3.6)信号控制,片选端(CE)由地址译码器的译码输出控制。因此,SRAM在与单片机连接时,主要解决地址分配、数据线和控制信号线的连接。在与高速单片机连接时,还要根据时序解决速度匹配问题。

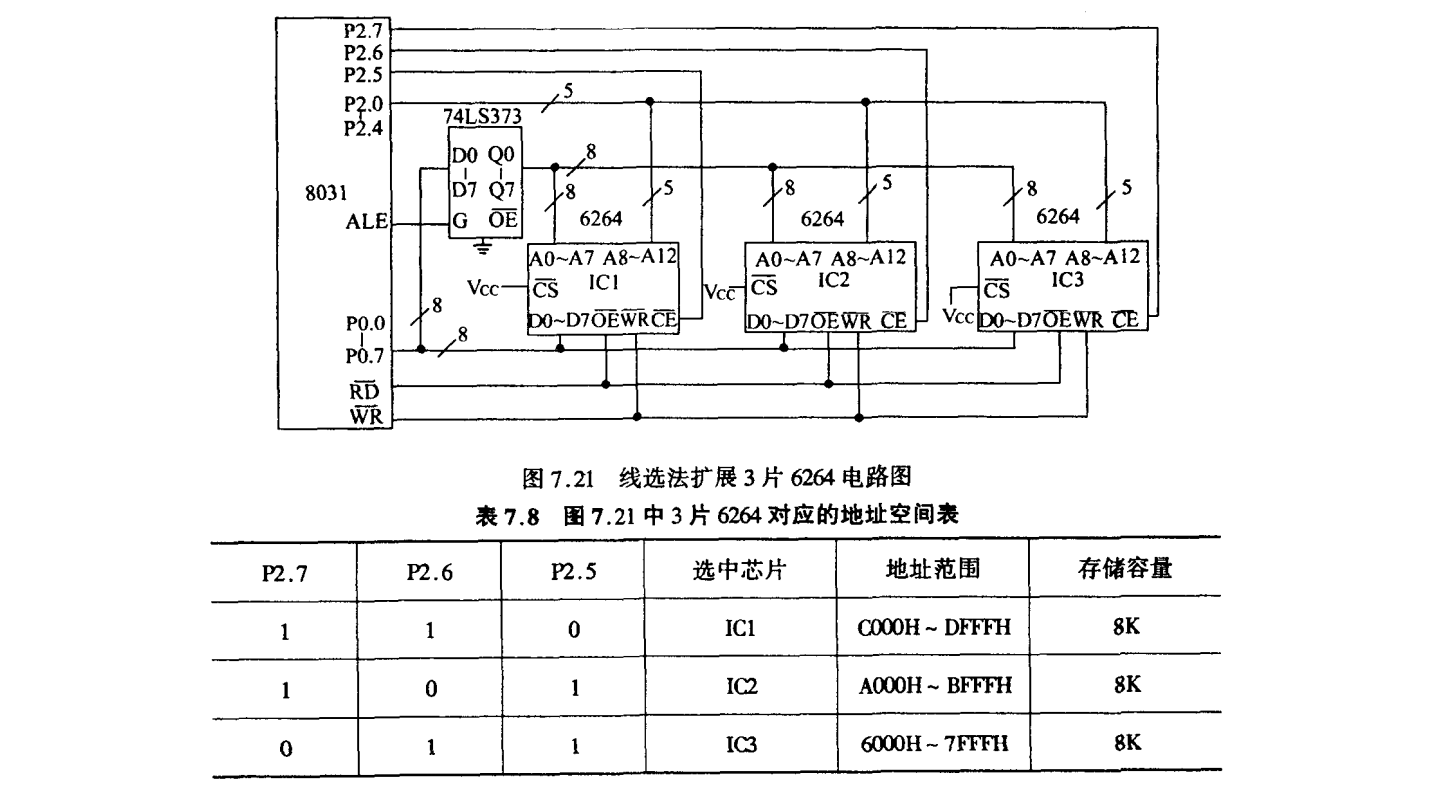

图7.21给出了用线选法扩展8031外部数据存储器的电路。图中数据存储器选用6264,该片地址为A0~A12,故8031剩余地址为三根。用线选法可扩展3片6264。3片6264对应的存储器空间见表7.8所示。

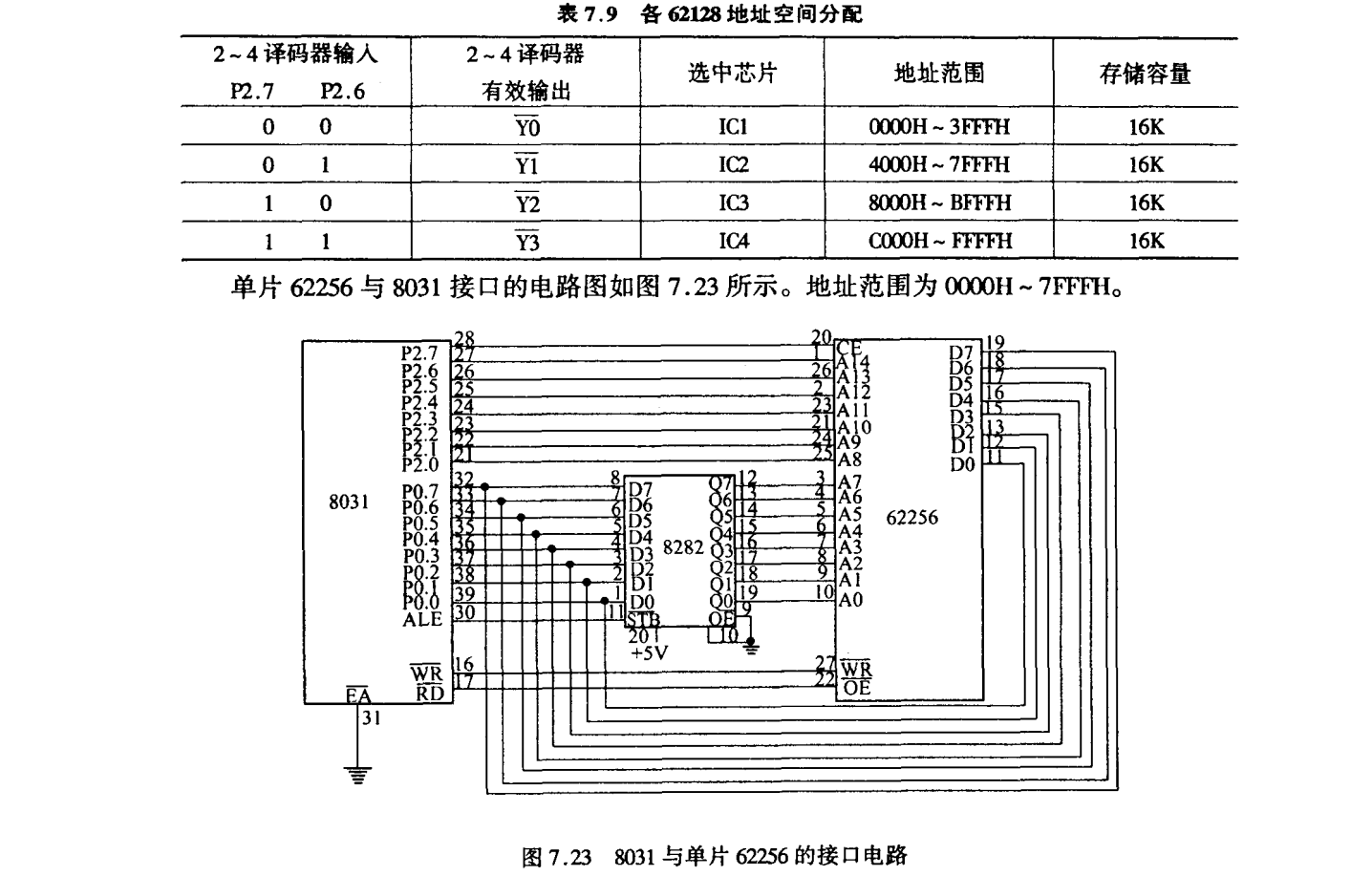

用译码选通法扩展8031的外部数据存储器电路如图7.22所示。图中数据存储器选用62128,该芯片地址线为A0~ A13,这样8031剩余地址线为两根,若采用2~4译码器可扩展4片62128。各个62128地址分配见表7.9。

EPROM和RAM的综合拓展

在单片机应用系统设计中,经常是既要扩展程序存储器(EPROM)也要扩展数据存储器(RAM),即存储器的综合扩展。下面介绍如何进行综合扩展。

综合扩展的硬件接口电路设计

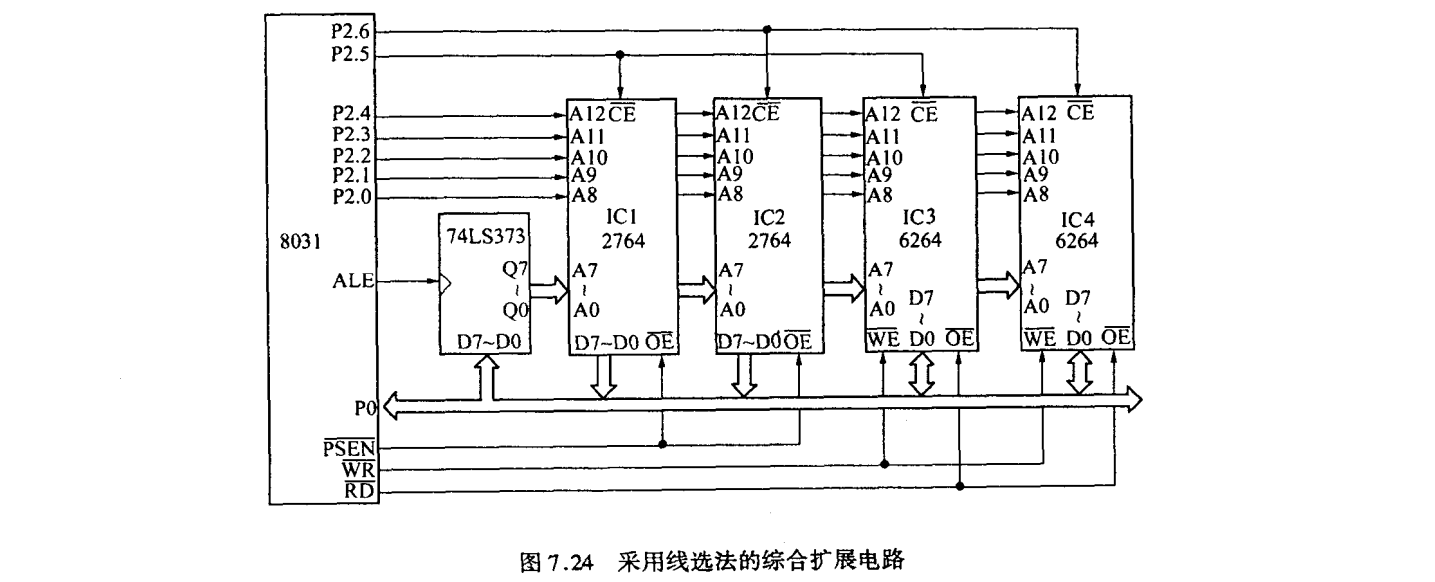

例7.2采用线选法扩展2片8KB的RAM和2片8KB的EPROM。RAM芯片选用2片6264,EPROM芯片选用2片2764,共扩展4片存储器芯片。扩展接口电路见图7.24。

控制信号及片选值号

地址线P2.5直接接到IC1(2764)和IC3(6264)的片选反端,P2.6直接接到102(2764)和104(6264)的片选而端。当P2.6 = 0,P2.5 = 1,IC2和IC4型片选端CE低电平,IC1和IC3的CE端全为高电平。

当P2.6=1,P2.5 = 0时IC1和IC3的CE端都是低电平,每次同时选中两个芯片,具体哪个芯片工作还要通过PSEN、WR、RD控制线控。

当片外程序存储区读选通信号PSEN为低电平,肯定到EPROM中读程序;当读、写通信号RD或WR为低电平则到RAM中读数据或向RAM写入数据。PSEN、WR、RD三个信号是在执行指令时产生的,但任一时刻,只能执行一条指令,所以只能一个信号有效,其它信号不可能同时有效。

各芯片地址空间分配

硬件电路一旦确定,各芯片的地址范围实际就已确定,编程时只要给出要选择芯片的地址,就能准确地选中该芯片。结合图7.24,介绍IC1、IC2、IC3、IC4地址范围的确定方法。

程序和数据存储器地址均用16位,P0 口确定低8位,P2 口确定高8位地址。

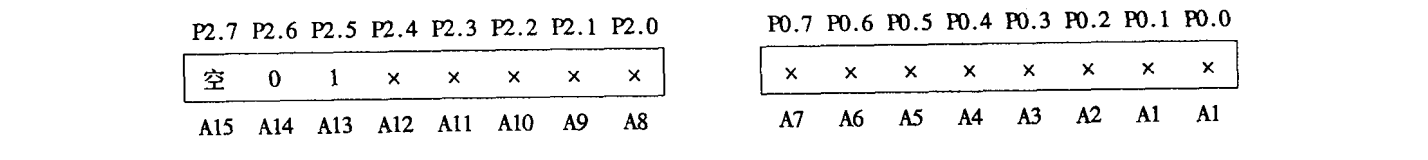

如P2.6 = 0、P2.5=1选中IC2、IC4。地址线A0-A15与P0、P2对应关系如下:

显然除P2.6、P2.5固定外,其他“ x ”位均可变。设无用位P2.7 = 0,“ x ”各位全为“0”则为最小地址2000H;若“x”位均变为”1“则为最大地址3FFFH,所以IC2和IC4占用地址空间为:2000H-3FFFH 共 8KB。

同理 IC1、IC3 地址范围 4000H~5FFFH(P2.6= l、P2.5 = 0、P2.7 = 0),IC2与IC4占用相同的地址空间,由于二者一个为程序存储器,一个为数据存储器,在控制线PSEN、WR或RD控制下,不同时工作。因此,地址空间重叠也无关系。IC1与IC3也同样。从此例看出,线选法地址不连续,地址空间利用也不充分,而且地址有重叠。

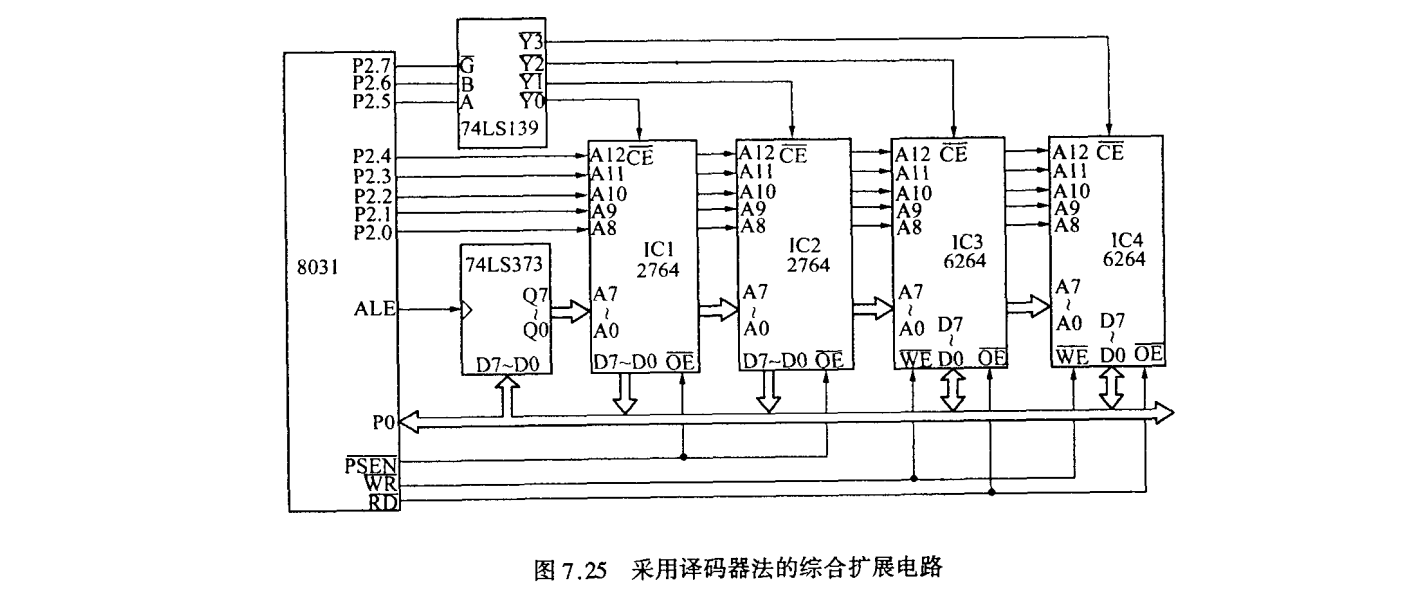

例7.3采用译码器法扩展2片8KB EPROM,2片8K BRAM。 EPROM选用2764,RAM选用6264。共扩展4片芯中。扩展的接口电路见图7.25。图中74LS139的4个输出端,Y0 ~ Y3分别连接4个芯片IC1、IC2、IC3、IC4的片选端。Y0~ Y3每次只能有一位是“0”,其他三位全为“1”,输出为“0”的一端所连接的芯片被选中。

译码法地址分配,首先要根据译码芯片真值表确定译码芯片的输入状态,由此再判断其输出端选中芯片的地址。

如图7.25所示74LS139的输入端A、B、C分别接P2接口的P2.5、P2.6、P2.7三端,召为使能端,低电平有效。根据表7.2中74IS139的真值表可见当C = 0、A = 0、B = 0时,输出端只有Y0为“0”,Y1~Y3全为1,选中IC1这样,P2.7、P2.6、P2.5全为“0”其他地址线任意状态都能选中IClo当其他全为“0”最小地址0000H,其他位全为“1”最大地址为1FFFH。

所以IC1地址范围0000H~lFFFH。

同理可确定其他芯片地址范围如下:

IC2:2000H~3FFFH

IC3:4000H-5FFFH

IC4:6000H~7FFFH

显然地址空间是连续的。