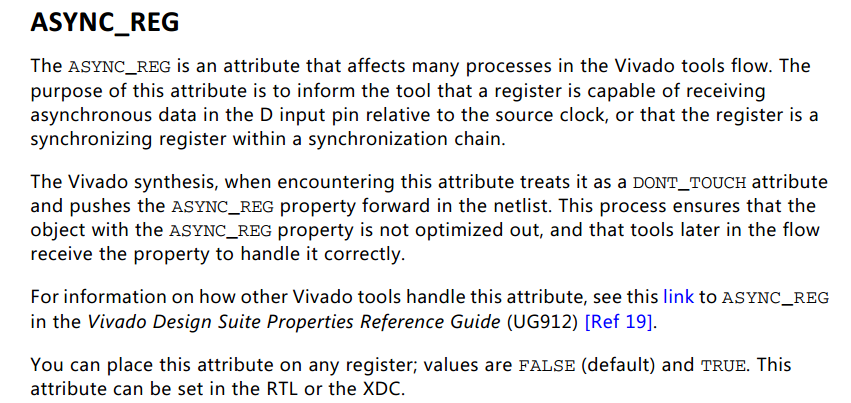

(*ASYNC_REG = "TRUE"*)命令用于声明寄存器能够接收相对于时钟源的异步数据,或者说寄存器是一个同步链路上正在同步的寄存器。这条命令可以放在任何寄存器上,除了设置它的值为TRUE外还可以设置为FALSE.

例子:(*ASYNC_REG = "TRUE"*) reg [0:0] async_rst = 0;

这样可以强制指定async_rst为异步时钟输入,防止综合器对打拍寄存器进行优化,类似DONT_TOUCH。 详情见UG901-Vivado Design Suite User Guide.pdf

module reset_sync (input clk, input reset_in, output reset_out); (* ASYNC_REG = "TRUE" *) reg reset_int = 1'b1; (* ASYNC_REG = "TRUE" *) reg reset_out_tmp = 1'b1; always @(posedge clk or posedge reset_in) if(reset_in) {reset_out_tmp,reset_int} <= 2'b11; else {reset_out_tmp,reset_int} <= {reset_int,1'b0}; assign reset_out = reset_out_tmp; endmodule // reset_sync

module cdc#( parameter DW =16 , parameter SL =3 ) ( input sys_clk , input sys_rst , input [DW-1:00] A_Din , output [DW-1:00] S_Dout ); (*ASYNC_REG="true"*)reg [DW-1:00] ccsrl_A_Din[0:SL-1]; reg [DW-1:00] ccr_A_Din ={DW{1'b0}} ; always@(posedge sys_clk) begin if(sys_rst) begin ccsrl_A_Din[SL-1] <= 1'b0 ; end else begin ccsrl_A_Din[SL-1] <= A_Din ; end end genvar i; generate for(i=0;i<SL-1;i=i+1) begin always@(posedge sys_clk) begin if(sys_rst) begin ccsrl_A_Din[i] <= 1'b0 ; end else begin ccsrl_A_Din[i] <= ccsrl_A_Din[i+1] ; end end end endgenerate always@(posedge sys_clk) begin if(sys_rst) begin ccr_A_Din <= {DW{1'b0}} ; end else begin ccr_A_Din <= ccsrl_A_Din[0] ; end end assign S_Dout =ccr_A_Din; endmodule

相关参考:

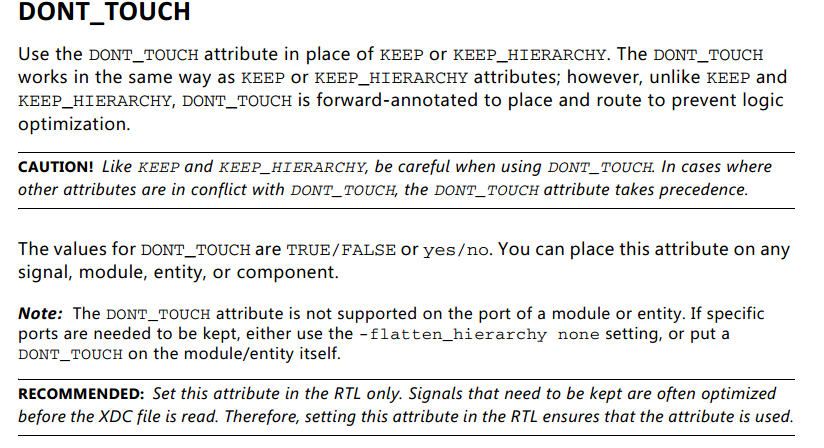

DONT_TOUCH Verilog Examples Verilog Wire Example (* dont_touch = “yes” *) wire sig1; assign sig1 = in1 & in2; assign out1 = sig1 & in2; Verilog Module Example (* DONT_TOUCH = “yes” *) module example_dt_ver (clk, In1, In2, out1); Verilog Instance Example (* DONT_TOUCH = “yes” *) example_dt_ver U0 (.clk(clk), .in1(a), .in2(b), .out1(c));