7series 逻辑单元理解

ug768和ug799文档介绍了7系列芯片中包含的基本逻辑单元,对其中常用的单元,进行下分析。

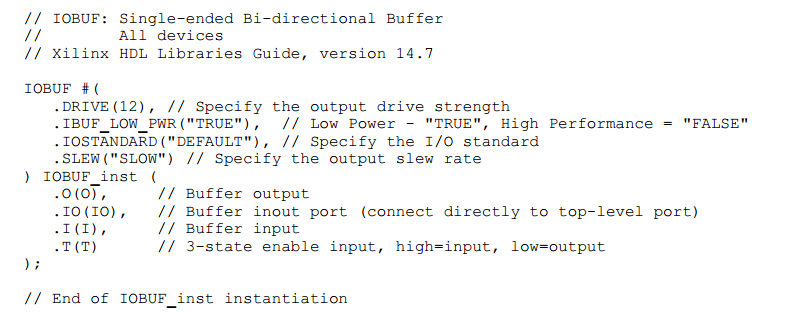

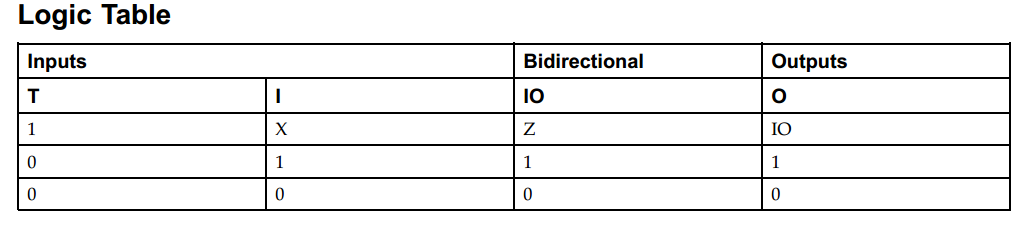

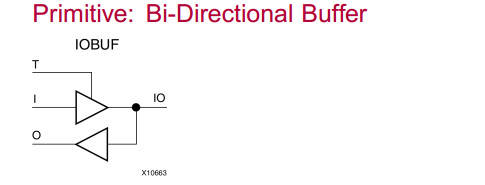

1、IOBUF单元

(1)真值表

(2)用途

the design element is a bidirectional single-ended I/O Buffer used to connect internal logic to an external bidirectional pin.

(3)属性

(4)模型

(5)心得体会

IOBUF作为FPGA内部逻辑与外部逻辑的接口,通常被打包成多bit进行使用;与CPLD一样,可以直接使用assign out = sel ? internal : 'dZ ,编译器综合成此模块。

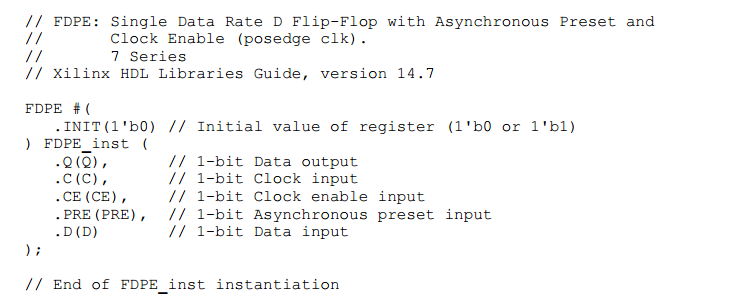

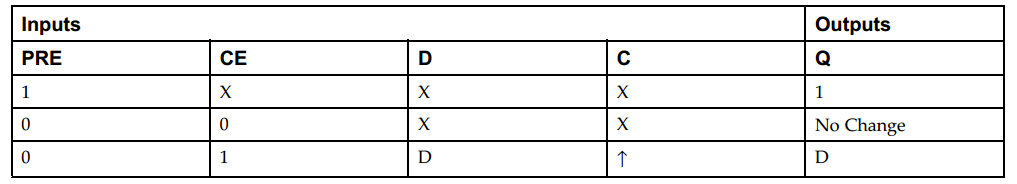

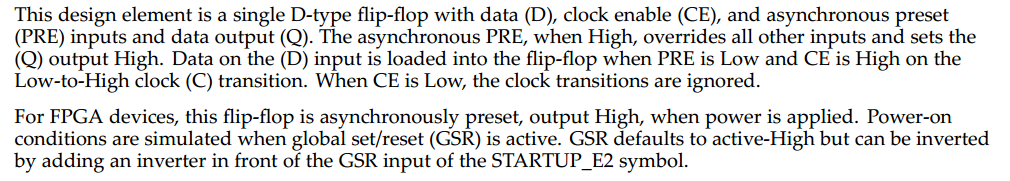

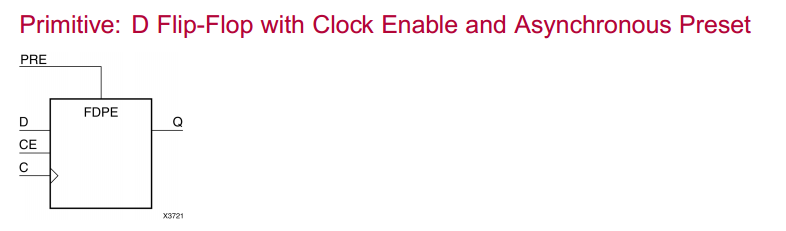

2、FDPE单元

(1)真值表

(2)用途

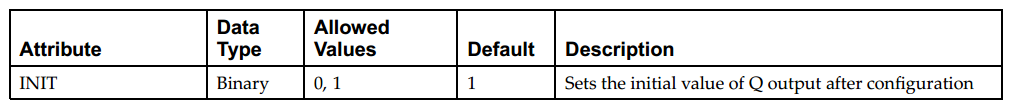

(3)属性

(4)模型

。

(5)心得体会

FDPE作为带有异步预置位的DFF,一般用作复位电路中,可以作为MMCM中不同时钟域中复位的输出。参看《Xilinx FPGA复位逻辑处理小结》

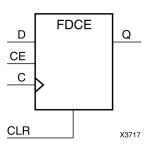

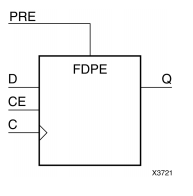

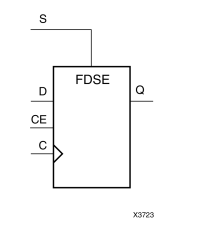

3、FDCE/FDPE/FDRE/FDSE区别:

| FDCE | FDPE | FDRE | FDSE | |

| 名称含义 | C:asynchronous clear | P: asynchronous preset | R: synchronous reset | S: synchronous set |

| 时钟域 | 异步 | 异步 | 同步 | 同步 |

| 常见用途 | always@(posedge clk or posedge rst ) | 作为跨时钟域复位处理单元 | ||

| init属性作用 | set the initial value of Q output after configuration,指的是配置好FPGA逻辑后的Q初值。 |

|||

| 符号 |

|

|

|

|

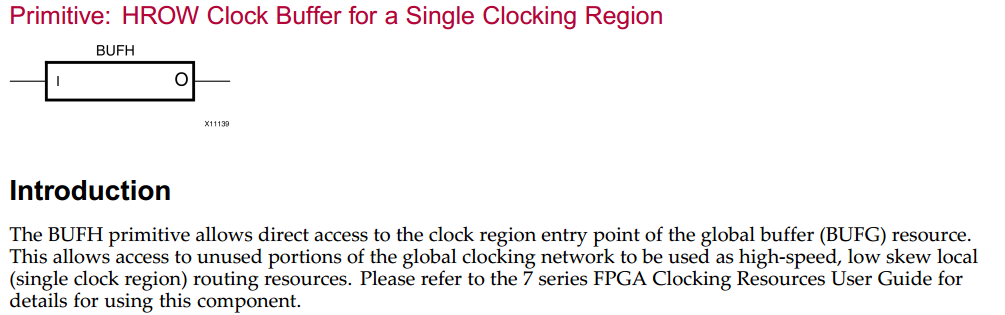

4、BUFG、BUFR、BUFIO、BUFH、BUFMR、IBUFG、GTs

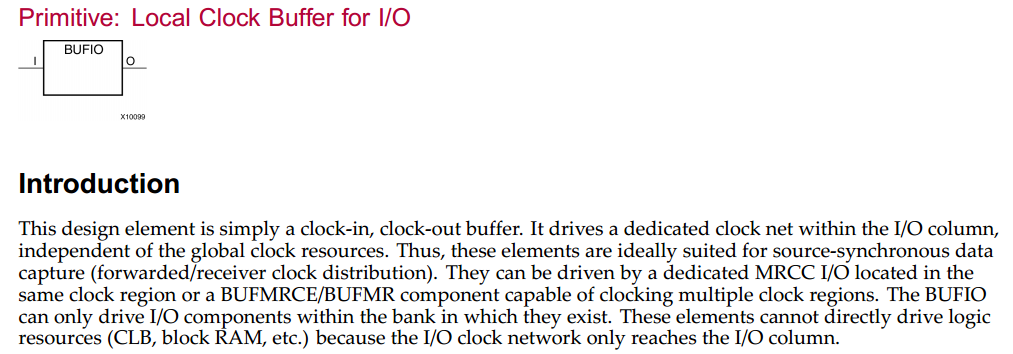

BUFIO:只能驱动I/O,不能驱动逻辑资源(CLB/RAM等);只能驱动这个BUFIO存在的BANK里的I/O;

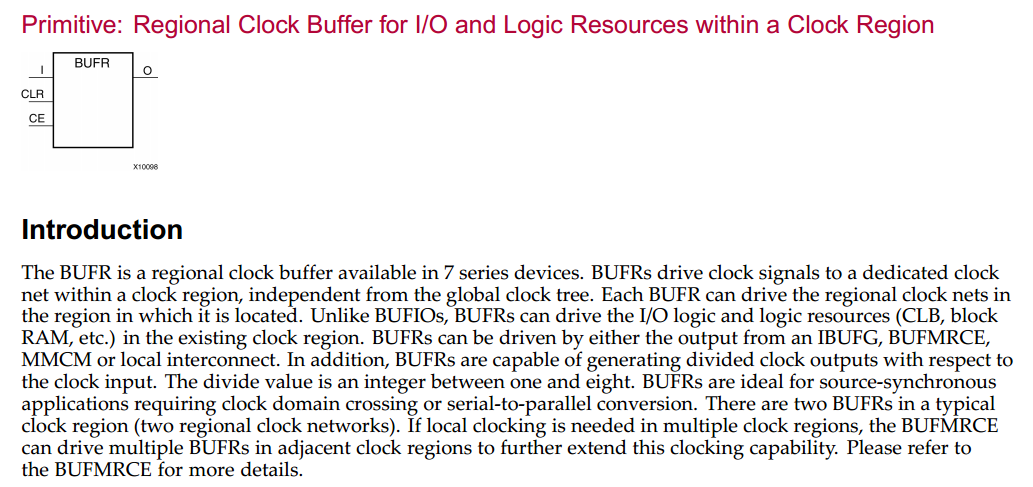

BUFR: 作为同一时钟域下,区域时钟缓冲器,驱动I/O和逻辑资源;