*Dynamic Reconfiguration Port(DRP)

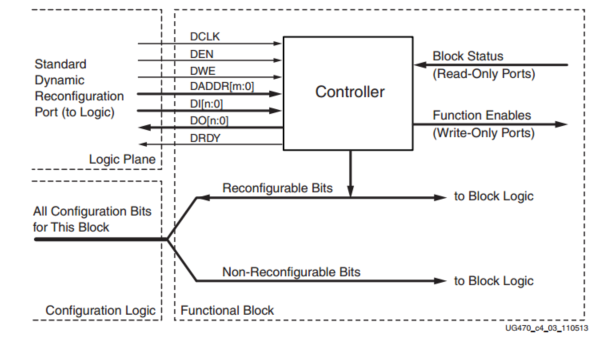

动态重配置端口:在7系列FPGA中,配置存储器主要用于实现用户逻辑,连接和I / O,但它也用于其他目的。 例如,它用于指定功能块中的各种静态条件,例如时钟管理块(CMT)。有时,应用程序需要在功能块运行时更改功能块中的这些条件。 这可以通过使用JTAG,ICAPE2,串行或SelectMAP端口进行部分重配置来实现。 但是,动态重配置端口(DRP)是许多功能块的组成部分,这样可以极大地简化配置过程。 这些配置端口存在于CMT,MMCM / PLL,XADC,串行收发器和PCIe®模块(非I / O)中。

早期不具备DRP端口的功能模块:

具备DRP端口的功能模块:

DRP端口描述:

| 信号名称 | 方向 | 描述 |

| DCLK | 输入 | 时钟上升沿采样 |

| DEN | 输入 | 使能所有端口操作 |

| DWE | 输入 | 低电平读使能;高电平写使能 |

| DADDR[m:0] | 输入 | 读写操作的目的地址 |

| DI[n:0] | 输入 | 写操作输入 |

| DO[n:0] | 输出 | 读操作输出 |

| DRDY | 输出 | 读写操作必须在DRDY=1状态下 |