做嵌入式开发,经常需要通过逻辑分析仪对数字信号进行数据分析。如果信号源附近有强干扰源,并且逻辑分析仪滤波效果不好的话,获取到的数字信号,经常带有一些“毛刺”,这些“毛刺”信号根据干扰的强弱不同,持续时间可能会由几纳秒到几百纳秒不等。尝试过在数字口加电容进行硬件滤波,电容加得太小,滤波不干净;电容加得太大,信号失真严重。

通过观察逻辑分析仪获取到的波形可以看到,干扰信号一般是在信号跳变之后的一小段时间内出现(这是我所遇到的信号的情况),如下图1所示信号由低变成高,2us内,都是干扰信号。实际上前面2 us内的电平信号应该是高电平。软件滤波的目的,就是要将干扰信号还原成它原来的电平。

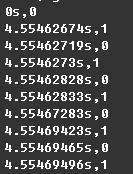

先将逻辑分析仪获取到的数据,转成csv格式的文件,命名为src_data.csv。src_data.csv 文件记录的是每个信号跳变瞬间的时间和对应的电平状态(0或1),如下图2为src_data.csv的格式。

如果没有逻辑分析仪,也可以通过将其他途径获取到的数据,以类似的格式保存。

实现算法:

1. 将信号产生的时间,转换成统一的计时单位。

2. 截取每一个信号周期内高电平和低电平所占的时间。并按照信号产生的顺序,依次存放在同一个列表(信号描述表)中。

3. 遍历一遍信号描述列表,把小于xxns的低电平都认为是干扰信号。把这个低电平持续的时间,加到上一个高电平持续的时间里,并把这个低电平从列表中去掉。

4. 遍历一遍信号描述表,把可能连续出现的连续相同电平合并。此时,信号描述表中的元素,都是按照高低高低这样的排列。

源码地址如下:https://git.oschina.net/liujiangyi123/digital_signal_filter/blob/master/digital_signal_filtering.py