Verilog IIC通信实验笔记

Write by Gianttank

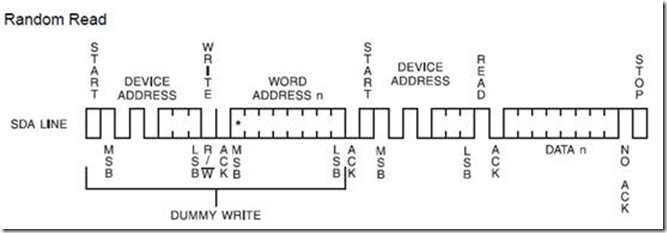

我实验的是 AT24C08的单字节读,单字节写,页读和页写,在高于3.3V系统中他的通信速率最高400KHZ的,我实验里用的是100KHZ的速率。图1是硬件原理图![clip_image002[5] clip_image002[5]](https://images.cnblogs.com/cnblogs_com/gianttank/WindowsLiveWriter/VerilogIIC_C9AE/clip_image002%5B5%5D_thumb.jpg)

图1

图2

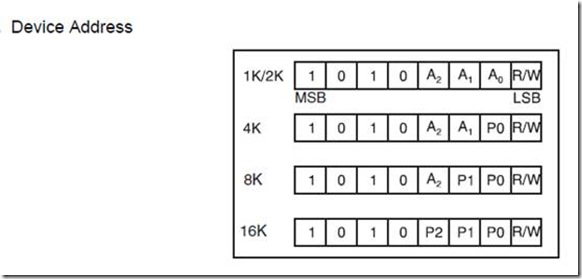

图2是器件地址,我的原理图是A2接高。

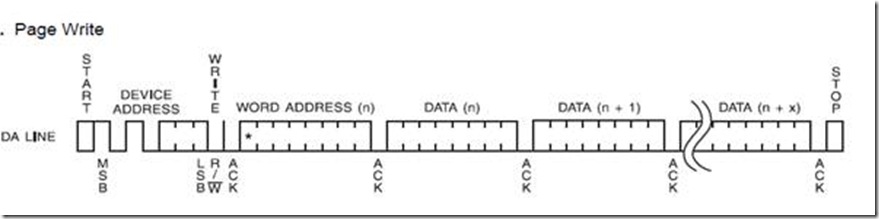

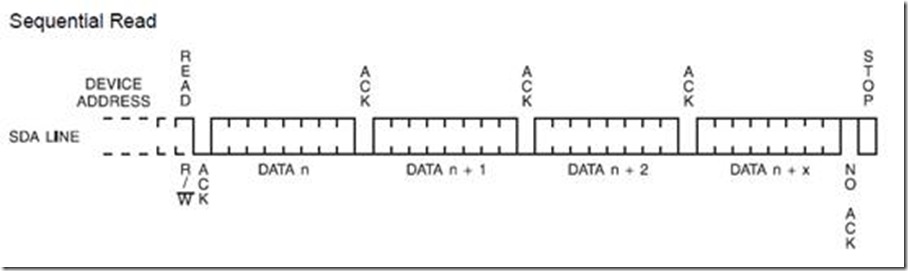

IIC通信协议中要注意的地方:

1. 当时钟线SCL 高电平时,如果把数据线SDA 从高电平拉到低电平,则表示通信开始(START);如果把数据线SDA 从低电平拉到高电平,则表示通信结束(STOP)。SDA数据不变,视为数据采样。

2. 前一个STOP 结束后。与下一个START开始要保证5ms的间隔。

3. 页写有字节限制,而页读没有,可以一次读出所有的数据。

4. SDA信号在FPGA为接受方时要设置为高阻态。

5. 应答信号永远是接收方发送的,这个很重要,我就是卡在这里几天没找到原因。FPGA在读数据的时候,第9个周期是FPGA发低电平给EEPROM的。

图3

引脚定义

|

信号名称 |

方向 |

描述 |

|

clk |

50M的主时钟 |

|

|

rst_n |

input |

复位信号 |

|

sw1 |

input |

|

|

sw2 |

input |

按键2 低电平有效 按下执行字节读 |

|

sw3 |

input |

|

|

sw4 |

input |

按键4 低电平有效 按下执行页写 |

|

SDA |

inout |

IIC数据端口 |

|

SCL |

IIC时钟端口 |

|

|

leddata |

output |

数码管段选 |

|

ledcom |

output |

数码管位选 |

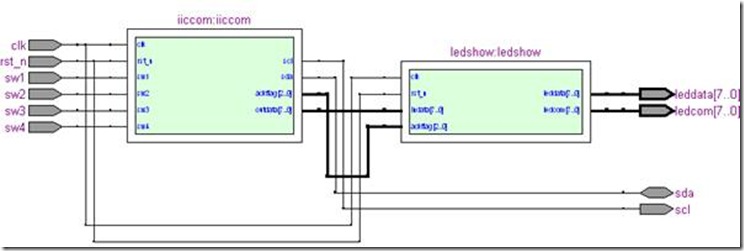

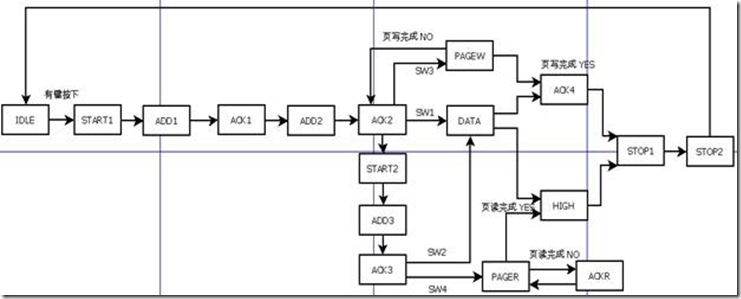

代码中分了两个模块,iic_com 模块除了执行和I2C 通信有关的代码设计外,还有按键检测部分,而ledshow 模块只是驱动数码管显示读出的数据。对于这个通信的过程,内部使用了一段式状态机进行设计。图4是状态机的状态图。具体每个状态见程序。

图4

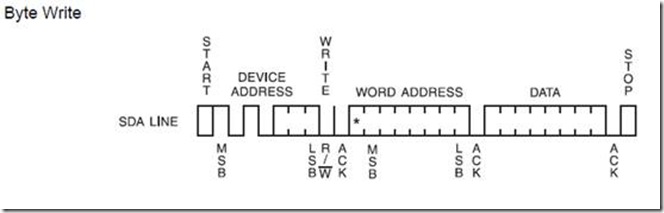

1.字节写

图5

蓝色为sda数据线高阻态,fpga接受eeprom应答。写入数据88h。

2.字节读

图6

3.页写

图7

因为我只有8个数码管,所以我程序里的页写,页读都只有4个数据。

可以看到写入数据位21h,43h,65h,87h。

4.页读

图8

Modelsim后仿真的图

这里就是 应答是fpga应答给eeprom的。

最后希望这篇文档能帮助对IIC协议还不够了解的同学。

源程序在下一篇文章中。