半加器:

//行为级建模

module half_adder2(a, b, sum, c_out);

input a, b;

output sum, c_out;

assign {c_out, sum} = a + b;

endmodule

// 结构级建模

module half_adder(a, b, sum, c_out);

input a, b;

output sum, c_out;

xor (sum, a, b);

and (c_out, a, b);

endmodule

进位选择加法器:

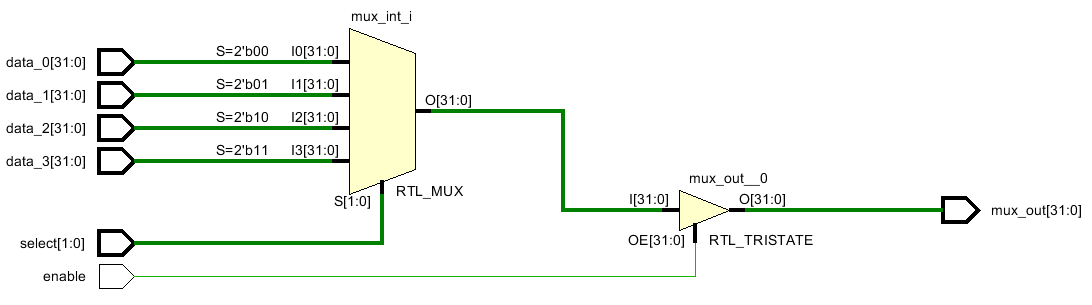

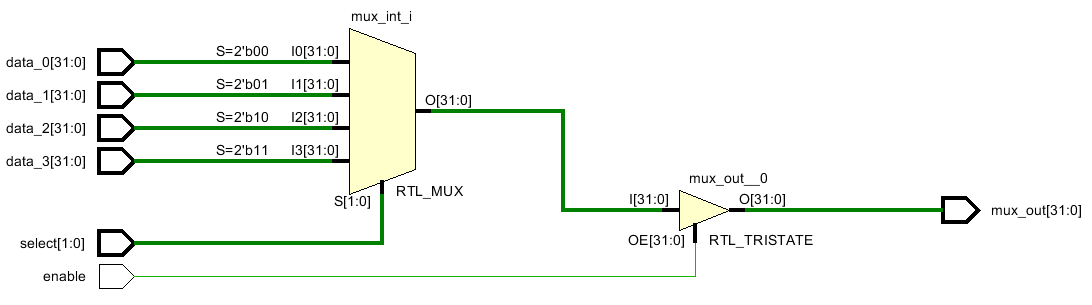

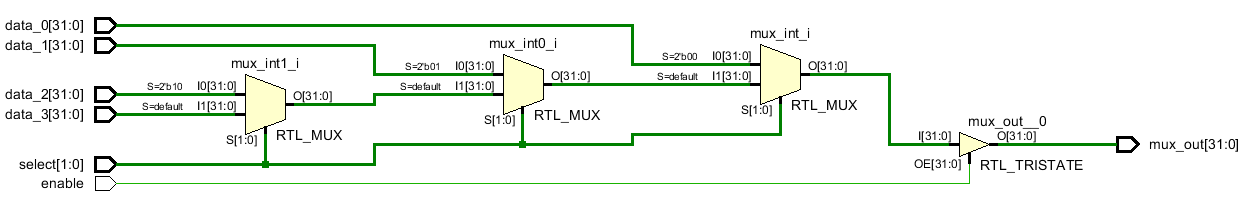

多路复用器:

//行为模型

module Mux_4_32_case(

output [31:0] mux_out,

input [31:0] data_3, data_2, data_1, data_0,

[1:0] select,

input enabel

);

reg [31:0] mux_int;

assign mux_out = enable ? mux_int : 32b'z;

always @ (data_3, data_2, data_1, data_0, select)

case (select)

0: mux_int = data_0;

1: mux_int = data_1;

2: mux_int = data_2;

3: mux_int = data_3;

default: mux_int = 32b'x; //当select包含z or x时的状态,不加default vivado综合出来的电路图没有区别,但是不知道在tb上会不会出问题

endcase

endmodule

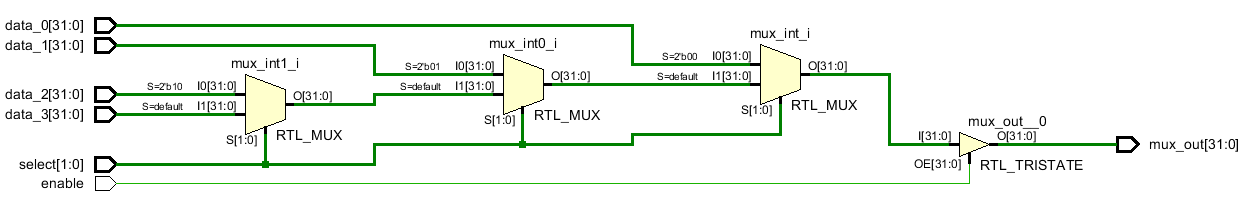

//使用if条件语句行为级建模

module Mux_4_32_if(

output [31:0] mux_out,

input [31:0] data_3, data_2, data_1, data_0,

input [1:0] select,

input enable

);

reg [31:0] mux_int;

assign mux_out = enable ? mux_int : 32'bz;

always @(data_3, data_2, data_1, data_0, select)

if(select == 2'b00) mux_int = data_0; else

if(select == 2'b01) mux_int = data_1; else

if(select == 2'b10) mux_int = data_2; else

if(select == 2'b11) mux_int = data_3; else

mux_int = 32'bx;

endmodule

module Mux_4_32_CA(

output [31:0] mux_out,

input [31:0] data_3, data_2, data_1, data_0,

input [1:0] select,

input enable

);

wire [31:0] mux_int;

assign mux_out = enable ? mux_int : 32'bz;

assign mux_int = (select==0) ? data_0:

(select==1) ? data_1:

(select==2) ? data_2:

(select==3) ? data_3: 32'bx;

endmodule

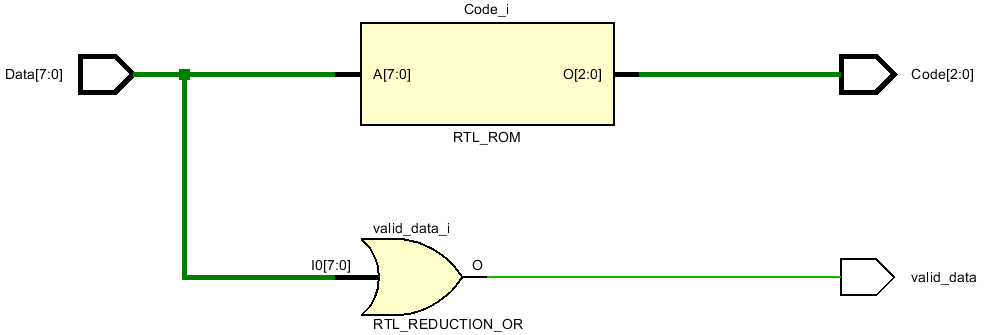

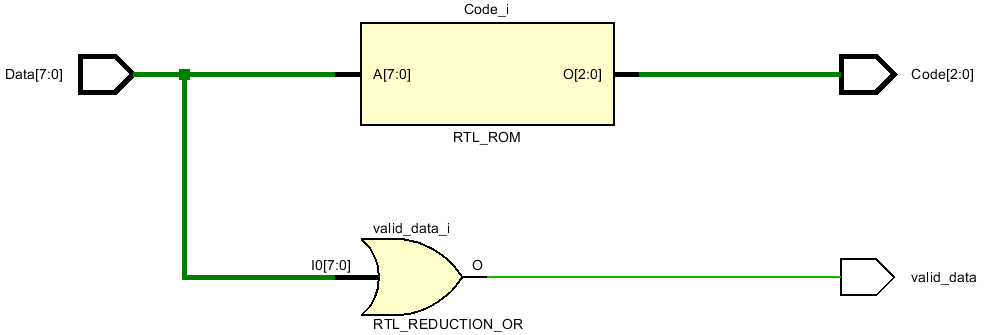

编码器

//case 优先编码器

module priority_case(

output reg [2:0] Code,

output valid_data,

input [7:0] Data

);

assign valid_data = |Data; //“reduction or" operator

always @(Data)

casex (Data)

8'b1xxxxxxx : Code = 7;

8'b01xxxxxx : Code = 6;

8'b001xxxxx : Code = 5;

8'b0001xxxx : Code = 4;

8'b00001xxx : Code = 3;

8'b000001xx : Code = 2;

8'b0000001x : Code = 1;

8'b00000001 : Code = 0;

default : Code = 3'bx;

endcase

endmodul