内容:

静态时序分析的概念与目的

与时钟相关的时序特性

静态时序分析(Statistic)

https://blog.csdn.net/u013668469/article/details/98033000 时钟sdc

静态时序分析的概念和目的

时序路径与关键路径

时序路径:是一个点到另一个点的数据通路,数据沿着时序路径进行传递,每条时序路径有一个起点(Startpoint)和一个终点(Endpoint)。

起点可以是:数据输入端口,触发器或寄存器的时钟引脚。

终点可以是:数据输出端口,时序器件的除时钟引脚外的所有输入引脚。

因此时序路径可以是数据输入端口到寄存器、寄存器到寄存器、寄存器到输出端口、输入端口到输出端口。

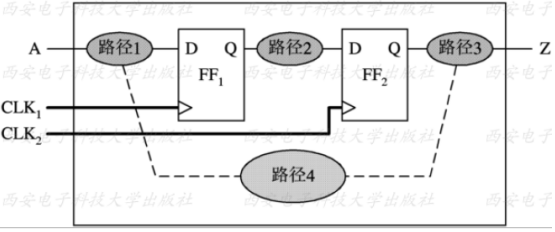

如下图电路中存在4条路径:

- 从输入端口A到FF1的D端;

- 从FF1的CLK端到FF2的D端;

- 从FF2的CLK端到输出端口Z;

- 从输入端口A到输出端口Z。

一般情况下,路径1、2、3是最常见的,路径4比较少见。???

关键路径:路径的特性是存在延时,其中延时最长的一条称为关键路径。

常见的时序路径约束

在进行约束前,需要了解触发器的三个概念:建立时间、保持时间和亚稳态。这里简单介绍这三个概念,更深入的介绍见《笔试题》、《亚稳态》。

建立时间指的是在时钟有效沿来之前数据必须保持稳定的一段时间,否则触发器锁存不住数据,用Tsu表示。

保持时间指的是在时钟有效沿来之后数据仍需保持稳定的一段时间,否则触发器锁存不住数据,用Th表示。

亚稳态:半导体厂商在工艺库中规定了每个触发器的建立时间和保持时间参数。如果数据在建立时间和保持时间中被采样,那么其输出是不可预知的,有可能是0,也有可能是1,这种未知的状态称为亚稳态。

了解这三个概念后,就可以对路径进行约束。约束的目的就是为了确定寄存器是否满足建立时间(和保持时间)。

与时钟相关的时序特性

时钟的时序特性主要分为抖动(Jitter)、偏移(Skew)和占空比失真(Duty Cycle Distortion)三种。在低速设计中不需要考虑这些时序特性;但是在告诉设计中,由于这三种特性会造成普遍的时序问题。

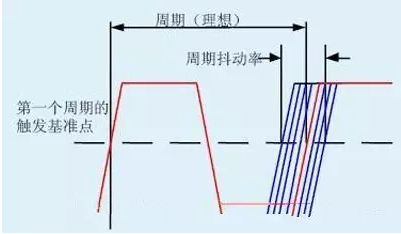

(1)时钟抖动

定义:理想时钟信号应该是理想的方波,但是现实中的时钟边沿不可能是瞬时变化的,有一个从高到低/从低到高的变化过程;同时存在噪声的原因,实际的时钟与理想时钟的长度存在必然的偏差。

分类:

周期抖动(Period Jitter):一个实际周期的长度与一个理想周期的最大时间偏差。

周期差抖动(Cycle-to-cycle Jitter):两个相邻周期之间周期长度的偏差,总是小于周期抖动。

长期抖动(Long-term Jitter):一个时钟沿相对于基准周期时钟沿经过一段时间的延迟之后,与基准时钟边沿的偏离。

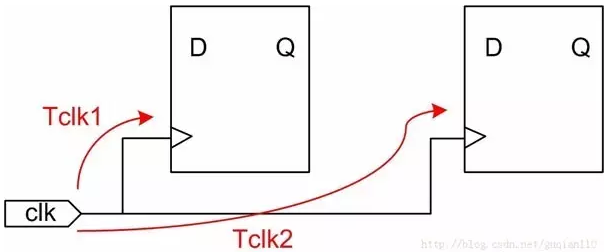

(2)时钟偏移(clock skew)

定义:时钟信号需要给整个电路的时序单元提供信号,但是由于时钟与各时序单元的距离,时序单元的负载等因素,导致同一个时钟信号到达不同的时序单元的时间存在差异(永远存在)。

上图时钟偏移计算公式:Tskew=Tclk2-Tclk1,Tskew为时钟到达寄存器D2相对于到达寄存器D1的时钟偏移。

(3)占空比失真DCD(Duty Cycle Distortion)

定义:通常是由于信号的posedge和negedge时序不同造成的,时钟信号在一个周期中保持高电平的时间不符合时钟占空比。

问题:DCD会导致吞噬大量的时序裕量,造成数字信号的失真,使过零区间偏离理想的位置。

静态时序分析常见面试题

- 什么是STA?静态时序分析,不需要向量去激活某一路径,而是对所有时序路径进行错误分析。

- 什么是data arrival time?输入数据在有效时钟沿后到达所需要的时间,分为时钟到达寄存器时间,寄存器输出延时和数据传输延时。

- 什么是required time?

- 什么是slack?

- STA中有哪些data path?input2reg,reg2reg,reg2output,input2output。

- 有哪些timing constranints exceptions?false path,multi cycle path,min/max path。

- 什么是clock latency?clock latency可以分为source latency和network latency,source latency是源时钟到芯片clock输入端的延迟;network latency是芯片clock输入端到flip flop clock输入的延迟。

- 什么是clock skew?来自同一个source clock到不同FF的时钟端的延迟之差。

- 什么是uncertainty?由于时钟抖动Jitter和时钟偏移Skew导致的时钟相对于理想位置的偏差。

- 什么是cell delay或propagation delay?

- 什么是net delay?

- 什么是drive strength?描述cell对其输出端上负载电容的充放电能力。

- 什么是门控时钟(clock gating)?是通过额外逻辑来修建时钟树,从而降低同步设计中的功耗。