原理介绍

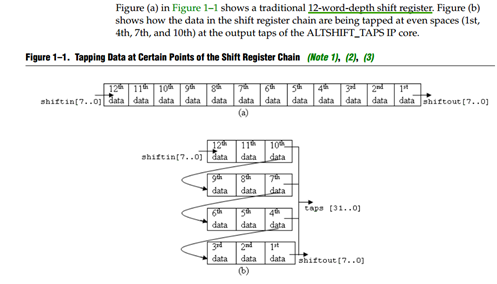

The ALTSHIFT_TAPS IP core supports single-bit and multiple-bit data shifting at one

clock cycle, depending on the width of the shiftin and shiftout ports. For example,

if the shiftin and shiftout ports are single-bit data, only one bit is shifted per clock

cycle. If the shiftin and shiftout ports are multiple-bit data, such as one-word data

(8-bit), the whole word is shifted per clock cycle.

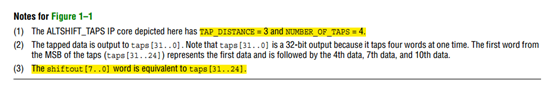

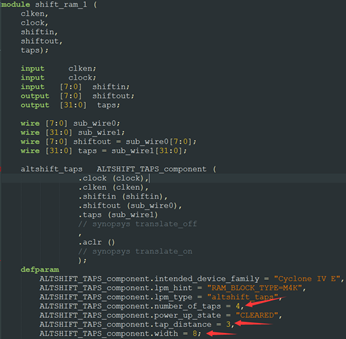

Shift_ram能够通过shiftin设置移位输出的位宽,TAP_DISTANCE 设置每行数据单元个数;

NUMBER_OF_TAPS设置抽头的数量;

TAP_DISTANCE = 3;表征每行有3个数据单元;

NUMBER_OF_TAPS = 4.;表征有4列,即抽头的数量;

将每一行的抽头输出就形成了taps,shiftout输出的是taps的高位数据单元;

实例

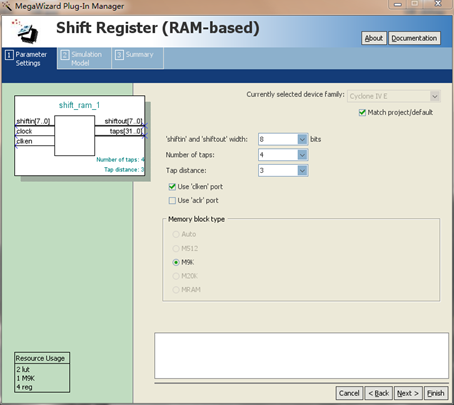

调用IP

测试数据产生模块

Modelsim仿真

仿真结果与datasheet的实例说明一致;