一、实验硬软件环境:

- EDA软件:Vivado2019

- 实验开发板:Basys3 FPGA套件

二、实验内容:

实现如下电路功能:当开关开启,灯泡轮流闪烁,间隔1s,类似跑马灯;开关关闭,则灯泡关闭。使用实验板上的按键模拟开关,led模拟灯泡,时钟使用实验板提供的clk。草靠实验板的管脚文件编写约束文

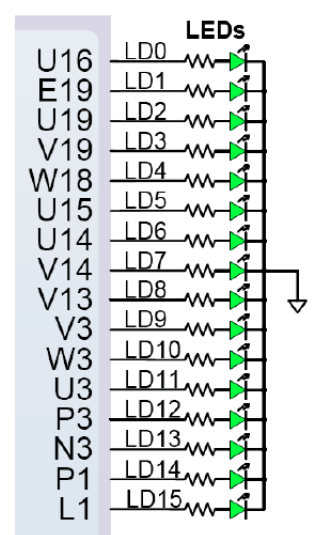

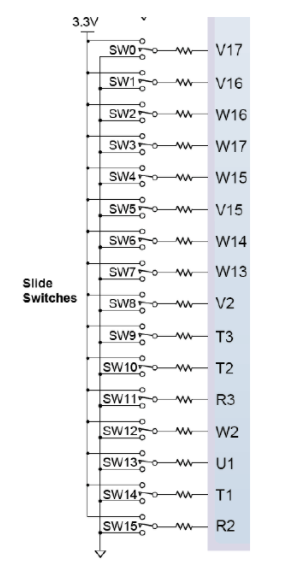

注意,LED部分的电路图如左图所示,当FPGA输出为高电平时,相应的LED点亮;否则,LED熄灭。拨码开关的电路如右图所示,当开关打到下档时,表示FPGA的输入为低电平。

三、具体实现

- 思路分析:开发板的晶振为100Mhz,则其周期为10ns,初值为0的计数器自加1到100,000,000时为1s,每隔1s时间,led灯转换一次。

- 设计源码:

View Code

View Code1 `timescale 1ns / 1ps 2 ////////////////////////////////////////////////////////////////////////////////// 3 // Company: 4 // Engineer: 5 // 6 // Create Date: 2020/09/08 14:18:09 7 // Design Name: 8 // Module Name: Marquee 9 // Project Name: 10 // Target Devices: 11 // Tool Versions: 12 // Description: 13 // 14 // Dependencies: 15 // 16 // Revision: 17 // Revision 0.01 - File Created 18 // Additional Comments: 19 // 20 ////////////////////////////////////////////////////////////////////////////////// 21 22 module Marquee(switch, clk, led); 23 input switch, clk; 24 output reg [3:0] led; 25 26 reg [28:0] count; 27 28 always @(posedge clk) 29 begin 30 if(!switch) 31 begin 32 led <= 4'b0001; 33 count <= 29'b0; 34 end 35 else 36 begin 37 if(count == 29'd100_000_000) 38 begin 39 count <= 29'b0; 40 if(led == 4'b1000) 41 led <= 4'b0001; 42 else 43 led <= (led << 1); 44 end 45 else 46 begin 47 count <= count + 1; 48 led <= led; 49 end 50 end 51 end 52 endmodule

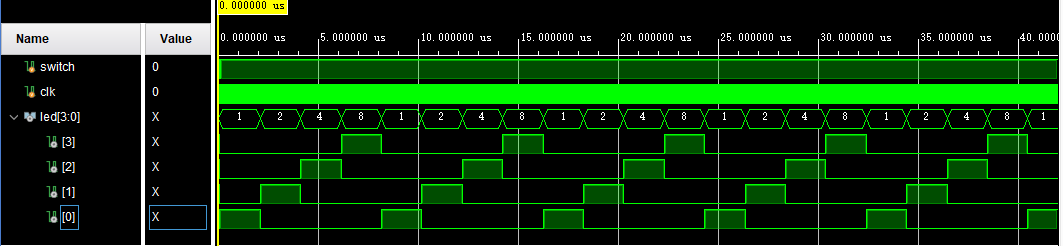

- 仿真代码:(需要注意的是,为了便于仿真,设计源码中的count设置为自加到100,而非100,000,000。)

View Code

View Code1 `timescale 1ns / 1ps 2 ////////////////////////////////////////////////////////////////////////////////// 3 // Company: 4 // Engineer: 5 // 6 // Create Date: 2020/09/08 15:42:36 7 // Design Name: 8 // Module Name: Marquee_tb 9 // Project Name: 10 // Target Devices: 11 // Tool Versions: 12 // Description: 13 // 14 // Dependencies: 15 // 16 // Revision: 17 // Revision 0.01 - File Created 18 // Additional Comments: 19 // 20 ////////////////////////////////////////////////////////////////////////////////// 21 22 23 module Marquee_tb; 24 reg switch, clk; 25 wire [3:0] led; 26 27 Marquee U_Marquee(.switch(switch), .clk(clk), .led(led)); 28 29 initial 30 begin 31 clk = 0; switch = 0; 32 33 #100 switch = 1; 34 35 #100; 36 end 37 38 always #10 clk = ~clk; 39 40 endmodule

- 波形图:

- 约束文件:

View Code

View Code1 set_property PACKAGE_PIN V17 [get_ports switch] 2 set_property IOSTANDARD LVCMOS33 [get_ports switch] 3 set_property PACKAGE_PIN W5 [get_ports clk] 4 set_property IOSTANDARD LVCMOS33 [get_ports clk] 5 set_property PACKAGE_PIN U16 [get_ports led[0]] 6 set_property IOSTANDARD LVCMOS33 [get_ports led[0]] 7 set_property PACKAGE_PIN E19 [get_ports led[1]] 8 set_property IOSTANDARD LVCMOS33 [get_ports led[1]] 9 set_property PACKAGE_PIN U19 [get_ports led[2]] 10 set_property IOSTANDARD LVCMOS33 [get_ports led[2]] 11 set_property PACKAGE_PIN V19 [get_ports led[3]] 12 set_property IOSTANDARD LVCMOS33 [get_ports led[3]]