SERDES是英文SERializer(串行器)/DESerializer(解串器)的简称,即在发送端多路低速并行信号被转换成高速串行信号,经过传输媒体,最后在接收端高速串行信号重新转换成低速并行信号。利用传输媒体的信道容量,减少所需的传输信道和器件引脚数目,提升信号的传输速度,从而大大降低通信成本。发送器和接收器完成擦划分信号的发送和接收,其中LVDS和CML是最常用的两种差分信号标准。

LVDS(Low_Voltage Differential Signaling)低电压差分信号

1994年由美国国家半导体公司提出的一种信号传输模式,是一种电平标准,LVDS接口又称RS-644总线接口,是20世纪90年代才出现的一种数据传输接口。这种技术的核心是采用极低的电压摆幅高速差动传输数据,可以实现点对点或一点对多点的连接,具有低功耗、低误码率、低串扰和低辐射等特点。标准推荐的最高数据传输速率是655Mbps

摄像机LVDS接口的输出如上图所示,即八个数据通道,每个数据通道传输的像素数据是10bit,采用双倍率采样,所以每个像素数据的传输需要5个时钟周期。串行输出。共有8个数据引脚,然后一个显示数据使能信号,一个行同步引脚,一个场同步引脚,一个备用引脚。八个数据通道,两个时钟通道。

LVDS发送芯片的输出是低摆幅差分对信号,一般包含一个通道的时钟信号和几个通道的串行数据信号。由于LVDS发送芯片是以差分信号的形式进行输出,因此,输出信号为两条线,一条线输出正信号,另一条线输出负信号

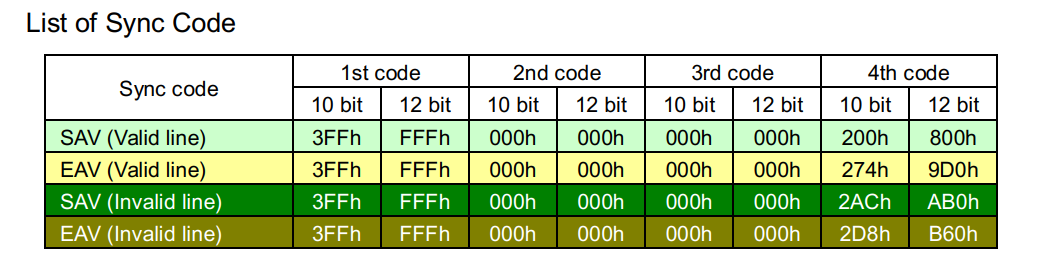

LVDS接收端:首先需要将输出的串行数据解串,这就需要用到同步码,同步用来帮助恢复正确的并行数据。

硬件实现:

1.需要设定参数,比如有几个通道以及每个数据是几比特的。然后就知道解串后输出的并行数据位宽。

2.需要将输入的差分信号转换成正常信号,这就需要调用FPGA原语IBUFDS,和IBUFGDS(这个主要用于时钟)而且需要对输入的时钟做一个缓存(调用BUFIO原语),产生一个慢时钟,是原时钟的五分之一(调用BUFR原语)

最先进入的数据再Q8输出。由于需要传输的数据是十位的,所以需要两个串并转换器进行级联。

完成数据的输入后,需要将传进来的数据进行一个解码,还原成输入时的形式。

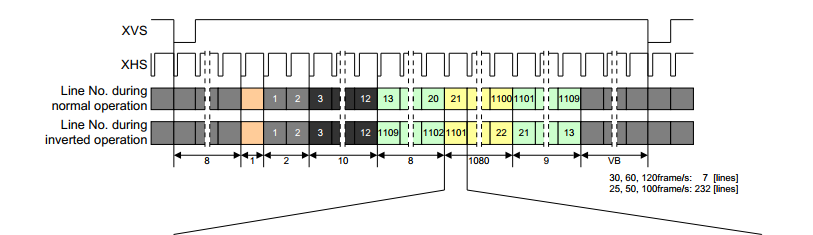

在接收模块还包括:行同步信号常用HS,场同步信号常用VS,数据使能信号。

然后接收到的数据需要解码,还原成传输过来的信号。有效信号开始的对齐码的一个FLAG,有效信号结束的一个对齐码的一个FLAG。无效信号开始的一个FLAG,(这个FLAG就是根据连续输入的信号跟同步码相同)