第一步:安装。

参考下面的链接,Cadence OrCad Allegro SPB 16.6 下载及安装破解指南

http://www.mr-wu.cn/cadence-orcad-allegro-spb-16-6-install-crack-hotfix/

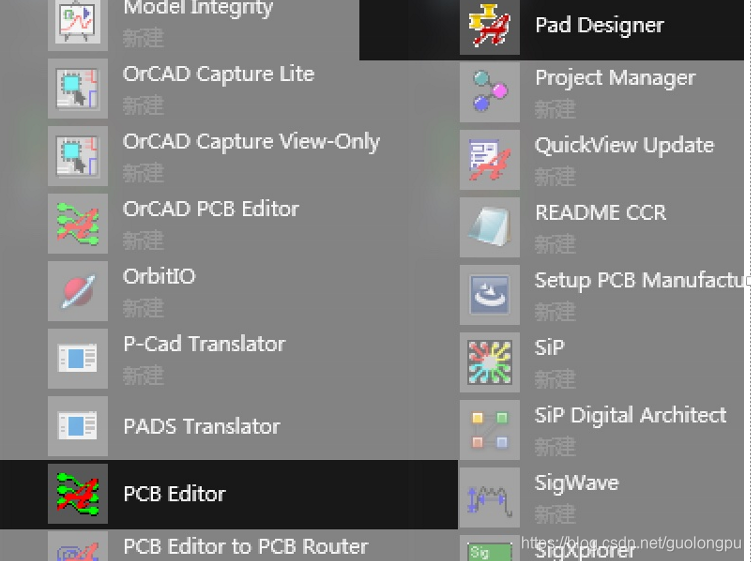

第二步:打开程序

Cadence SPB 程序安装完毕后,并不会像其他EDA软件一样,在桌面生成快捷图标。

需要进入-》开始菜单->所有应用->Cadence 选项文件夹内,通过鼠标点击对应的图标启动程序。

第三步:说明

Cadence SPB 的组件非常多,新手们往往不知道需要点击哪些图标可以做哪些事情。

本文只介绍对于新手来说会经常用到程序组件,

而其他的程序组件会随着Cadence软件的深入使用再逐步进行了解,

这样会显著降低我们的入门学习曲线。

DB Doctor:修复Allegro板子数据库错误的工具

Design Entry CIS:原理图设计工具

PCB Editor:PCB设计工具

Pad Designer:Allegro PCB封装焊盘栈设计工具

由于开始菜单里Cadence相关的图标众多,每次启动软件都要到开始菜单里找图标,显然是一件非常费眼神的事情,我们可以通过鼠标左键按住图标,将其拖至桌面,便会在桌面上自动创建一个对应的快捷图标,以后自己在桌面上双击对应的快捷图标即可启动程序。

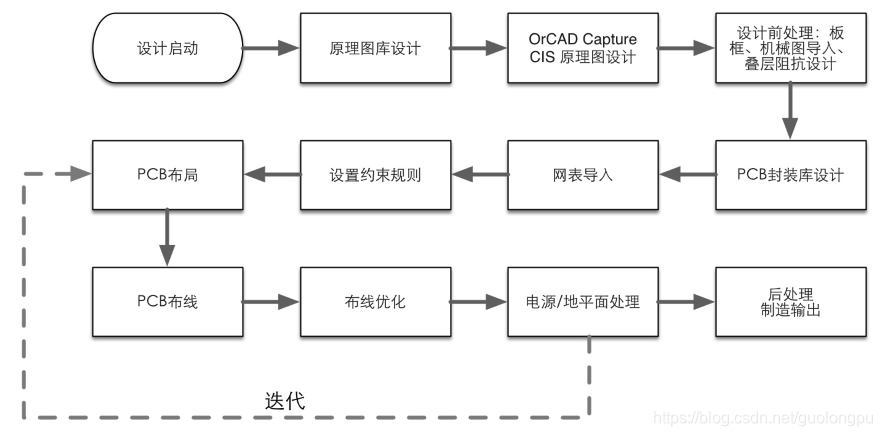

第四步:基于Cadence SPB的PCB设计流程

常规的基于Cadence SPB 的PCB设计流程如上图所述,其包括以下几个步骤:

设计启动

PCB设计项目的起点,在启动PCB项目设计之前应该完成产品的需求分析、特性评估、元器件选型、系统原理验证等工作。

原理图库设计

原理图库设计在 OrCAD软件里完成,OrCAD默认自带了许多常用的原理图库,我们可以利用系统自带的原理图库进行设计,以降低工作量,在大型一点的公司,会架设有原件信息系统(CIS),OrCAD Capture CIS 将CIS的功能特性与 Cadence 原理图绘制功能完美结合。通过对元件的有效管理,从而减少了搜索现有元件进行重用、手动输入元件信息内容和维护元件数据上的耗费的时间及精力。我们可以根据元件的电气属性搜索元件,而CIS会自动取回相关元件。CIS让工程师能够在设计流程的初期就可以调用正确的元件资料,并且可以将完整的规格传递到PCB工程师和其他相关设计人员手中,从而减少产生错误的可能性。CIS还能提供元件成本信息,能够让工程师直观的选用最优选的、低成本的元件。

对于个人学习环境,这里我们直接复用系统自带的原理图库,对于自带的原理图库没有的元器件,我们再参照相关的数据手册手动创建。

OrCAD Capture CIS 原理图设计

电路原理图,是电路结构的基本构造图,其详细的描绘了电路的大致原理,元件的互连网络关系及信号的走向。作为设计意图的体现,原理图的正确性非常重要。

绘制原理图除了需要保证原理图的电气原理正确性,原理图绘制还需要遵循一定的设计规范,需要具有良好的可阅读性,无歧义性。

我们在OrCAD Capture CIS 里完成原理图的设计工作。

PCB设计前处理

在进入PCB布局布线流程之前,我们得先确认一些PCB的物理结构约束条件,如:产品外形尺寸、接口孔位、PCB固定螺丝孔位,高度限制、是否有局部挖空区域等等。这些约束条件跟原理图的正确性一样重要,最终决定着PCB设计的成败。最终装配好的PCB必须与产品的结构尺寸相吻合,否则即使PCB画的再好,也是废品一件。

除此之外,我们还要根据关键信号的分布情况,确定好信号层及电源/地底层的分布,与PCB板厂沟通确认,明确PCB工艺及PCB的叠层结构。

PCB封装库设计

在绘制PCB之前,还必须确认好各个元器件的封装尺寸,对于系统没有的PCB封装库需要自行创建。

PCB封装库作为PCB设计的基本元素,其重要性是不言而喻的。我们很多新手犯得最多的错位就是封装尺寸弄错,或者管脚位弄反了。所以对于新手而言,创建封装库的时候,一定要仔细确认封装库的管脚顺序是否与数据手册的一致,然后在A4纸上打印出来,确认一下封装的尺寸是否合理。

网表导入

网表,即描述原理图中包含的各个元器件信息及其电气连接关系。Cadence SPB 中 原理图设计及PCB设计是分开的,OrCAD绘制的原理图可以输出网表信息给第三方的PCB设计软件。同理,Allegro也可以导入第三方的原理图设计软件输出的网表。

所以在PCB布局布线之前,需要导入网表信息,以明确元器件信息及其电气连接关系。

设计约束规则

又是体现出Allegro强大的地方,Allegro是规则驱动设计的,其提供了强大而完善的设计规范设定,用户设定好了整块板子规则后,在布局布线时只要把DRC都打开,确认好所有的DRC错误警告,整块板子就可以达到设计规范的所需要求。

正因为Allegro强大的规则约束设计,所以也略显复杂,后续章节会针对这部分做着重的详解。

PCB布局

PCB布局的合理性直接影响到了下一步的PCB布线的过程,PCB布局是否合理,直接关系到PCB 的EMC性能,可靠性、可装配性、可维护性、散热性等等。关于PCB的布局,需要遵循一定的设计规范标准,同时也是一个经验积累的工程。

好在我们准备练手的开发板布局相对简单,在后边的PCB设计环节我会列举一些典型的PCB布局注意事项。对于新手来说,可以多多借鉴高手们的作品。我们也可以上一些拆解评测网站,看一下实际产品的PCB布局情况,拆解网站给出的PCB清晰度不错,还给出了评测意见,比如按键布局是否合理,散热是否合理等等的建议,可以借鉴。

PCB布线

PCB布线是一门艺术,也是PCB设计过程中非常重要的一环,可以说无论是原理图的绘制,还是网表的导入和PCB布局,都是为了实现布线工作做准备的。Allegro为我们提供了非常强大而便利的PCB布线功能。

布线优化

就像写文章一样,需要重复的审阅,对个别句子及段落进行重新修饰及调整。还是那句话,PCB布线是一门艺术。

电源/地平面处理

电源/地是PCB的基石,为整个系统的稳定运作提供强有力的支撑。

后期处理及制造输出

PCB设计结束之后,在进行PCB打样之前,我们需要对着check list做最后的仔细检查、调整丝印、工程标准等等。确认无误后,输出Gerber光绘文件及钻孔文件给PCB厂家进行打样生产。