1 module SampleLogicRealTime(

module SampleLogicRealTime(

2 input rst_n,

input rst_n,

3 input iclk,

input iclk,

4 input trig,

input trig,

5 output oclk

output oclk

6 );

);

7

8 parameter IDLE = 2'b01,

parameter IDLE = 2'b01,

9 SAMPLE = 2'b10;

SAMPLE = 2'b10;

10

11 parameter LENGTH = 9'd300;

parameter LENGTH = 9'd300;

12

13 reg [1:0] current_state, //state

reg [1:0] current_state, //state

14 next_state;

next_state;

15

16 reg r_data_in0, //detect the risingedge reg

reg r_data_in0, //detect the risingedge reg

17 r_data_in1,

r_data_in1,

18 o_rising_edge;

o_rising_edge;

19

20 reg [8:0] count; //count for delay

reg [8:0] count; //count for delay

21 reg count_rst_n;

reg count_rst_n;

22

23 // sequential circuit

// sequential circuit

24 always@(posedge iclk, negedge rst_n) begin

always@(posedge iclk, negedge rst_n) begin

25 if (!rst_n) begin

if (!rst_n) begin

26 current_state <= IDLE;

current_state <= IDLE;

27 end

end

28 else begin

else begin

29 current_state <= next_state;

current_state <= next_state;

30 end

end

31 end

end

32 // combinational circuit for state logic

// combinational circuit for state logic

33 always@(current_state,count,o_rising_edge) begin

always@(current_state,count,o_rising_edge) begin

34 next_state = IDLE;

next_state = IDLE;

35

36 case (current_state)

case (current_state)

37 IDLE : next_state = o_rising_edge ? SAMPLE : IDLE;

IDLE : next_state = o_rising_edge ? SAMPLE : IDLE;

38 SAMPLE : next_state = (count >= LENGTH) ? IDLE : SAMPLE;

SAMPLE : next_state = (count >= LENGTH) ? IDLE : SAMPLE;

39 endcase

endcase

40 end

end

41

42 assign oclk = (count_rst_n ==1'b0)? 1'b0 : iclk;

assign oclk = (count_rst_n ==1'b0)? 1'b0 : iclk;

43 // combinational circuit for output logic

// combinational circuit for output logic

44 always@(current_state,iclk) begin

always@(current_state,iclk) begin

45

46 case (current_state)

case (current_state)

47 IDLE : begin

IDLE : begin

48 count_rst_n <= 1'b0;

count_rst_n <= 1'b0;

49 end

end

50 SAMPLE : begin

SAMPLE : begin

51 count_rst_n <= 1'b1;

count_rst_n <= 1'b1;

52 end

end

53 endcase

endcase

54 end

end

55

56 //detect the rising edge

//detect the rising edge

57 always@(posedge iclk) begin

always@(posedge iclk) begin

58 r_data_in0 <= r_data_in1;

r_data_in0 <= r_data_in1;

59 r_data_in1 <= trig;

r_data_in1 <= trig;

60 end

end

61 always@(r_data_in0,r_data_in1) begin

always@(r_data_in0,r_data_in1) begin

62 o_rising_edge = ~r_data_in0 & r_data_in1; //o_rising_edge output

o_rising_edge = ~r_data_in0 & r_data_in1; //o_rising_edge output

63 end

end

64

65 //counter

//counter

66 always@(posedge iclk) begin

always@(posedge iclk) begin

67 if(~count_rst_n)

if(~count_rst_n)

68 count <= 9'b0_0000_0000;

count <= 9'b0_0000_0000;

69 else

else

70 count <= count + 1'b1;

count <= count + 1'b1;

71 end

end

72

73 endmodule

endmodule

74

module SampleLogicRealTime(

module SampleLogicRealTime(2

input rst_n,

input rst_n,3

input iclk,

input iclk,4

input trig,

input trig,5

output oclk

output oclk6

);

);7

8

parameter IDLE = 2'b01,

parameter IDLE = 2'b01,9

SAMPLE = 2'b10;

SAMPLE = 2'b10;10

11

parameter LENGTH = 9'd300;

parameter LENGTH = 9'd300;12

13

reg [1:0] current_state, //state

reg [1:0] current_state, //state14

next_state;

next_state;15

16

reg r_data_in0, //detect the risingedge reg

reg r_data_in0, //detect the risingedge reg17

r_data_in1,

r_data_in1,18

o_rising_edge;

o_rising_edge;19

20

reg [8:0] count; //count for delay

reg [8:0] count; //count for delay 21

reg count_rst_n;

reg count_rst_n;22

23

// sequential circuit

// sequential circuit24

always@(posedge iclk, negedge rst_n) begin

always@(posedge iclk, negedge rst_n) begin25

if (!rst_n) begin

if (!rst_n) begin26

current_state <= IDLE;

current_state <= IDLE;27

end

end28

else begin

else begin29

current_state <= next_state;

current_state <= next_state;30

end

end31

end

end32

// combinational circuit for state logic

// combinational circuit for state logic33

always@(current_state,count,o_rising_edge) begin

always@(current_state,count,o_rising_edge) begin34

next_state = IDLE;

next_state = IDLE;35

36

case (current_state)

case (current_state)37

IDLE : next_state = o_rising_edge ? SAMPLE : IDLE;

IDLE : next_state = o_rising_edge ? SAMPLE : IDLE;38

SAMPLE : next_state = (count >= LENGTH) ? IDLE : SAMPLE;

SAMPLE : next_state = (count >= LENGTH) ? IDLE : SAMPLE;39

endcase

endcase40

end

end41

42

assign oclk = (count_rst_n ==1'b0)? 1'b0 : iclk;

assign oclk = (count_rst_n ==1'b0)? 1'b0 : iclk;43

// combinational circuit for output logic

// combinational circuit for output logic44

always@(current_state,iclk) begin

always@(current_state,iclk) begin45

46

case (current_state)

case (current_state)47

IDLE : begin

IDLE : begin 48

count_rst_n <= 1'b0;

count_rst_n <= 1'b0;49

end

end50

SAMPLE : begin

SAMPLE : begin51

count_rst_n <= 1'b1;

count_rst_n <= 1'b1;52

end

end53

endcase

endcase 54

end

end55

56

//detect the rising edge

//detect the rising edge57

always@(posedge iclk) begin

always@(posedge iclk) begin58

r_data_in0 <= r_data_in1;

r_data_in0 <= r_data_in1;59

r_data_in1 <= trig;

r_data_in1 <= trig;60

end

end61

always@(r_data_in0,r_data_in1) begin

always@(r_data_in0,r_data_in1) begin62

o_rising_edge = ~r_data_in0 & r_data_in1; //o_rising_edge output

o_rising_edge = ~r_data_in0 & r_data_in1; //o_rising_edge output63

end

end64

65

//counter

//counter66

always@(posedge iclk) begin

always@(posedge iclk) begin67

if(~count_rst_n)

if(~count_rst_n)68

count <= 9'b0_0000_0000;

count <= 9'b0_0000_0000;69

else

else70

count <= count + 1'b1;

count <= count + 1'b1;71

end

end72

73

endmodule

endmodule74

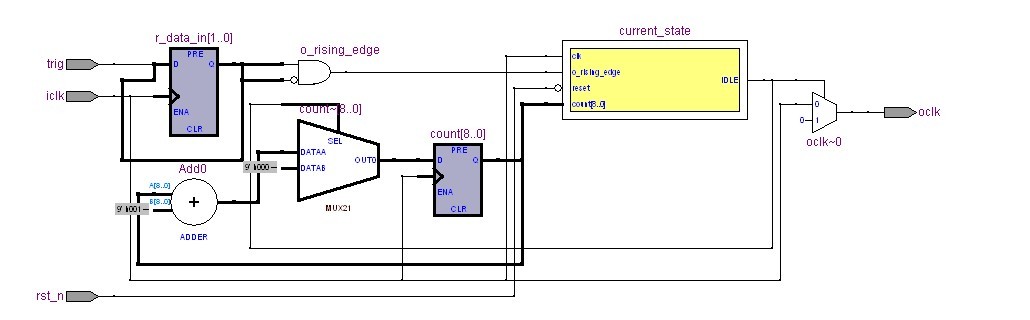

RTL图:

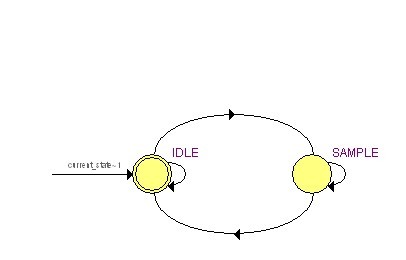

状态转换图: