今天想跟大家提一下IC 流程。因為我未來的分享也是和它有關。先溝通認知的部份,才能繼續下去。

我認為數位工程師的風格有很多,就像軟體工程師的風格也有很多種類。數位工程師的風格的分類,我是依據 IC流程來做分類的。每位數位工程師專精的地方有所不同,所以解決問題的思維也就不同。了解清楚 IC流程的權則劃分後,我會舉一些案例,讓大家去思考流程中的關鍵是什麼?初學者藉由這樣子的思索,探索想成為什麼樣子風格的數位工程師。

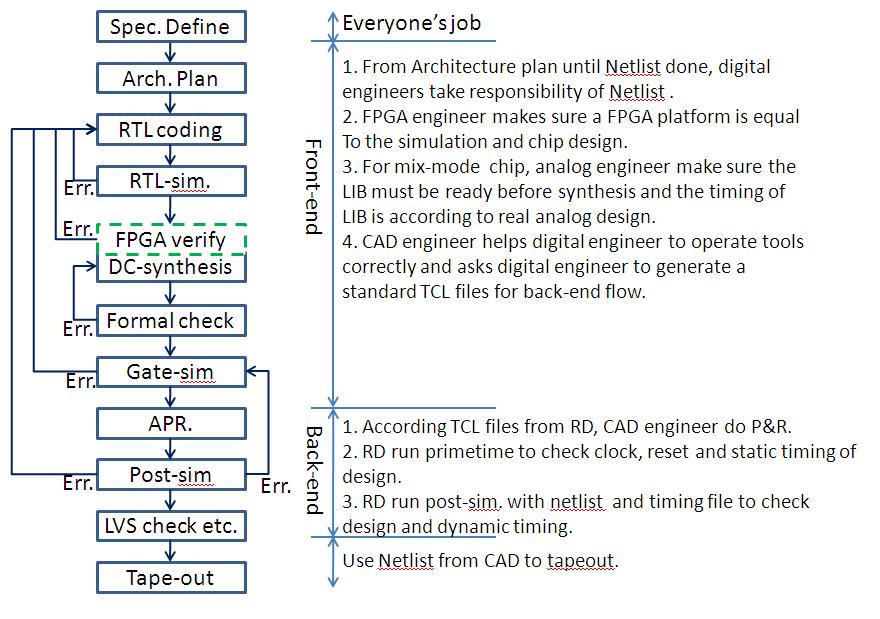

簡單說明一下流程。流程的開始是從規格的制定開始。確定規格後,開始規劃晶片的架構及功能。分配完工作後,就開始RTL coding。一邊coding一邊跑RT-level模擬。如果有錯誤,就回去修改RTL. 驗證所有的Design後,就去FPGA平台驗證,確認無誤後就可以合成netlist。Netlist和RTL做比對,確認兩者是相等的,就跑Gate-level 模擬。如果結果不是自己想要話,就是回到DC重新合成或是到修改RTL。都沒有錯,就給後段工程師APR. APR後,就跑Post-level 模擬。如果有錯,回到gate-level修正,或是RTL-level修正。如果都沒有錯,CAD工程師把後段的所有工作檢查完。然後就tape-out. 每個步驟都代表階段工作已驗證完畢後,才可以往下一個階段進行。

從Fig圖,我們看到,IC流程被分為front-end和back-end兩個階段。

先說Front-end:

我相信每位數位工程師都知道front-end的工作內容,在此就不贅述。數位工程師是否知道front-end階段中,他應該注意哪些細節,才會產出高品質的netlist。我提出幾點來供大家參考,如果你還有更好的想法,歡迎你也提出來分享!

1.RTL code都要是synthesizable(可被合成的),而且知道自己每個constrain的條件以及interface的timing要符合60/40原則。(60/40原則: 留給別人60%的timing margin。自己只用40%, 也有人說是40-20-40比例,40%自己用,40%是別的工程師用, 最後20%是留給CAD工程師做APR使用。)

2. RTL-level simulation coverage 要到90%以上。

3. FPGA驗證到錯誤時,必須把這個錯誤的情況重新複製到RTL-level simulation,建立完整的驗證資料庫,下一位工程師在改程式時,就不用在FPGA驗證時,才發現舊問題。混淆FPGA工程師驗證的流程。

4.合成時,確認每個D-flip-flop都有timing report可讀;每個path都有timing constrain;interface的delay都很完整。Clock的宣告都是符合你的設計想法。

5.做好clock tree和reset tree的說明,讓CAD工程師了解你的設計想法。

6.確認給CAD工程師的tcl檔案是對的,而且和你的DC tcl檔案是相符合的。

7.確認合成出來的netlist是對的後,才交給CAD工程師。

以上七點,相信大家都是認同的,但是有嚴格要求做到嗎?

舉例來說。相信大家一定看過 Interrupt的機制。如果沒有看過也沒有關係,下面是常見的Interrupt的機制。

原始範例:

always@(posedge clki or negedge rstni)

begin

if(~rstni)

IRR00 <=0;

else if(B==1) //error happend

IRR00 <=1;

else

IRR00<=0;

end

assign IR_EN00 = IRR00 & (REG_IRR_EN[0]);

assign IR_RST00 = (clr_id==4'h0);

always @(posedge IR_EN00 or negedge IR_RST00)

if(~ IR_RST00)

IRR_00_Z1 <= 0;

else

IRR_00_Z1 <= 1'b1;

else

IRR_00_Z1 <= IRR_00_Z1;

就IRR_00_Z1這個D-flip-flop而言,合成時,你有特別宣告IR_EN00為clock嗎?IR_RST00位於reset tree上,在做ATPG時,DRC不會過,DC-compiler會幫你修正,但是你怎麼知道它會幫你做?它做的修正是你想要的嗎?是對的嗎?

或許你想反駁,這些的 timing不是很重要,所以不用管。ATPG會幫你修正reset或是clock時,tool不會錯。這樣子的想法和上述哪幾點相衝突?

第一點 timing constrain不曉得要怎麼寫?

第四點 沒有每個D-flip-flop都有timing report,因為 clock無法宣告。

第七點 無法確認合成出來的所有 timing是對的,因為timing report無法全部產生。

如果程式改成下面的情況時,是不是就做到我們的要求?

解決方式一:

always@(posedge clki or negedge rstni)

begin

if(~rstni)

IRR00 <=0;

else if(B==1 & REG_IRR_EN[0]) //error happend

IRR00 <=1;

else

IRR00<=0;

end

always@(posedge clki or negedge rstni)

begin

if(~rstni)

IRR00_sync <=0;

else if(IRR00==1) //error happend

IRR00_sync <=~IRR00_sync;

else

IRR00_sync<=IRR00_sync;

end

always@(posedge nosleep_clki or negedge rstni)

begin

if(~rstni)

begin

IRR_00_Z1_pre_sync1 <=0;

IRR_00_Z1_pre_sync2 <=0;

end

else

begin

IRR_00_Z1_pre_sync1 <=IRR00_sync;

IRR_00_Z1_pre_sync2 <=IRR_00_Z1_pre_sync1;

IRR_00_Z1_pre_sync3 <=IRR_00_Z1_pre_sync2;

end

end

assign IRR_00_Z1_pre_sync4 = IRR_00_Z1_pre_sync2 ^ IRR_00_Z1_pre_sync3;

always@(posedge nosleep_clki or negedge rstni)

begin

if(~rstni)

begin

IRR_00_Z1 <= 0;

end

else if(IRR_00_Z1_pre_sync4)

begin

IRR_00_Z1 <= 1;

end

else if(clr_id==4'h0)

IRR_00_Z1 <= 0;

else

IRR_00_Z1 <= IRR_00_Z1;

End

clki和 nosleep_clki是我們一定會宣告。跨clock domain設false-path。IRR_00_Z1的 timing是不是就可以報告出來。

那原來的那段程式,是不是就不要再用?當然不是,我們是要符合七點的要求,design沒有做錯,為什麼要放棄?只要做些修正,重新合成,還是可以用。

解決方式二:

module interrupt_machine (

input clki

,input rstni

,input B

,input [3:0] clr_id

,input scan_mode

,output IRR_00_Z1

)

reg IRR00;

wire IR_EN00;

wire IR_RST00;

reg IRR_00_Z1;

always@(posedge clki or negedge rstni)

begin

if(~rstni)

IRR00 <=0;

else if(B==1) //error happend

IRR00 <=1;

else

IRR00<=0;

end

assign IR_EN00 = IRR00 & (REG_IRR_EN[0]);

assign IR_RST00 =scan_mode?rstni : (clr_id==4'h0);

always @(posedge IR_EN00 or negedge IR_RST00)

if(~ IR_RST00)

IRR_00_Z1 <= 0;

else

IRR_00_Z1 <= 1'b1;

else

IRR_00_Z1 <= IRR_00_Z1;

endmodule

將 Interrupt_machine單獨合成,請CAD工程師幫忙做成 Macro,確保 timing都是你想要的,以call macro方式來合成全部的電路;而 IR_RST00部份,你也修正到適合ATPG情況。當你在跑模擬或是 formal check時,都可以確保你的 reset沒有做錯。

這兩種做法都可以達到你的要求,但是它的差別是什麼你知道嗎?

第一種解決的情況是工程師自己可以解決,可以在RD團隊中解決問題。

第二種是需要CAD工程師幫忙保證你的 interrupt timing,這需要跨部門的合作。

這就是我所說的數位工程師的風格。你是要成為只相信tool的工程師;或是每個module都需要別人幫忙的工程師;亦或是自己可以處理每個bug,並想辦法驗證它的正確性以及 timing constrain的工程師。但是不管是哪一種,都希望你都能符合上述的七個要求。