Xilinx Vivado 提供了上板后的FPGA逻辑分析,信号视图显示等功能。

需要注意,上板后查看信号需要重新综合,并且需要耗费一定的片上布局布线资源。

1. 添加debug信号

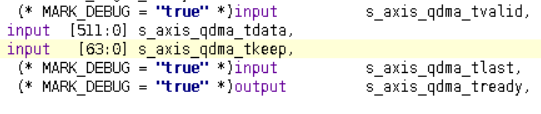

可以对模块端口或者wire 变量进行debug信号提取,只要在verilog代码前面添加:(* MARK_DEBUG = "true" *) 即可:例如,

此时需要跑综合,检查错误并分析语义。并且通过vivado综合,进行下一步。

2. 配置debug信号

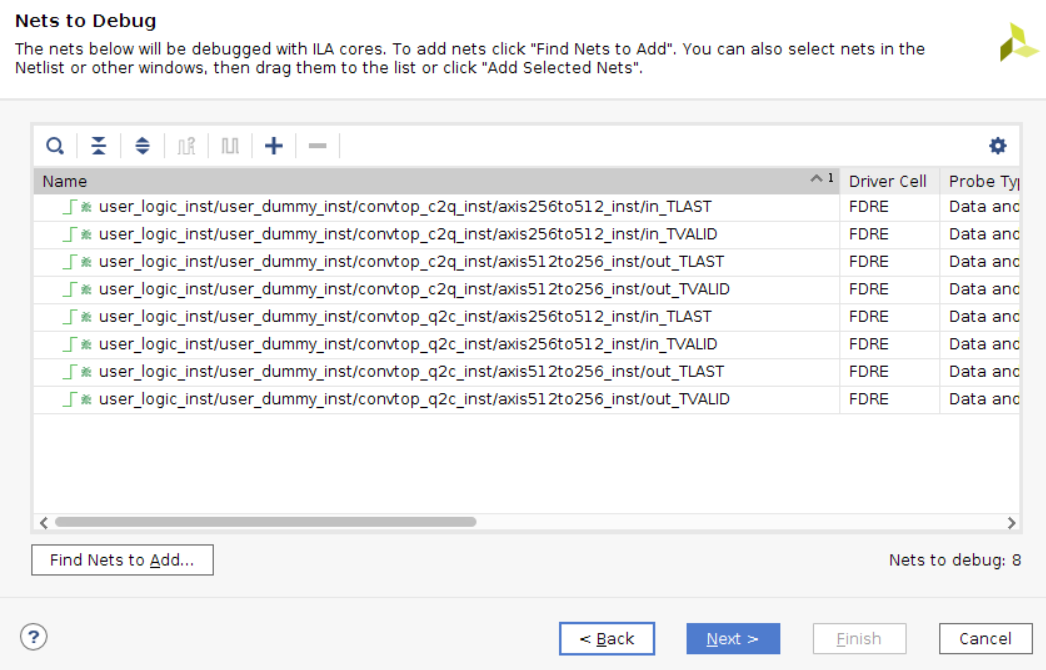

配置debug信号,用于挑选需要进行真正查看的信号名称。在写代码时可以添加很多debug标签,但是debug耗费片上资源,看哪一部分,实现哪一部分。

点击SYNTHESIS -> Set Up Debug。

选好需要debug的信号后:

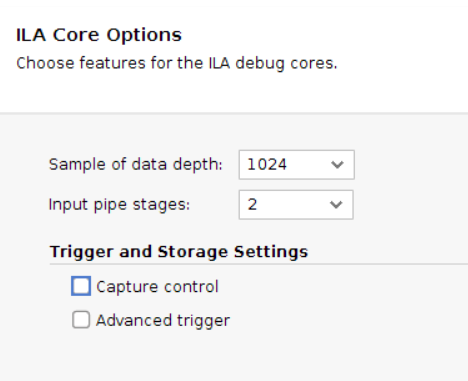

选择信号的缓存深度。由于片上信号速率大,我们不可能实时捕捉并上传,只能首先储存到片上逻辑分析core中,所以我们需要选择core的存储容量,一个深度对应为一个时钟周期,也就是我们存储多少时钟周期的debug信号值,之后会选择debug信号的记录触发条件,当满足何条件之后才开始缓存,帮助我们抓取特定时间窗口内的所有信号的波形图,一般我们先设定深度1024,输入节拍数为2:

完成:

之后vivado会修改工程的约束文件,进而我们需要重新再综合一次工程。之后再布局布线,timing保证没错误的前提下,即可生成bit文件并下载入FPGA,最后搭建测试场景并开始运行。

3. 使用JTAG仿真器在线仿真

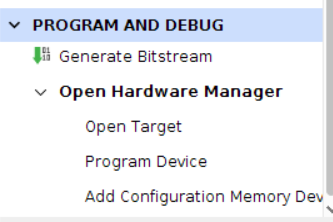

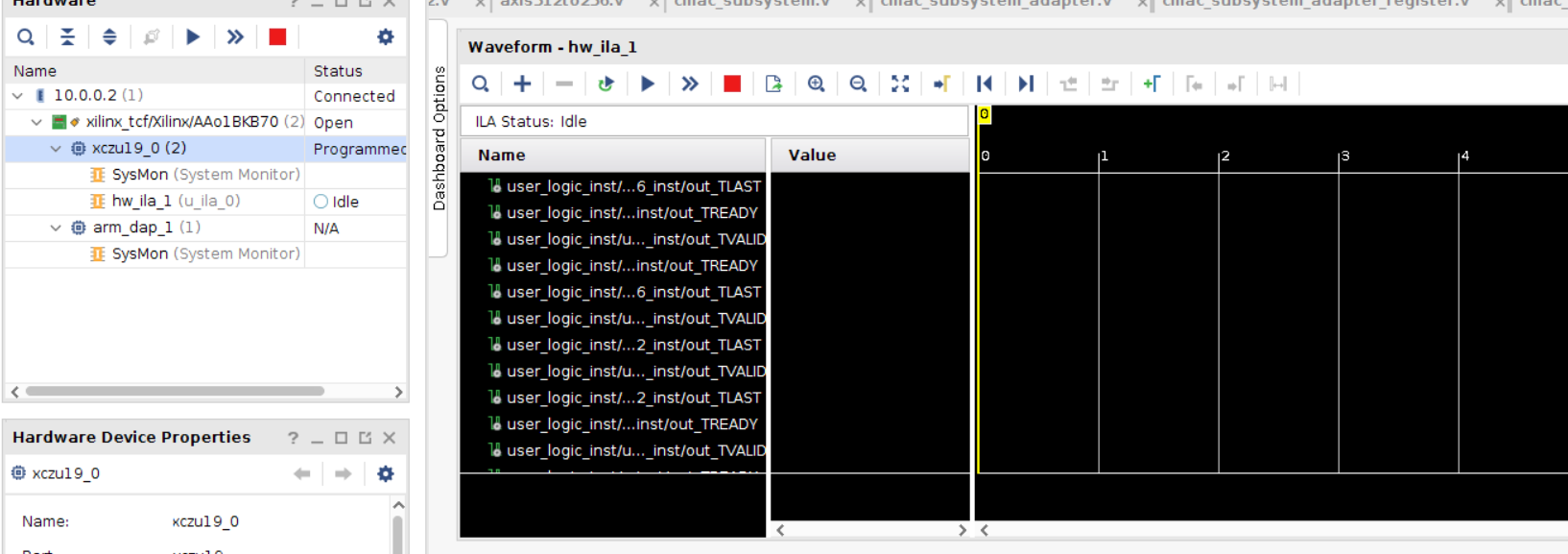

首先,打开硬件管理器中的目标器件

有仿真器的可以直接看到待观测信号:

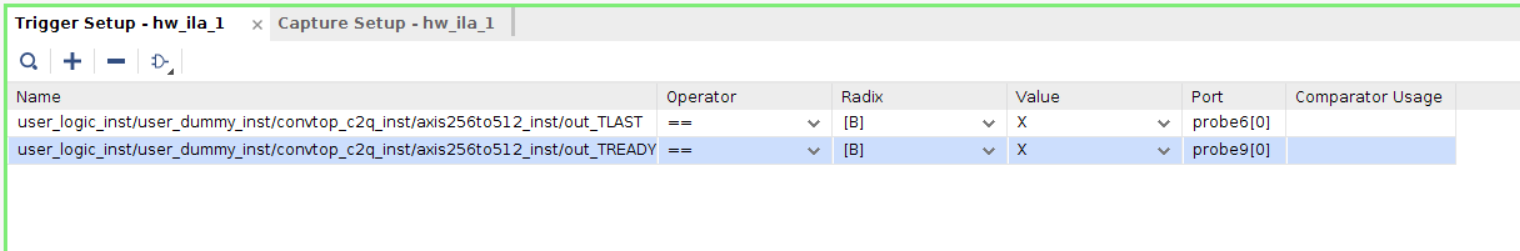

设置触发条件,在待测信号中设置一个触发条件,点击“+”添加触发条件信号到触发窗口中:

例如我们需要valid信号与ready信号同时为高时,开始捕捉信号波形,那么双击上面列表中的信号即可:

因为同时为高,所以设置value为1:

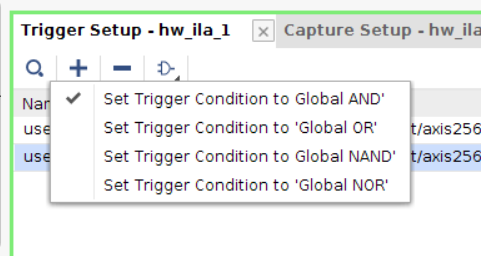

因为同时为高,所以用逻辑与,点击“三角”图标选择与逻辑:

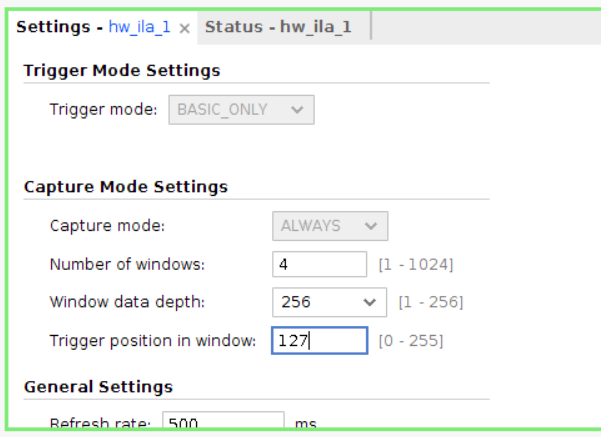

至此设置完成触发条件。接着设置触发次数,我们可以抓取多次满足触发条件前后的波形,在左边setting窗口中选择window数是4次,也就是4次触发,触发点选择在每个窗口的中间,那么触发点设为127即可:

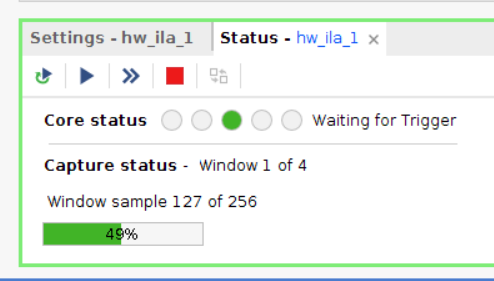

接下来,在status窗口点击运行按钮,即可开始捕捉波形:

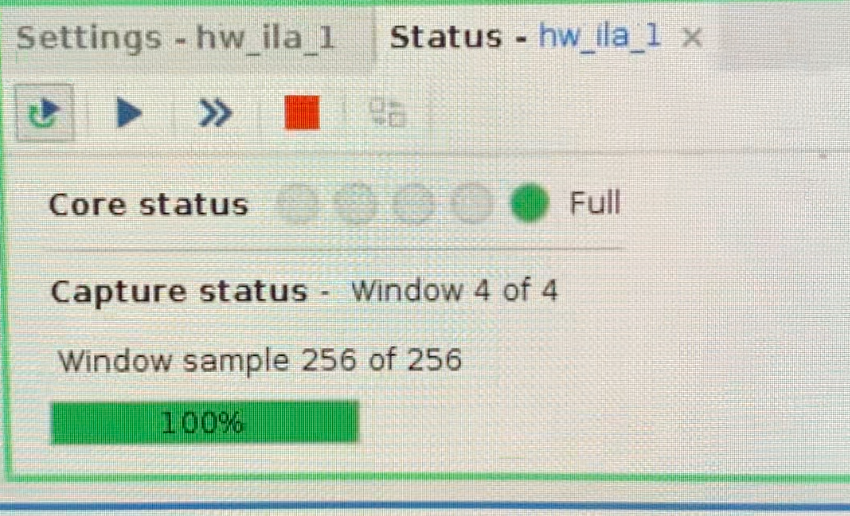

开始测试真实数据,或者实验,捕捉完成后,捕捉状态会变为100%:

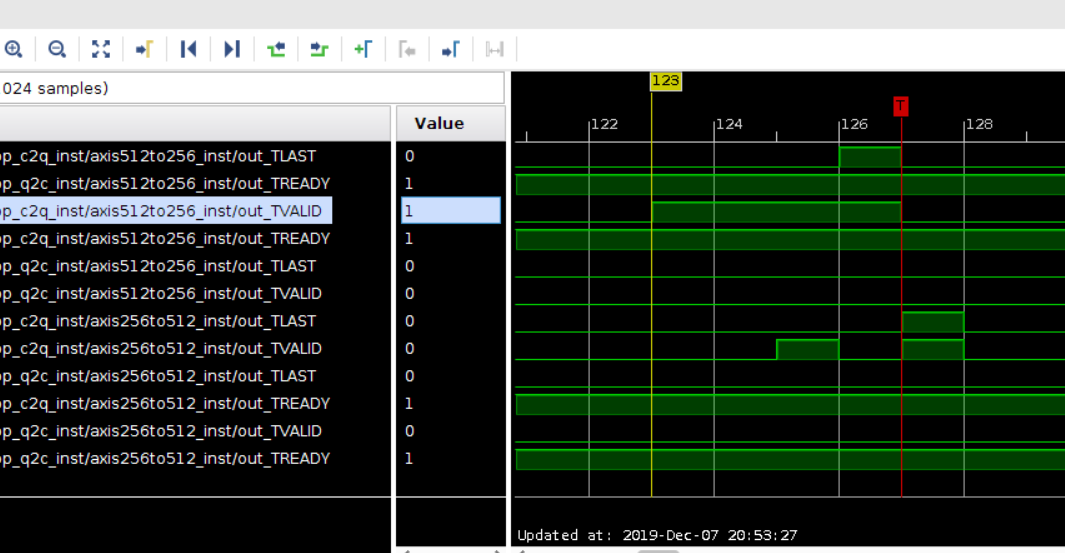

此时我们在波形窗口里即收到了四次,满足条件的捕捉,并注意他们不一定是时间连续的波形的捕捉,中间超过128时钟周期之外的数据也许会丢掉,但是不影响已经捕获的波形是满足捕获触发条件的。

完。