RTL:寄存器传输级别

LRM:语言参考手册

FSM:有限状态机

EDIF:电子数据交换格式

LSO:库搜索目录

XCF:XST 约束条件

1. par -ol. high 命令总是 '-'开头,参数紧跟其后

2.如果 一个命令被使用两次,请出现两次

3.参数顺序严格按照说明,不能乱序出现

4. 命令认大小写

4.常见命令

-f :执行命令文件

-h help

-intstyle : 集成风格 ? 只输出警告和错误

-intstyle ise|xflow|silent --三个必备条件 ise指明环境 xflow 指明作为部分数据流执行 silent 静默执行 只输出警告和错误

该程式在工程中默认运行

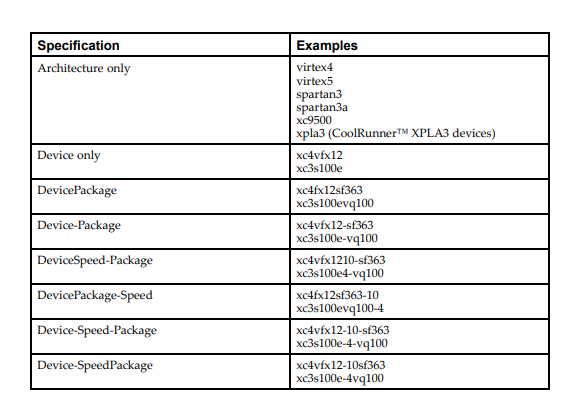

-p part number 设备编号

平台+型号+封装+速度

你可以在平台设计各个地方指定这个参数,但是网表不需要,网表约束条件NCF(Netlist Constraints File )不需要,网表阅读器需要(EDIF2NGD),用户约束文件不需要(UCF),运行NGDBuild需要必须提前指定一个架构。map也需要架构,封装,设备型号(可以出现在map命令行或者设计流之前)如果没有速度,默认一个速度 part number要和ngcbuild一致。SmartXplorer需要(FPGA only)。注意map指定的部件将会覆盖网表。

MAP:输入NGD文件,输出NCD文件。作用是将逻辑映射到物理逻辑单元。map可以包含高级优化选项(影响时间优化),这些选项可以放在初级映射.

的时候,也可以放在放置后。--- -global_opt 放置之前进行全局化优化。放置之后,进行时序检查,如果不符合将进行重新读取网表,放置优化操作。map会首先进行DRC检查。输出一个ncd文件(本地电路描述文件),可以由PAR进行路由和放置导线。

进行时序优化,timing-driven and rounting(-timing) must be enabled,开启物理综合优化 通过 -logic_opt(logic Optimization) -register_duplication(duplication Registers)

Placing and Routing

PAR 执行一个NCD(map)文件,输出一个本机电路描述NCD文件。据说可以手动和自动路由(EDitor)

map

input :需要一个ngd文件,ngd由ngdbuild生成。 NMC file,guide ncd file guide ngm file activity files

output: NCD PCF(约束文件,规则检查) NGM,MRP(报告文件),map(log),PSR(物理合成报告,只有某些优化开启才会生成)

工作流程:

1.选择器件 -- 使用命令 如果没有指定,会搜索ngd文件,如果也没有将报错

2.读取输入文件信息

3.DRC

4.删除多余的网络(S约束出现过网络将被保留,-u 所有网络将被保留)

5.将pads和它的逻辑连接到IOBS上

6.将逻辑映射到物理单元(按照约束)

7.更新从输入NGD文件接收到的信息,并将更新后的信息写入NGM文件。这个NGM文件包含关于设计的逻辑信息和关于如何映射设计的物理信息。NGM文件只用于反向注释

8.创建物理约束(PCF)文件。这是一个文本文件,包含在设计条目期间指定的任何约束。如果在设计条目期间没有指定约束,那么将创建一个空文件,以便您可以使用文本编辑器直接或间接地通过FPGA编辑器将约束输入到文件中MAP要么创建一个PCF文件(如果不存在),要么通过覆盖文件的SCHEMATIC生成部分(在SCHEMATIC语句之间)来重写现有文件开始和示意结束)。对于现有的约束文件,MAP还检查用户生成的部分,并可能注释掉带有错误的约束或停止程序。如果在用户生成的部分中没有发现错误,则该部分保持不变。

9.spartan3 -timing 必须

10.DRC

11.创建NCD文件

12.map report

语法:

map [options] infile[.ngd] [pcf_file.pcf]

-activityfile (Activity File):电源优化 模拟一个输入输出

-activityfile activityfile .vcd|.saif

-bp (Map Slice Logic)

这个选项启用块RAM映射。当块RAM映射被启用时,MAP尝试将lut和FFs放置到单输出、单端口块RAM中。

一个 hdl工程应该包含的文件

-c (Pack Slices) 如果使用 -timing 该功能不可用

对于不指定-timing的Spartan®-3,Spartan- 3a, Spartan- 3e和Virtex®-4设备,packfactor可以是0到100(包括)之 间的任意整数。

•对于Spartan-3, Spartan-3A, Spartan-3E和Virtex-4设备,当-timing被指定时,packfactor只能是0,1或100。

•对于Virtex-5、Spartan-6、Virtex-6、7系列和Zynq设备,时间驱动包装和放置始终开启,包装系数只能为1或100。

填充因子(对于非零值)是目标层密度百分比。

•封装因子值为0表示只有相关的逻辑(具有公共信号的逻辑)应该被封装到单个Slice中,并产生最不密集的封装设计。

•当封隔器试图达到最大的封隔密度时,封隔系数为1片利用率1%。

•封装系数为100意味着只有足够的不相关封装能够满足设备100%的利用率。这导致了最小的填充密度。

对于从1到100的填充系数值,MAP只有在设计要求更密集的填充以满足目标层利用率时,才会将不相关的逻辑合并到同一层中。如果不需要与设备匹配的无关包装,则指定-c 100时所使用的切片数将等于指定-c 0时所使用的切片数。

尽管指定较低的封隔系数会导致设计密度增大,但设计的位置和路线可能会更加困难。不相关的包可以创建具有冲突放置需求的切片,而密集的包可以创建局部路由拥塞。

-cm(cover mode)

-cm [area|speed|balanced]

此选项指定MAP覆盖阶段使用的标准。

注意:此选项不适用于Spartan-6、Virtex-6、7系列和Zynq设备。

area(默认值)使减少lut的数量(从而减少clb的数量)成为最高优先级。

速度的影响取决于是否有用户指定的时间限制。对于具有用户指定的时间限制的设计,速度模式将实现时间限制作为最高优先级,并将减少LUTS的级别(路径经过的LUTS的数量)作为下一个优先级。对于没有用户指定的时间限制的设计,速度模式使实现最大系统频率的最高优先级和减少lut的数量级别的下一个优先级。这个设置使得在放置和路由设计之后,很容易实现时间限制。对于大多数设计,lut的数量会有小幅增加(与面积设置相比),但在某些情况下,增幅可能会很大。

balanced试图平衡两个优先级——实现时间要求和减少lut的数量。它产生的结果与速度设置类似,但避免了lut数量大幅增加的可能性。对于具有用户指定的时间约束的设计,平衡模式使实现时间约束的优先级最高,减少LUTS的数量作为下一个优先级。对于没有用户指定时间约束的设计,平衡模式使实现最大系统频率的优先级最高,减少lut的数量下一个优先级。

-detail (Generate Detailed MAP Report)

此选项启用Map报告中的可选部分。

DCM和PLL配置数据(第12节)和控制集信息(第13节,仅Virtex®-5)包含在MAP报告中。

-equivalent_register_removal (Remove Redundant Registers)

-equivalent_register_removal {on|off}

启用此选项后,将检查任何具有冗余功能的寄存器,以确定删除它们是否会增加时钟频率。默认情况下,该选项是开启的。

此选项将删除冗余寄存器。

此选项仅适用于Spartan®-6、Virtex®-6、Virtex-5和Virtex-4设备。

此选项仅在使用-global_opt(全局优化)时可用

-f (Execute Commands File)

-f command_file

这个选项执行指定的command_file中的命令行参数

-global_opt (Global Optimization)

-global_opt off|speed|area|power

这个选项指示MAP在映射设计之前对完全组装的网表执行全局优化例程。

注意此选项仅适用于Spartan®-6、Virtex®-6、Virtex-5和Virtex-4设备。如果使用此选项,则禁用-register_duplication(重复寄存器)。

off(默认值)告诉MAP不要运行全局优化。

速度优化速度。

区域优化为最小的区域(不适用于Virtex-4设备)。

全局优化包括逻辑重新映射和调整、逻辑和寄存器复制和优化,以及3个状态缓冲区的逻辑替换。

这些例程将扩展MAP的运行时,因为会发生额外的处理。默认情况下,该选项是关闭的。注意-global_opt电源选项可以使用-activityfile选项提供的活动数据。当SmartGuide被启用时(-smartguide), guide的百分比会减少。请参阅-global_opt中的-equivalent_register_removal(删除冗余寄存器)选项。请参阅本章的再合成和物理合成优化部分。

-ignore_keep_hierarchy (Ignore KEEP_HIERARCHY Properties)

-ignore_keep_hierarchy(层级)

这个选项会导致MAP忽略块上的所有“KEEP_HIERARCHY”属性

-intstyle (Integration Style)

这个选项根据您正在运行的集成样式将屏幕输出限制为只输出警告和错误消息。

-intstyle ise|xflow|silent

当使用-intstyle时,必须指定以下三种模式之一:

•-intstyle ise表示该程序正在作为集成设计环境的一部分运行。

•-intstyle xflow表示程序正在作为集成批处理流程的一部分运行。

•-intstyle silent限制屏幕输出仅为警告和错误消息。

注意-intstyle在集成环境(如Project Navigator或XFLOW)中运行时会自动调用。

-ir all|off|place

all禁用所有RLOC处理。

off允许所有RLOC处理。

place告诉MAP使用RLOC约束对Slices中的逻辑进行分组,而不是生成

控制片的相对位置的rpm (Relationally Placed宏)。

-filter (Filter File)

此选项指定一个过滤器文件,其中包含用于捕获和过滤程序在执行期间产生的消息的设置。

-filter [filter_file ]

By default, the filter file name is filter.filter.

-lc (Lut Combining)

该选项指示Map将两个LUT组件组合成一个LUT6站点,利用该站点的双输出引脚。

注意此选项仅适用于Virtex-5、Spartan-6、Virtex-6、7系列和Zynq设备。

-lc [off|auto|area]

off(默认值)将禁用LUT组合特性。

area是更激进的选择,只要有可能就合并lut。

Auto将尝试在压缩和性能之间取得平衡。

-logic_opt (Logic Optimization)

此选项调用放置后逻辑重组,以改进时间和设计性能。

-logic_opt on|off

logic_opt选项在放置的网络列表上工作,通过重组和重新合成,然后是增量放置和增量计时分析,尝试和优化时间关键的连接。一个完全放置,时间优化的NCD设计文件产生。注意,此选项需要时间驱动的映射,这是通过MAP -timing选项启用的。当SmartGuide™被启用时(-smartguide), guide的百分比将会减少。

请参阅本章的“再合成”和“物理合成优化”章节。

-mt (Multi-Threading)

这个选项允许MAP使用多个处理器。它为Placer提供了多线程功能。

注意此选项仅适用于Virtex-5、Spartan-6、Virtex-6、7系列和Zynq设备。

-mt off|2

默认为关闭。当关闭时,软件只使用一个处理器。当值为

2、软件将使用2核,如果有的话。

-ntd (Non Timing Driven)

-ntd

该选项执行非定时驱动放置。

当启用-ntd开关时,将忽略所有时间限制,实现工具将不使用任何时间信息来放置和路由设计。

注意:要在没有时间限制的情况下运行整个流,需要为MAP和PAR指定-ntd开关。

-o (Output File Name)

此选项指定设计的输出NCD文件的名称

-o outfile[.ncd]

扩展名.ncd是可选的。输出文件名及其位置可通过以下方式确定:

•如果没有使用-o选项指定输出文件名,则输出文件将与输入文件同名,扩展名为。ncd。文件被放置在输入文件目录中

•如果你指定了一个没有路径说明符的输出文件名(例如cpu_dec. path)。ncd文件被放置在当前工作目录中,而不是/home/ design/ cpu_dec.ncd)。

•如果您使用完整的路径说明符指定输出文件名(例如,/home/designs/cpu_dec.ncd)

-ol (Overall Effort Level)

该选项设置总体MAP工作级别。努力水平通过选择一个或多或少的cpu密集型算法来控制用于包装和放置的时间量。

-ol std|high

使用std用于低工作水平(以QOR为代价的最快运行时间)

•使用高用于高工作水平(最佳QOR与增加的运行时)

所有架构的默认工作级别都很高。

当使用-timing选项运行时间驱动包装和放置时,-ol选项是可用的。

注意Xilinx®建议将MAP工作级别设置为等于或高于PAR effort level.

map -timing -ol std design.ncd output.ncd design.pcf

这个示例将总体MAP工作级别设置为std(以…为代价的最快运行时)

-p (Part Number)

此选项指定实现设计的部件

-p part_number

如果没有指定零件号,MAP将选择输入的NGD文件中指定的零件。如果输入的NGD文件中的信息没有指定完整的设备和包,则必须使用此选项输入设备和包的规格。如果有必要,MAP提供一个默认的速度值

您指定的体系结构必须与输入NGD文件中指定的体系结构相匹配。

您可能在运行NGDBuild时或在设计入口过程的早期步骤中选择了该架构(例如,您可能在ISE®design Suite或您的合成工具中指定了该架构)。如果架构不匹配,则必须再次运行NGDBuild并指定架构。

-power (Power Optimization)

此选项指定优化布局以降低功耗。Spartan-6,Virtex-6、7系列和Zynq设备,您可以使用high和xe选项指定使用智能时钟门控算法,以进一步降低功耗。

-power on|off|high|xe

Off指定不进行对运行时、内存或性能有负面影响的电源优化。这是默认选项。On (standard)规定在放置期间使用功率优化算法,以减少数据和时钟网上的电容负载,以减少整体动态功率。此选项的主要权衡是额外的运行时和修改位置,这可能导致性能略有下降。此选项可用于所有架构。High指定在设计中使用智能时钟门控算法,减少整体开关以降低动态功率。此选项的主要代价是额外的运行时间、较小的区域增加、增加的系统内存需求和数据或控制路径中的额外逻辑,这些都会导致性能下降。然而,与在(标准)上使用时相比,节省的电量通常更大。此选项仅适用于Spartan-6、Virtex-6、7系列和Zynq设备。Xe(额外的工作)指定使用标准和高级算法来最大限度地减少动态功率优化。然而,这种选择通常对运行时、区域、内存和性能有最大的影响。只有当设计中有足够的时间松弛,并且可以容忍额外的运行时和内存时,才建议使用此选项。此选项仅适用于Spartan-6、Virtex-6、7系列和Zynq设备。当您使用-power on时,您还可以指定一个切换活动文件,以进一步改进电源优化。有关更多信息,请参见-activityfile。你可以在-global_opt电源开关中使用-power选项来进行额外的电源优化和改进。有关更多信息,请参见-global_opt。

-pr (Pack Registers in I/O)

This option places registers in I/O

-pr off|i|o|b

默认情况下(没有-pr选项),MAP只在

如果一个IOB = TRUE属性已经被合成工具或用户约束文件(.ucf)应用到寄存器中,则I/O组件。pr选项指定可以将触发器或锁存器打包到输入寄存器(i选择)、输出寄存器中

(o选择),或两者(b选择),即使组件没有以这种方式指定。如果未指定此选项,则默认为off。对于寄存器上的IOB属性,无论设置为TRUE还是FALSE,都会覆盖-pr选项

-register_duplication (Duplicate Registers)

这个选项复制寄存器。

注意如果使用-global_opt, -register_duplication将被禁用。

-register_duplication on|off

register_duplication选项仅在使用-timing选项运行时间驱动的打包和放置时可用。register_duplication选项复制寄存器,以在运行时间驱动的打包时提高时间。

-r (Register Ordering)

这个选项将组成总线的寄存器分组到一个片中的有序序列中。寄存器根据它们的名称决定形成总线。

-r [4|off|8]

关闭禁用注册顺序。

4(默认)如果不是由LUT提供的,则每个片使用4个寄存器(否则使用8个寄存器)。

8使用切片中的所有8个寄存器。

-smartguide (SmartGuide)

该选项指示程序根据放置和路由的NCD文件,使用以前实现的结果来指导当前实现。SmartGuide技术自动实现MAP (MAP -timing)中的时间驱动包装和放置,提高了高利用率设计的设计性能和时间。如果在启用SmartGuide技术之前使用map -timing选项创建放置和路由NCD指南文件,可能会获得更好的结果。SmartGuide技术可以从命令行或从Project Navigator的Design面板的Hierarchy窗格中启用

-smartguide design_name .ncd

注意:如果有NGM文件可用,SmartGuide技术将提供更高的引导百分比。NGM文件包含MAP过程中完成的转换的信息。有关MAP如何检测NGM文件的信息,请参阅本章的MAP进程部分。使用SmartGuide技术,所有的引导都是在BEL级别的MAP中完成的。指导包括打包、放置和路线选择。SmartGuide技术可以优化设计的包装和布局,并在PAR期间路由新网。SmartGuide技术的第一个目标是在未改变的部分保持设计实施,并满足更改部分的时间要求;第二个目标是减少运行时。注意,实现中未更改的部分将不会被更改,因此将保持相同的计时分数。对于计时失败但没有更改的路径,应该100%进行指导。将重新实现计时失败和被更改的路径。

MAP运行的结果存储在输出MAP报告文件(.mrp)中。指南统计数据,包括指南网的数量和所有新的、指南和重新实施的组件都列在地图报告中,这是一份估计报告。最终的统计数据在PAR报告文件(. PAR)中列出。PAR会生成一个单独的指导报告文件(.grf),如果在PAR命令行中使用-smartguide,会生成一个详细的指导报告文件。如果不使用-smartguide,则会创建一个汇总指南报告文件。指南报告文件列出了重新实施或新建的组件和网。-timing选项可实现所有特定于时间驱动包装和放置的选项。这包括-ol选项,它设置用于包装和放置设计的总体工作级别。有关更多信息,请参见-ol(总体努力水平)。使用-timing命令时,会启用以下选项:-logic_opt、-ntd、-ol、-register_duplication、-x和-xe。有关详细信息,请参阅本节中各个选项的描述。有关更多信息,请参见-timing(时间驱动包装和放置)。

-t (Placer Cost Table)

此选项指定placer使用的成本表

-t [placer_cost_table ]

Placer_cost_table是placer使用的成本表(placer成本表在PAR章)。有效值为1 ~ 100,默认值为1。

要使用不同的成本表自动创建实现,请参考本指南中的SmartXplorer部分。

注意-t选项仅在使用-timing选项运行时间驱动的包装和放置时可用。

-timing (Timing-Driven Packing and Placement)

此选项用于提高设计性能。它指示MAP做包装和放置设计。在UCF/NCF文件中指定的用户生成的时间限制驱动这些包装和放置操作。

注-timing是可选的所有Spartan®-3系列和Virtex®-4设备(默认关闭)。Virtex-5、Spartan-6、Virtex-6、7系列和Zynq设备都是开启的。

-timing

当您指定-timing时,位置将在MAP中而不是PAR中进行。使用此选项可能会导致MAP的运行时间更长,尽管它会减少PAR的运行时间。建议采用时间驱动的包装和布局,以提高设计性能、时间和高度利用率的包装。如果不相关的逻辑编号(如MAP报告的Design Summary部分所示)是非零的,那么-timing选项对于在设备中封装更多的逻辑是有用的。当设计中有当地时钟时,也建议采用时间驱动的包装和放置。如果在没有用户时间约束的情况下选择了时间驱动的包装和放置,工具将自动生成并动态调整所有内部时钟的时间约束。该特性称为性能评估模式。更多信息请参见-x(性能评估模式)。这种模式允许一次性评估设计中所有时钟的时钟性能。通过这种模式实现的性能不一定是每个时钟可能达到的最佳性能,相反,它是设计中所有时钟之间的性能平衡。

-timing选项可实现所有特定于时间驱动包装和放置的选项。这包括-ol选项,它设置用于包装和放置设计的总体工作级别。有关更多信息,请参见-ol(总体努力水平)。使用-timing命令时,会启用以下选项:-logic_opt、-ntd、-ol、-register_duplication、-x和-xe。有关详细信息,请参阅本节中各个选项的描述。更多信息,请参见本章中的再合成和物理合成优化

-u (Do Not Remove Unused Logic)

这个选项告诉MAP不要从设计中删除未使用的组件和网

-u

默认情况下(没有u选项),MAP在映射之前从设计中消除了未使用的组件和网。未使用的逻辑是未驱动的逻辑,不驱动其他逻辑,或作为一个周期且不影响设备输出的逻辑。当指定u时,MAP对所有悬空信号应用一个S (NOCLIP)属性,以防止在该点开始修剪并通过设计级联。悬空组件仍然可以被修剪,除非出现接受NOCLIP属性的悬空信号

-w (Overwrite Existing Files)

此选项指示MAP覆盖现有的输出文件,包括现有的设计文件(NCD)。

-w

-x(Performance Evaluation Mode)

如果在用户约束文件中指定了计时约束,并且您希望使用工具生成的计时约束执行MAP和PAR运行,而不是评估设计中每个时钟的性能,则使用-x选项。

-x

该操作称为“性能评估”模式。此模式可以通过使用-x选项或在设计中没有使用时间限制时进入。这些工具分别为每个内部时钟创建时间约束,并将根据执行期间的反馈收紧/放松约束。MAP工作级别控制关注的是最快运行时(STD)还是最佳性能(HIGH)。注意虽然x忽略所有用户生成的时间约束,在UCF/NCF文件中指定,但所有物理约束,如LOC和AREA_GROUPS将被使用。注意-x和-ntd开关互斥。如果不使用用户定时约束,则只能选择一种自动定时方式。

-xe (Extra Effort Level)

当使用-timing选项运行由时间驱动的打包和放置时,可以使用-xe选项,并设置额外的工作级别。

-xe effort_level

可以将Effort_level设置为n(正常)或c(继续)。当-xe设置为c时,MAP继续尝试改进打包,直到很少或没有改进。

map -ol high -xe n design.ncd output.ncd design.pcf

-xt (Extra Placer Cost Table)

此选项指定适合高利用率设计的成本表。这些表可以与常规成本表一起使用(-t选项)。

此选项仅适用于Spartan-6、Virtex-6、7系列和Zynq设备

-xt cost_table

Cost_table是一个介于0和5(包括)之间的整数,它将选择算法的变体,让您更紧密地优化它们以适应您的设计。默认值是0。

Resynthesis and Physical Synthesis Optimizations

MAP提供了支持高级优化的选项,这些选项能够改进标准实现之外的计时结果。这些高级优化可以在放置之前或之后改变设计。优化可以应用于Xilinx设计流程中的两个不同阶段。第一个阶段发生在逻辑到体系结构片段的初始映射之后。MAP -global_opt选项指示MAP在完全映射的设计上执行全局优化例程,然后再进行布局。更多信息请参见-global_opt(全局优化)。可以应用优化的第二个阶段是在布局之后,当不满足时间要求的路径被评估和重新合成时。MAP获取初始网表,放置它,然后分析设计的时间。当不满足时序时,MAP执行物理合成优化,并将网表转换为满足时序。要启用物理合成优化,必须启用时间驱动的放置和路由(-timing)。物理合成优化是通过-logic_opt(逻辑优化)和register_duplication(重复寄存器)选项启用的。有关可用选项的更多信息,请参阅本章的MAP选项部分。

Guided Mapping

在引导映射中,使用现有的NCD来指导当前MAP运行。指南文件可以来自实施的任何阶段:未放置或已放置,未路由或已路由。

Xilinx®建议使用当前版本的软件生成NCD文件。

使用以前的软件版本生成的指南文件通常可以工作,但可能不支持。

注意当使用带有-timing选项的指导映射时,Xilinx建议使用放置的NCD作为指导文件。一个放置的NCD是通过运行MAP与-timing选项,或运行PAR。

SmartGuide™技术允许先前实现的结果指导下一个实现。当使用SmartGuide时,MAP和PAR进程使用带有-smartguide选项的NCD文件来指导新的和重新实现的组件和网络。SmartGuide技术可以移动导向组件和网来满足时间要求。SmartGuide技术的第一个目标是满足时间要求;第二个目标是减少运行时。]

SmartGuide技术在设计周期结束时效果最好,此时满足了时间要求,并进行了小的设计更改。如果设计变更的路径难以满足时间要求,则无需SmartGuide技术即可获得最佳性能。

其他适用于SmartGuide技术的设计改变的例子有:

•改变引脚位置

更改实例化组件的属性

•放松时间限制的变化

•添加ChipScope™核心的更改

在这个版本的Xilinx软件中,SmartGuide取代了-gm和-gf选项。

Simulating Map Results

当使用NGC文件进行模拟时,你并不是在模拟一个映射结果,而是在模拟逻辑电路描述。当使用NCD文件进行模拟时,您是在模拟物理电路描述。

MAP可能会生成一个在反注释模拟网络列表中未检测到的错误。

例如,在运行MAP后,可以执行如下命令生成回注的仿真netlist:

netgen mapped.ncd mapped.ngm -o mapped.nga

test

map -intstyle ise -p xc6vlx75t-ff484-1 -w -ol high -t 1 -xt 0 -register_duplication off -global_opt off -mt off -ir off -pr o -lc off -power off -o wave_gen_map.ncd wave_gen.ngd wave_gen.pcf

DRC Options

• -e (Error Report) • -o (Output file) • -s (Summary Report) • -v (Verbose Report) • -z (Report Incomplete Programming)

Place and Route (PAR)

map->ncd->PAR->(bitgen使用的ncd)

SmartGuide™ map par 后少量优化

Timing-driven Xilinx®时序分析软件使PAR能够基于时序限制进行设计。

Non Timing-driven (cost-based) 放置和路由是使用各种成本表来执行的,这些成本表将权重值分配给相关因素,如约束、连接长度和可用路由资源。如果没有时间限制,则使用非时间驱动的放置和路由。

input : ncd file pcf file guide ncd file

output: ncd file par file pad file csv file txt file xrpt file unroutes file

placing : 如果map 已经执行了 -timing 说明已经执行了放置,par只执行路由

Timing Driven PAR:是一个不依赖输入刺激的静态时序分析工具,

在原理图捕获或HDL设计输入程序中,将时间限制作为属性输入。在大多数情况下,NCF将由合成工具自动生成。

将您的时间限制写入用户约束文件(UCF)。当生成逻辑设计数据库时,这个文件由NGDBuild处理。为了避免在UCF中手动输入时间约束,可以使用constraints Editor,它极大地简化了约束的创建。有关如何使用约束编辑器的详细描述,请参阅软件附带的约束编辑器帮助。

在物理约束文件(PCF)中输入时间约束,该文件是由MAP生成的。PCF文件包含使用前面描述的两个方法指定的任何计时约束,以及您在文件中输入的任何附加约束。一般不建议修改PCF文件。

如果在设计中没有找到计时约束,或者选中了Project Navigator“忽略用户计时约束”选项,所有内部时钟都会自动生成计时约束。当PAR运行时,将调整这些约束以获得更好的性能。实现的性能级别与PAR工作级别的设置直接相关。努力级STD将有最快的运行时间和最低的性能,努力级HIGH将有最好的性能和最长的运行时间。如果PAR在物理约束文件中找到时间约束,则自动调用时间驱动的放置和时间驱动的路由。物理约束文件作为时序分析软件的输入。有关约束的更多信息,请参见约束指南(UG625)。

语法;

par [options] infile[.ncd] outfile [pcf_file[.pcf]]

选项可以是PAR options中列出的任意数量的PAR选项。按任意顺序输入选项,在选项前面加上破折号(键盘上的减号),并用空格隔开。

Infile是您希望放置和路由的设计文件。该文件必须包含.ncd扩展名,但您不必在命令行上指定.ncd扩展名。

outfile是PAR完成后写入的目标设计文件。如果指定的命令选项产生单个输出设计文件,则outfile的扩展名为.ncd。

NCD扩展名生成NCD格式的输出文件。如果指定的命令选项产生多个输出设计文件,则outfile必须具有扩展名。多个输出文件放置在具有默认扩展名.ncd的目录中。

注意:如果指定的文件或目录已经存在,则会出现错误消息,操作不会运行。您可以通过使用-w选项来覆盖这个保护并自动覆盖现有的文件。

pcf_file是一个物理约束文件(PCF)。该文件包含您在设计条目期间输入的约束、您使用用户约束文件(UCF)添加的约束以及您直接在PCF文件中添加的约束。如果您没有在命令行中输入PCF的名称,并且当前目录包含带有不完整名称和. PCF扩展名的现有PCF, PAR将使用现有的PCF。

par input.ncd output.ncd

这个示例在文件输入中放置和路由设计。并将放置的和路由的设计写入output.ncd。

注意,PAR将自动检测并包含与输入NCD文件具有相同根名称的PCF

par -k previous.ncd reentrant.ncd pref.pcf

此示例跳过放置阶段,并保留所有路由信息而不锁定它(重入路由)。然后它按照pref.pcf文件中找到的时间限制运行。如果设计是完全路由的,并且你的时间限制没有被满足,那么路由器尝试重新路由,直到时间目标被实现或直到它确定它不能实现。

-activityfile (Activity File)

此选项允许您指定一个切换活动数据文件来指导电源优化。

注意此选项需要使用-power选项,除Spartan-6、Virtex-6、7系列和Zynq外,该选项适用于所有架构。

-activityfile activityfile .{vcd|saif} PAR supports two activity file formats, .saif and .vcd.

-clock_regions (Generate Clock Region Report)

使用此选项指定是否生成时钟区域报告运行PAR进程。

-clock_regions generate_clock_region_report

该报告包含关于每个时钟区域的资源利用的信息,并列出了一个时钟区域内全局时钟缓冲区之间的时钟冲突。

-f (Execute Commands File)

这个选项执行指定的command_file中的命令行参数

-f command_file

有关-f选项的更多信息,请参见介绍章节。

-intstyle (Integration Style)

这个选项根据您正在运行的集成样式将屏幕输出限制为只输出警告和错误消息。

-intstyle ise|xflow|silent

当使用-intstyle时,必须指定以下三种模式之一:

•-intstyle ise表示该程序正在作为集成设计环境的一部分运行。

•-intstyle xflow表示程序正在作为集成批处理流程的一部分运行。

•-intstyle silent限制屏幕输出仅为警告和错误消息。

注意-intstyle在集成环境(如Project Navigator或XFLOW)中运行时会自动调用。

-filter (Filter File)

此选项指定一个过滤器文件,其中包含用于捕获和过滤程序在执行期间产生的消息的设置

-filter [filter_file ]

By default, the filter file name is filter.filter

(Re-Entrant Routing)

该选项从现有的位置和路由开始运行重入路由。默认情况下,该选项是关闭的。

previous_NCD.ncd reentrant.ncd

路由以现有的布局和路由为起点;但是,可能会发生路由更改,现有的路由资源不会被保留。

重入路由对于手动路由设计的部分,然后继续自动路由是有用的;例如,恢复过早停止的路由(Ctrl-C),或运行额外的路由传递。

-mt (Multi-Threading)

这个选项允许PAR使用多个处理器。它为Placer提供了多线程功能。

注:此选项适用于除Spartan®-3、Spartan- 3a、

Spartan-3E和Virtex®-4设备。当您使用时,多线程不可用

-smartguide、-power on、-x、partition或一个没有PCF文件的项目。

-mt off|2|3|4

默认为关闭。当关闭时,软件只使用一个处理器。当值为

2、3或4软件将使用到指定的核数。

-nopad (No Pad)

此选项关闭为PAD文件报告创建三种输出格式

-nopad

默认情况下,所有这三种PAD报表类型都是在运行PAR时创建的。

-ntd (Non Timing Driven)

这个选项告诉PAR执行非计时驱动放置

-ntd

当启用-ntd开关时,将忽略所有时间限制,实现工具将不使用任何时间信息来放置和路由设计。

注意这个选项对MAP和PAR都可用,要想在没有时间限制的情况下运行整个流,可以为MAP和PAR设置-ntd开关。

-ol (Overall Effort Level)

此选项设置整体PAR工作级别。

-ol high|std

使用高用于高工作级别(增加运行时的最佳QOR)

•使用std用于低工作水平(以QOR为代价的最快运行时间)

对于Spartan®-3、Spartan- 3a、Spartan- 3e和Virtex®-4设备,默认的工作级别是std,对于所有更新的架构来说都是高级别。

当使用-timing选项运行时间驱动包装和放置时,-ol选项是可用的。

注意Xilinx®建议将MAP工作级别设置为等于或高于

努力水平不相上下。

par -ol std design.ncd output.ncd design.pcf

此示例将整体PAR工作级别设置为std(以QOR为代价的最快运行时)。

-p (No Placement)

这个选项告诉PAR绕过placer并进入路由阶段。当使用此选项时,必须完全放置设计,否则PAR将发出错误消息并退出。

-p

当你使用这个选项时,现有的路由在路由开始之前被销毁。要保留现有路由,请使用-k(重入路由)选项而不是-p。

注意:使用这个选项可以保持之前的NCD位置,但要重新运行路由器

par -p design.ncd output.ncd design.pcf

这个示例告诉PAR跳过放置,直接进行路由。如果设计没有完全到位,您将得到一条错误消息,PAR将不做任何事情。

-pl (Placer Effort Level)

此选项为PAR设置Placer工作级别,覆盖总体工作级别设置。

注:此选项仅适用于Spartan®-3,Spartan- 3a, Spartan- 3e和

Virtex®4设备。对于其他设备,使用-ol (Overall Effort Level)。

-pl high|std

使用高为最好的放置结果,但较长的运行时间。这个设置适用于更复杂的设计。

•使用std快速运行时间与最低的放置努力。这个设置适用于不太复杂的设计。

当您使用-pl时,默认的工作级别是高的。

par -pl high design.ncd output.ncd design.pcf

此示例覆盖PAR的总体工作级别设置,并将Placer工作级别设置为较高。

-power (Power Aware PAR)

这个选项告诉PAR优化非时序关键设计信号的电容

-power [on|off]

这个选项的默认设置是关闭的。对于Spartan-6、Virtex-6、7系列和Zynq以外的设备,当您使用-power on时,您也可以指定一个切换活动文件来指导电源优化。参见-activityfile(活动文件)选项。

-r (No Routing)

这个选项告诉PAR在完成布局后跳过路由设计。

-r

注意:要跳过已经完全放置的设计,请使用-p(不放置)选项。

par -r design.ncd route.ncd design.pcf

此示例导致设计在路由阶段之前退出。

-rl (Router Effort Level)

此选项为PAR设置Router工作级别,覆盖总体工作级别设置。

注:此选项仅适用于Spartan®-3,Spartan- 3a, Spartan- 3e和

Virtex®4设备。对于其他设备,使用-ol (Overall Effort Level)。

-rl high|std

使用高值可获得最佳路由结果,但运行时间较长。这个设置适用于更复杂的设计。

•使用std快速运行时间和最低的路由努力。这个设置适用于不太复杂的设计

当您使用-rl时,默认的工作级别是高的

par -rl high design.ncd output.ncd design.pcf

此示例覆盖PAR的总体工作级别设置,并将Router工作级别设置为较高。

-smartguide (SmartGuide)

该选项指示程序根据放置和路由的NCD文件,使用以前实现的结果来指导当前实现。SmartGuide技术自动实现MAP (MAP -timing)中的时间驱动包装和放置,提高了高利用率设计的设计性能和时间。如果在启用SmartGuide技术之前使用map -timing选项创建放置和路由NCD指南文件,可能会获得更好的结果。SmartGuide技术可以从命令行或从Project Navigator的Design面板的Hierarchy窗格中启用。

-smartguide design_name .ncd

使用SmartGuide技术,所有的引导都是在BEL级别的MAP中完成的。指导包括打包、放置和路线选择。SmartGuide技术可以优化设计的包装和布局,并在PAR期间路由新网。SmartGuide技术的第一个目标是在未改变的部分保持设计实施,并满足更改部分的时间要求;第二个目标是减少运行时。注意,实现中未更改的部分将不会被更改,因此将保持相同的计时分数。对于计时失败但没有更改的路径,应该100%进行指导。将重新实现计时失败和被更改的路径。MAP运行的结果存储在输出MAP报告文件(.mrp)中。指南统计数据,包括指南网的数量和所有新的、指南和重新实施的组件都列在地图报告中,这是一份估计报告。最终的统计数据在PAR报告文件(. PAR)中列出。PAR会生成一个单独的指导报告文件(.grf),如果在PAR命令行中使用-smartguide,会生成一个详细的指导报告文件。如果不使用-smartguide,则会创建一个汇总指南报告文件。指南报告文件列出了重新实施或新建的组件和网。更多信息和示例,请参见本章的指南报告文件(GRF)

-t (Placer Cost Table)

此选项指定placer使用的成本表

-t [placer_cost_table ]

Placer_cost_table是placer使用的成本表。有效值为1 ~ 100,默认值为1。

要使用几个不同的成本表来创建实现,请参见本指南中的SmartXplorer章节。

注意此选项仅适用于Spartan®-3,Spartan- 3a, Spartan- 3e和Virtex®-4设备。对于其他设备,要查看成本表,使用MAP选项-t (Starting

砂矿成本表)代替。

par -t 10 -pl high -rl std design.ncd output_directory design.pcf

在本例中,PAR使用成本表10。placer的努力是最高的,路由器的努力在std。

-w (Overwrite Existing Files)

此选项指示PAR覆盖现有的NCD文件。

-w

默认情况下(没有此选项),PAR将不会覆盖现有的NCD文件。如果指定的NCD存在,PAR将给出一个错误并在运行位置和路由之前终止

-x (Performance Evaluation Mode)

该选项告诉PAR忽略提供的任何计时约束,并在所有内部时钟上生成新的计时约束。

-x

如果在物理约束文件中指定了计时约束,并且希望使用工具生成的计时约束执行PAR运行,而不是评估设计中每个时钟的性能,则使用此选项。该操作称为“性能评估模式”。此模式可以通过使用-x选项或在设计中没有使用时间限制时进入。工具生成的时间约束分别约束每个内部时钟,并根据执行期间的反馈收紧/放松约束。PAR工作级别控制关注的是最快运行时(STD)还是最佳性能(HIGH)。PAR忽略了设计中的所有时间限制。pcf,并使用所有物理约束,如LOC和AREA_RANGE。

-xe (Extra Effort Level)

使用这个选项来设置额外的努力水平。

-xe n|c

n (normal)告诉PAR使用额外的运行时密集方法,以尝试满足困难的时间限制。如果PAR确定不能满足时间限制,则会发出一条消息,说明不能满足时间限制,PAR退出。c (continue)告诉PAR继续路由,即使PAR确定不能满足时间限制。PAR继续尝试路由和改进计时,直到几乎或没有计时改进。注意使用额外的努力c会导致非常长的运行时间。要使用-xe选项,还必须将-ol (Overall Effort Level)选项设置为高,或者将-pl (Placer Effort Level)选项和-rl (Router Effort Level)选项设置为高。

par -ol high -xe n design.ncd output.ncd design.pcf

此示例指示PAR使用额外的工作,但如果确定不能满足时间限制则退出。

////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

设计信息-显示PAR命令行、已将设计放置和路由到的设备、输入设计文件(NCD和PCF)上的信息,以及执行放置和路由的时间。警告和信息消息也可能出现在PAR报告的第一部分中。设计摘要-提供设计中资源的细分,并包括设备利用率摘要。Placer结果-列出Placer的不同阶段,并确定哪个阶段正在执行。所示的校验和数仅用于Xilinx调试目的,并不能反映placer运行的质量。注意当运行map -timing和SmartGuide工具时,placer结果不会出现在PAR报告文件中。这些流的放置在MAP中完成。路由器结果-列出路由器的每个阶段,并报告未路由网的数量,以及括号中显示的大约时间分数。SmartGuide报告-描述路由器被调用后的guide结果。PAR报告的这一部分准确地反映了输入设计和指导设计之间的差异,包括指导的、重新实现的和新的或更改的组件的数量。分区实现状态-列出哪些分区被保留,哪些分区被重新实现,以及它们被重新实现的原因。如果在设计中没有找到分区,PAR报告将说明这一点。时钟报告——以表格的形式列出设计中的所有时钟,并提供有关路由资源、扇形输出数量、每个时钟的最大净倾斜和最大延迟的信息。时钟表中的锁定列指示时钟驱动程序(BUFGMUX)是分配给特定的站点还是左浮动。注意:在时钟表中列出的时钟偏差和延迟与TRACE和定时分析仪中报告的偏差和延迟不同。PAR考虑驱动时钟针的网络,而TRACE和Timing Analyzer包括整个时钟路径。计时得分——列出关于输入PCF中包含的计时约束的信息,包括满足了多少个计时约束。本节的第一行显示了时间评分。在不满足时间限制的情况下,时间评分将大于0。一般来说,计时分数越低,结果越好。注意,当输入PCF中没有给出约束或使用-x选项时,PAR报告的这一部分中的约束表不会生成。摘要-列出PAR是否能够成功地放置和路由设计。本节还列出了在REAL time和CPU时间中完成PAR运行所用的总时间。PAR报告的最后一节列出了在PAR调用期间发现的错误、警告和信息性消息数量的摘要。

//////////////////////////////////////////////////////////////////////////////////////////////////////////

smartxplorer -p xc6slx16-2-csg324 -uc stopwatch.ucf -sd ".;ipcore_dir" stopwatch.xst

1. ascii 文件

2.列出 所有的hdl文件,以便上传至设计

3.每行一个源文件

4.通常具有 .prj 扩展名

hdl 语法

<hdl_language> <compilation_library> <source_file>

hdl_language:

1.指出是hdl还是verilog

2.是否可以混合编译 vhd verilog

compilation_library

1.指定hdl需要的逻辑库

2.默认逻辑库是 work

source_file:

1.指定hdl 源文件

2.使用绝对路径还是相对路径

3.