2018-2019-1 20165235 《信息安全系统设计基础》第五周学习总结

教材学习内容总结

随机访问存储器

- 每个DRAM芯片被连接到内存控制电路,为了读出超单元(i,j)的内容,内存控制器将地址i发送给DRAM然后是列地址j,DRAM把超单元的内容发回给控制器作为响应。其中行地址称作RAS,列地址乘作CAS。

- 通过将多个内存模块连接到内存控制器,能够聚合成主存。当控制器收到一个地址A时,控制器选择包含A的模块k,将A转换成它的(i,j)形式,并将(i,j)发送给模块k。

- 系统总线;连接CPU和I/O桥接器。内存总线:连接I/O桥接器和主存。i/O桥接器将系统总线的电子信号翻译成内存总线的电子信息。

磁盘存储

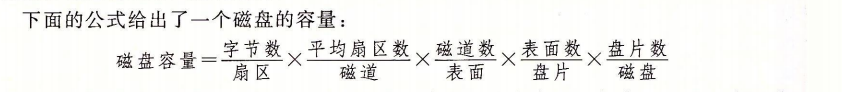

- 扇区:每一个磁道。

- 柱面:所有盘面上到主轴中心的距离相等的磁道的集合。

- 盘面,磁道,扇区三元组唯一的标示了对应的物理扇区。控制器上的硬件会解释这个三元组,将读/写头移动到适当的柱面,等待扇区移动到读/写头下,将读/写头感知的位放在控制器的一个小缓存区中,然后将它们复制到主存。

- 磁盘控制器必须对磁盘进行格式化,然后才能在该磁盘上存储信息。

固态磁盘

- 一个SSD封装有一个或多个闪存芯片和闪存翻译层组成,闪存芯片替代传统旋转磁盘中的机械驱动器,而闪存翻译层是一个硬件角色,扮演硬件控制器的角色。

局部性

- 局部性:倾向于引用邻近于其他最近引用过的数据项的数据项,或最近引用过的数据项本身。

- 高速缓冲存储器用来保护最近引用过的指令和数据项

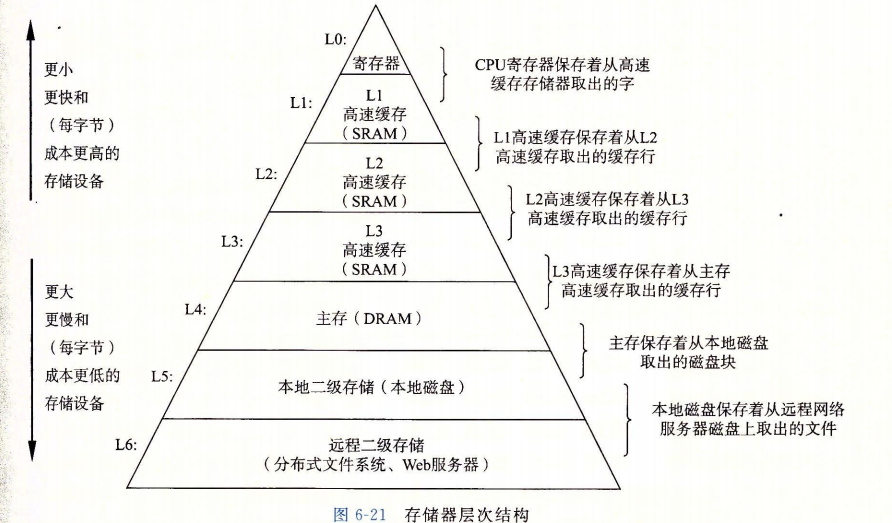

存储器结构中的缓存

- 使用高速缓存的过程称为缓存。

- 覆盖一个现存的块过程称为替换或者驱逐。

高速缓存存储器

- CPU寄存器文件和主存之间插入了一个小的SRAM高速缓存存储器(一级缓存L1)

- L1和主存之间插入一个更大的SRAM,称为L2,L2与主存之间又吵插入一个L3。

- 高速缓存的大小C指的是所有块之和C=SEB。

- 每行只有一行的(E=1)的高速缓存存储器称之为直接映射高速缓存。

- 从高速缓存抽取被请求的字的过程分为三步:1.组选择。2.行匹配。3.字抽取。

- 标记位和索引位连接起来唯一地标示了内存中的每一块。

- 多个块映射到同一个高速缓存组。

- 映射到高速缓存组的块由标记位唯一标识。

存储器存储结构:

磁盘容量计算公式:

教材学习中的问题和解决过程

- 问题1:我看了教材上缓存器命中有关的内容,有这个问题 :CPU对缓存中某个块进行写操作如何或者是什么时候去更新内存里的对应的数据呢?。

- 问题1解决方案:我查了资料,有这些说法:这个块先委托缓存保管,块进行写操作内存不予理睬,等该块要被驱逐出缓存时,再更新到内存,这称为写回。我同意这种说法,但是我个人认为每次当写回时每个缓存组都得确认自己是否被修改。

代码托管

其他(感悟、思考等,可选)

在本周学习中,我对教材430页的直接映射高速缓存中对每次读不同地址是否命中不是很理解。通过上网也没能找到好方法,最后结合教材429页的表格才弄懂了这部分内容。本周学习对430页之后的内容还没有学习,在下周学习中一定学会。