1基础理论部分

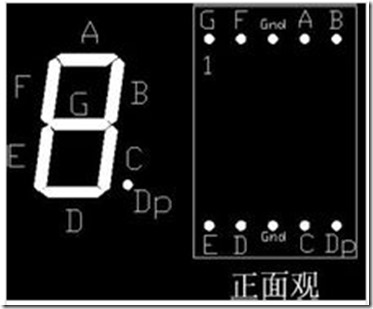

led数码管是由多个发光二极管封装在一起组合的“8”字型的器件,引线内部已经完成,如下图10.1所示,图10.2为实物图。

图10.1 数码管内部结构

那么我们想要控制数码管的亮灭,其实也就是控制发光二极管的亮灭,分别用高低电平去控制。对于数码管来说,读者若是学过单片机及其他MCU的话,其实都知道数码管的控制有两个信号是比较重要的,一个是段选信号,一个是位选信号,位选信号是针对有多个数码管时,需要控制哪一个数码管发亮,段选就是控制数码管显示什么数字。

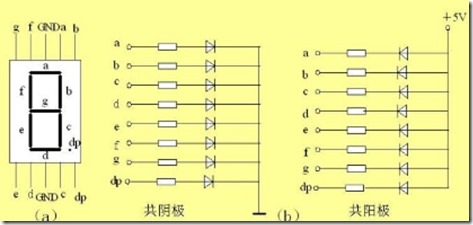

那么在购买数码管的时候,往往买回来时上面没有标注各引脚信息。这时不要慌,首先你购买时要分清共阳极还是共阴极数码管,共阳极和共阴极数码管电路示意图如图10.2所示。然后可以利用万用表打到“二极管”档位,然后万用表正极接触数码管一个引脚,负极去挨个触碰其他引脚,直到数码管发亮时,可以记录对应的引脚信息即可。

图10.2 数码管共阳和共阴极电路图

1.1 静态显示

静态驱动也称直流驱动。静态驱动是指每个数码管的每一个段码都由一个I/O端口进行驱动,或者使用如BCD码二-十进制译码器译码进行驱动。静态驱动的优点是编程简单,显示亮度高,缺点是占用I/O端口多,如驱动5个数码管静态显示则需要5×8=40根I/O端口来驱动。

1.2 动态显示

动态驱动是将所有数码管的8个显示笔划"a,b,c,d,e,f,g,dp"的同名端连在一起,另外为每个数码管的公共极COM增加位选通控制电路,位选通由各自独立的I/O线控制。

2 Verilog代码实现部分

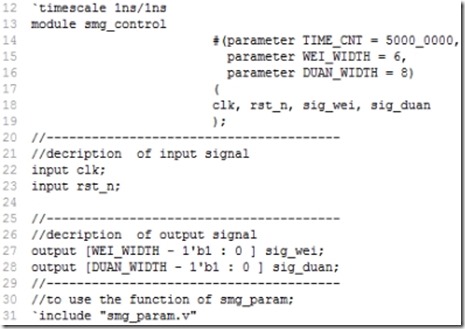

现在要实现数码管的静态显示功能,从0加到f,时间间隔为1s。封装接口为

2.1 smg_control模块

上述是整个模块的声明,并且调用了smg_param.v的文件,用于数码管解码参数的设置,关于include的用法可以参考其他语法书籍。

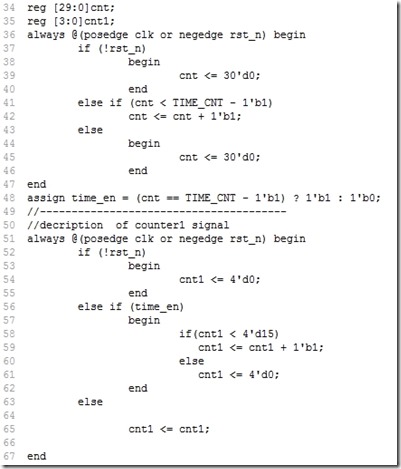

两个计数器,一个用于实现时钟计数1s,一个用于数码管编解码计数控制。

上述是实现数码管解码部分,注意smg_param.v中参数调用的方法。

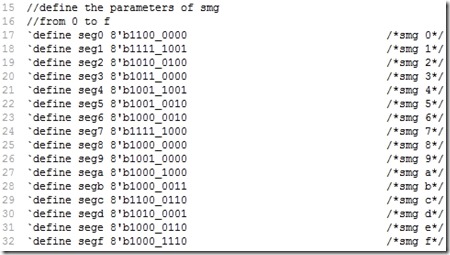

2.2 smg_param模块

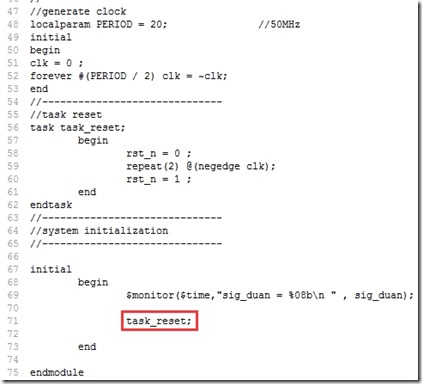

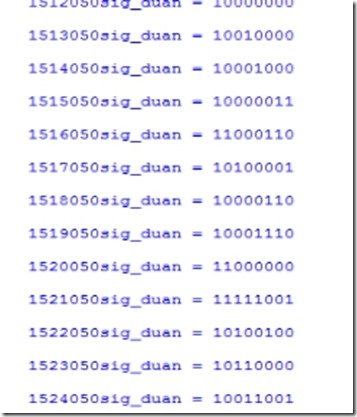

3 Modelsim仿真部分

仿真程序很简单,只需添加时钟和复位信号即可。测试的脚本文件如图10.3所示,因测试时将计数改到50,所以周期是1000ns。

图 10.3 测试脚本文件