时序约束实例详解

本篇博客结合之前的内容,然后实打实的做一个约束实例,通过本实例读者应该会实用timequest去分析相关的实例。本实例以VGA实验为基础,介绍如何去做时序约束。

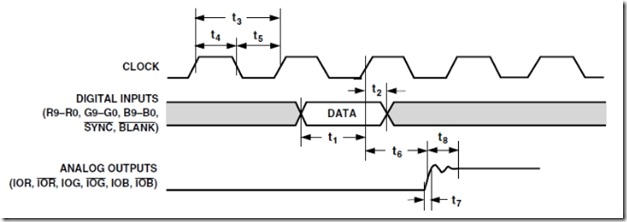

首先VGA这种情况属于供源时钟情况,不明白供源时钟的可以参看之前博客讲解。首先查看ADV7123的数据手册,查看其时序图。如下图所示,是建立时间和保持时间要求。

下图是时序图,可见t1和t2在时钟上升沿的位置,数据在时钟的上升沿进行采集。

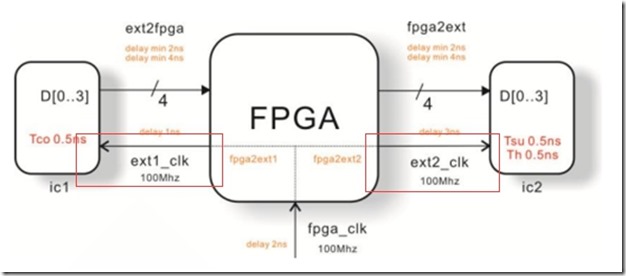

对于VGA实验来说,FPGA是发送端,ADV7123是接收端,如果传输的速率比较高的话,数据和时钟上升沿的严格对齐就要依靠PLL产生可调相位的时钟信号来保证,不过对于对于25MHz时钟通过较好的时序约束和分析后,则不必动用PLL。

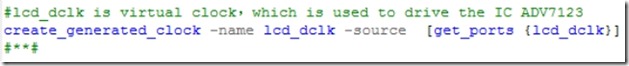

接下来需要产生虚拟时钟,对于reg2reg路径的分析,其时钟都是FPGA内部,不用产生虚拟时钟,但是对于pin2reg或者reg2pin这种情况,需要产生一个虚拟时钟,作为pin端的时钟来分析时序。如下图中的标注所示。

所以ADV7123和FPGA进行时钟相关的信号就是ADV7123的驱动时钟,明白这个信号之后,需要设置其虚拟时钟约束,如下图所示。

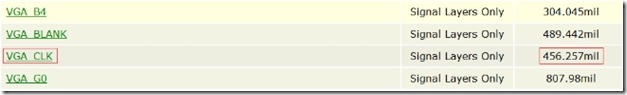

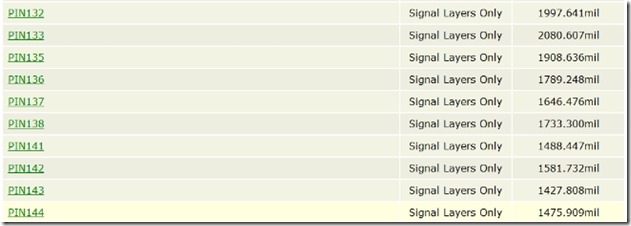

由于FPGA是相对于ADV7123为输出ADV7123所需要的信号,所以需要设置输出延迟约束。这一部分结合上一篇博客的分析,首先需要计算FPGA到ADV7123芯片的延迟,这一部分主要是PCB上面的信号走线延时。所以需要结合PCB走线来估计延迟时间。

打开altium designer,然后查看VGA模块的走线长度如下图1所示,长度大约是11.589mm。

图1 VGA模块走线长度

在FPGA核心板(笔者设计的一款学习板)上面的lcd_dclk的走线长度如下图2所示。长度大约是41.4mm。

图2 核心板走线长度

根据上述的计算,所以lcd_dclk总得走线长度 = 52.989mm。

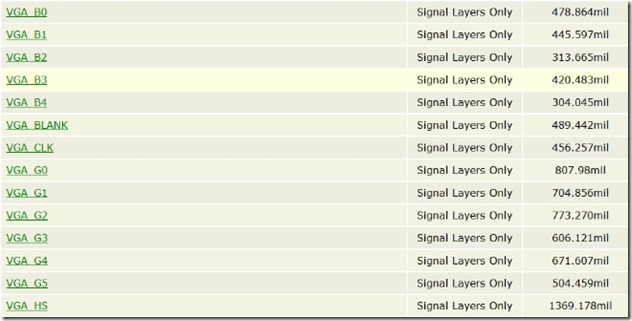

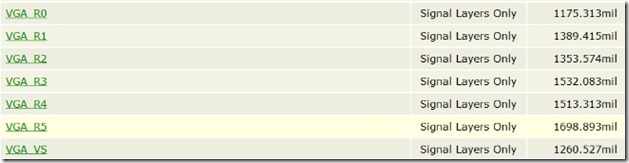

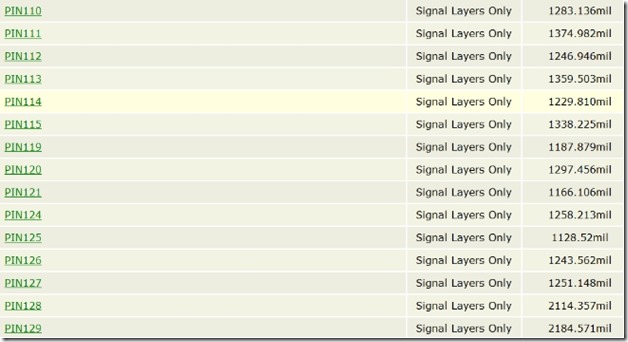

同样的道理,数据走线长度如下图3所示,此走线长度是VGA模块上面的长度,长度大约在7.72~43.152mm,那么对于核心板上面的走线模块长度如图4所示,大概长度约为28.65 ~ 53.32mm,总的长度为36.37mm~96.472mm,根据0.17ns/25.4mm,lcd_clk走线延迟0.35ns,数据总线延迟0.24ns~0.646ns。

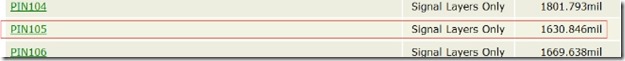

图3 各信号走线延迟

图4 核心板各信号走线延迟

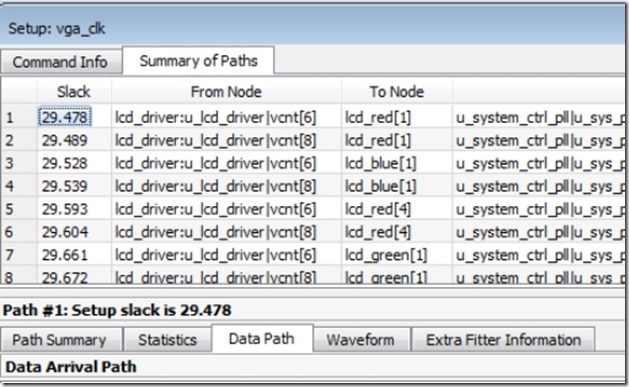

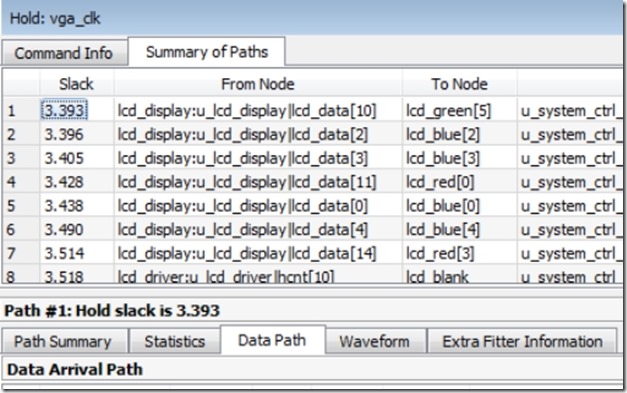

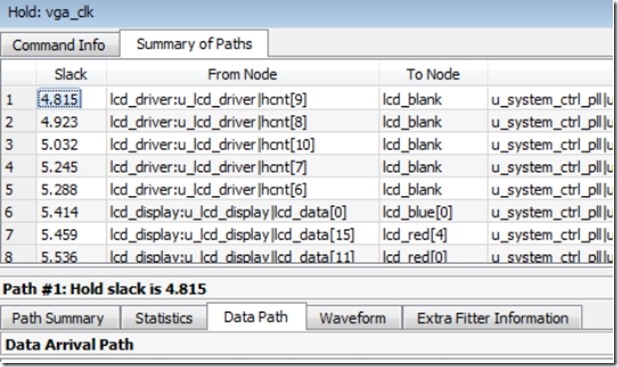

若是不考虑时钟偏移,那么进行时序分析得到的余量如图5所示。

图5 建立和保持余量

上述是计算完了FPGA到外部IC的延迟,但是还有时钟偏斜没有计算,那么需要用到set max/min delay 命令,对于lcd_dclk先估计一个范围,如0~5ns即可,这个范围肯定是满足要求,但是可能会不能够留有更多的余量。然后在将有时钟偏移的延迟时间代入set output delay的表达式中,此处利用公式将lcd_dclk 最大延迟设为3ns,lcd_dclk最小延迟设为1ns,那么考虑时钟偏斜的输出最大值 = 0.646 + 0.2 -3 = -2.154ns;输出最小值 = 0.24 - 1.5 - 1 = -2.26ns;

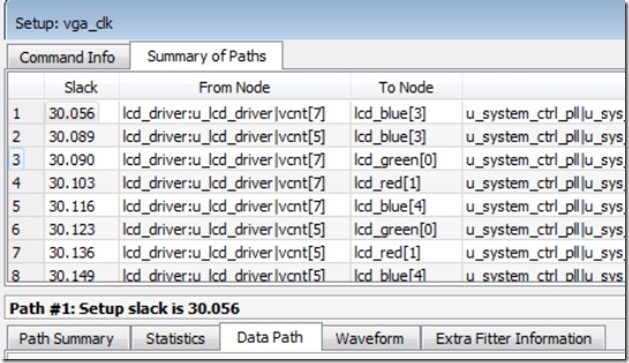

图6是约束后的建立余量和保持余量,可以看到满足时序要求,并保有很大的时序余量。

图6 建立余量和保持余量

//=======================================================================

更多详细的资料下载可以登录笔者百度网盘:

网址:http://pan.baidu.com/s/1bnwLaqF

密码:fgtb

//=======================================================================