COMPUTER ORGANIZATION AND ARCHITECTURE DESIGNING FOR PERFORMANCE NINTH EDITION

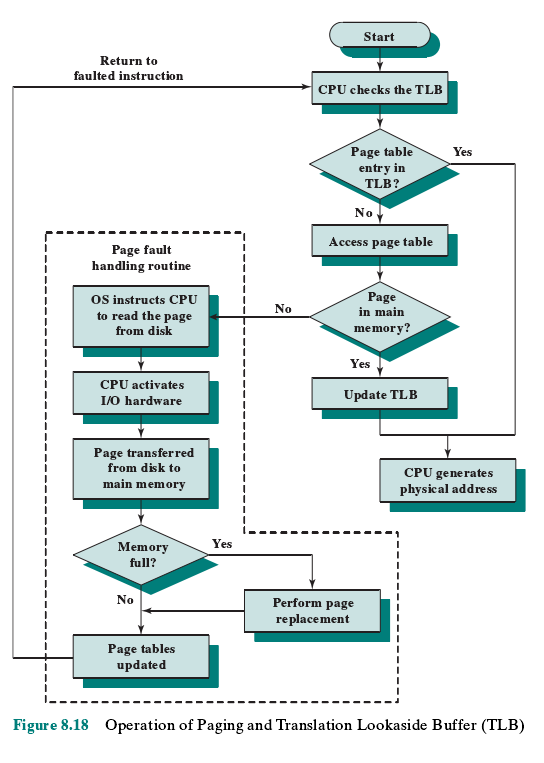

In principle, then, every virtual memory reference can cause two physical mem-

ory accesses: one to fetch the appropriate page table entry, and one to fetch the

desired data. Thus, a straightforward virtual memory scheme would have the effect

of doubling the memory access time. To overcome this problem, most virtual

memory schemes make use of a special cache for page table entries, usually called

a translation lookaside buffer (TLB). This cache functions in the same way as a

memory cache and contains those page table entries that have been most recently

used. Figure 8.18 is a flowchart that shows the use of the TLB. By the principle of

locality, most virtual memory references will be to locations in recently used pages.

Therefore, most references will involve page table entries in the cache. Studies of

the VAX TLB have shown that this scheme can significantly improve performance

[CLAR85, SATY81].

Note that the virtual memory mechanism must interact with the cache system

(not the TLB cache, but the main memory cache). This is illustrated in Figure 8.19.

A virtual address will generally be in the form of a page number, offset. First, the

memory system consults the TLB to see if the matching page table entry is present.

If it is, the real (physical) address is generated by combining the frame number with

the offset. If not, the entry is accessed from a page table. Once the real address is

generated, which is in the form of a tag and a remainder, the cache is consulted to

see if the block containing that word is present (see Figure 4.5). If so, it is returned

to the processor. If not, the word is retrieved from main memory.

The reader should be able to appreciate the complexity of the processor hard-

ware involved in a single memory reference. The virtual address is translated into

a real address. This involves reference to a page table, which may be in the TLB, in

main memory, or on disk. The referenced word may be in cache, in main memory,

or on disk. In the latter case, the page containing the word must be loaded into main

memory and its block loaded into the cache. In addition, the page table entry for

that page must be updated.