导言

如果学过单片机的同学应该不会陌生,学习51单片机时最经常听到的就是“最小系统”。

最小系统里面少不了晶振,否则单片机无法工作。

单片机需要晶振(时钟源)来工作,那么对于STM32芯片同样如此。

此外,同一个电路,时钟越快功耗越大,抗电磁干扰能力也随之变弱。

所以对于较为复杂的MCU一般都是采取多时钟源的方法来解决这些问题。

STM32是一块对于功耗可控的芯片,所以需要我们手动开启有关的时钟树,以方便后续的开发。

STM32的时钟树与时钟源

时钟源

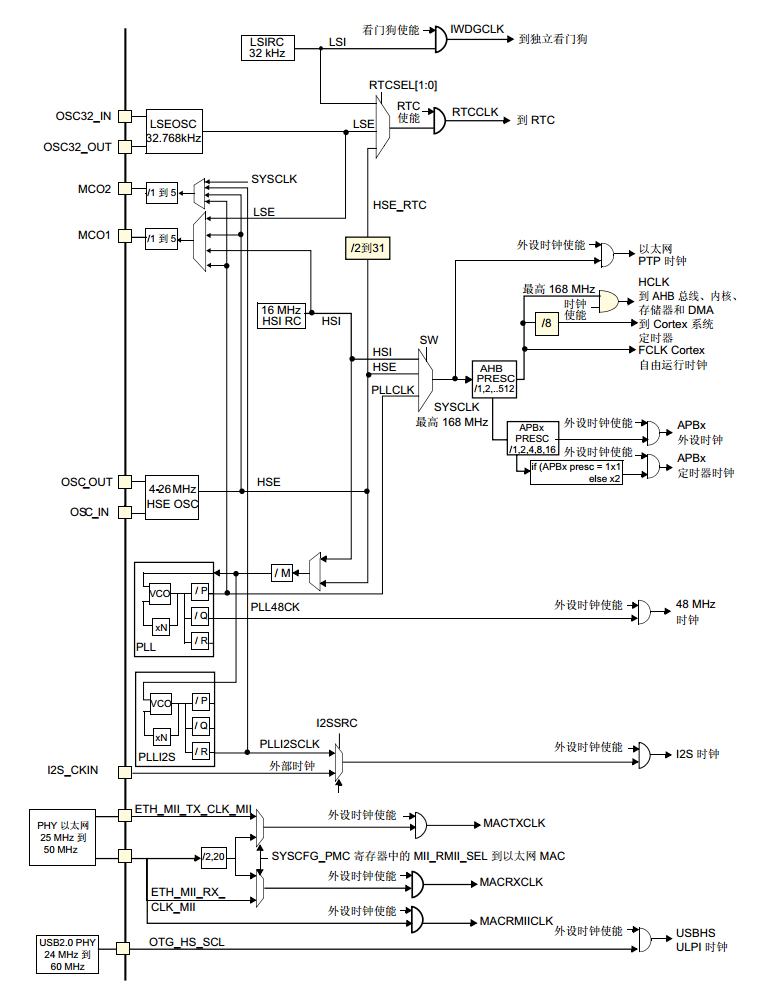

在STM32F4中,有5个最重要的时钟源,按来源分为内外部两种;按速率也可以分为高低速两种。

| 时钟源 | 含义 | 时钟速率 | 用途 |

| HSI | 高速内部时钟 | 16MHz | 可以直接作为系统时钟或者PLL输入 |

| HSE | 高速外部时钟 | 4~26MHz | 可以直接作为系统时钟 |

| LSI | 低速内部时钟 | 32KHz | 供给独立看门口和自动唤醒单元使用 |

| LSE | 低速内部时钟 | 32.768KHz | 主要是RTC(实时时钟)的时钟源 |

| PLL |

锁相环 (内部倍频器) |

可以是 HSI的二分频 HSE的一分频 或HSE的二分频 |

锁相环倍频输出,分为主PLL和专用PLL: 1)主PLL由HSE或HSI提供时钟信号,并且具有两个不同的输出时钟: ①PLLP:生成高速的系统时钟,最高180MHz;(STM32F429) ②PLLQ:生成USB OTG FS的时钟(48MHz)、随机数发生器和SDIO的时钟。 2)专用时钟PLL(PLLI2S),用于生成精确时钟,在I2S接口实现高品质音频输出。 |

时钟树

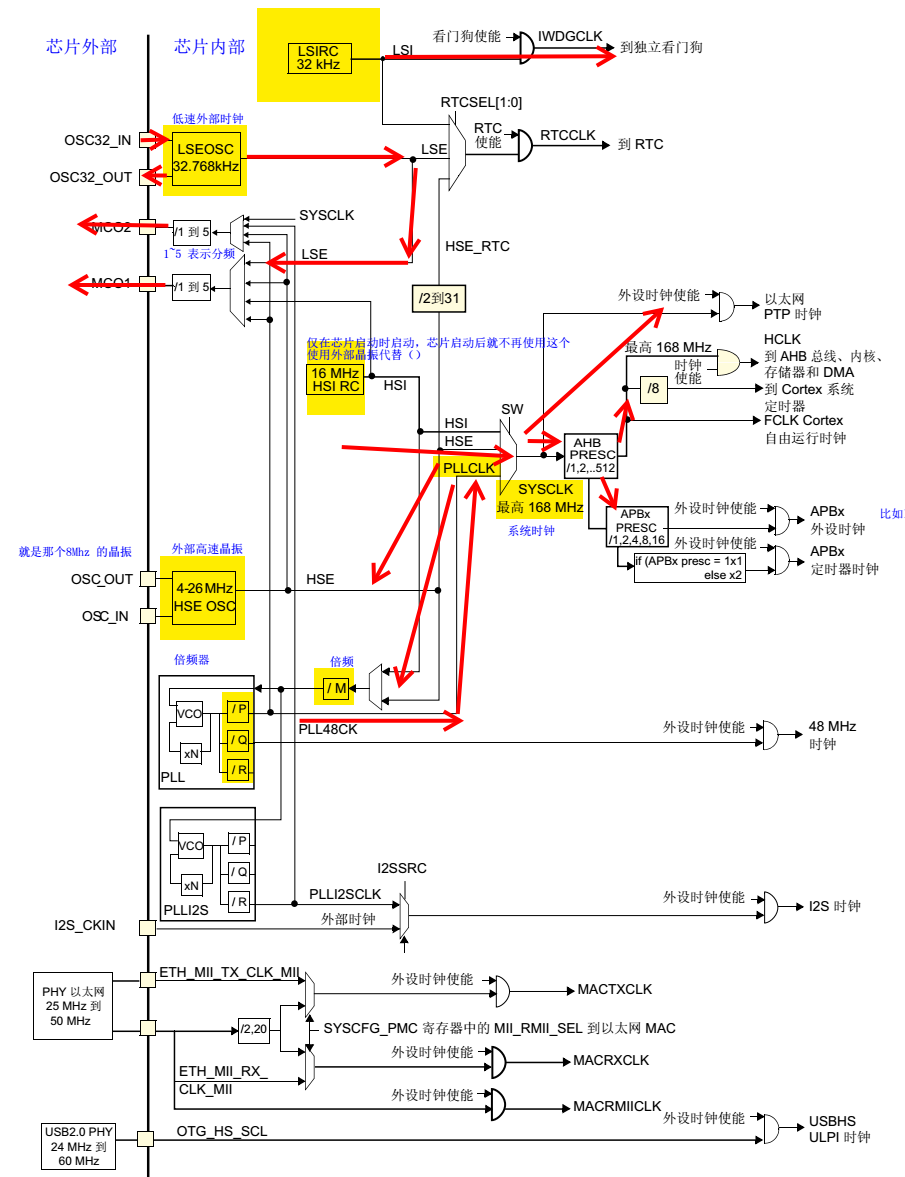

由于STM32复杂的时钟体系,有人形象地称下图为时钟树。

当初学习到这个地方的时候,本人也觉得混乱。

但其实只要抓准5个时钟源,“顺藤摸瓜”就可以捋清关系了。

下图是笔者根据自己开发板的情况画的简单线路图。

了解完以上的关系就不难理解为什么任何片内外设在使用之前,必须使能相应的时钟。

附时钟频率的计算:

SYSCLK = Fvco/pllp = Fs*(plln/(pllm*pllp));

Fvco:VCO频率

SYSCLK:系统时钟频率

Fusb:USB,SDIO,RNG等的时钟频率

Fs:PLL输入时钟频率,可以是HSI,HSE等.

plln:主PLL倍频系数(PLL倍频),取值范围:64~432.

pllm:主PLL和音频PLL分频系数(PLL之前的分频),取值范围:2~63.

pllp:系统时钟的主PLL分频系数(PLL之后的分频),取值范围:2,4,6,8

pllq:USB/SDIO/随机数产生器等的主PLL分频系数(PLL之后的分频),取值范围:2~15.