第一步要看的肯定是pin planner ,这个是黑金四代EP4CE15F17C8的视图

先就是发现他们pin有不同的颜色区域,分别对应不同的bank,应该是有的设计里面要求pin在同一个bank吧(首先这么猜想,后面再验证),再看不同的圈圈三角形代表什么意思 View--> Pin Legend

图中几个棕色背景的pin就是使用过得,鼠标放到pin上就会自动显示 pin name

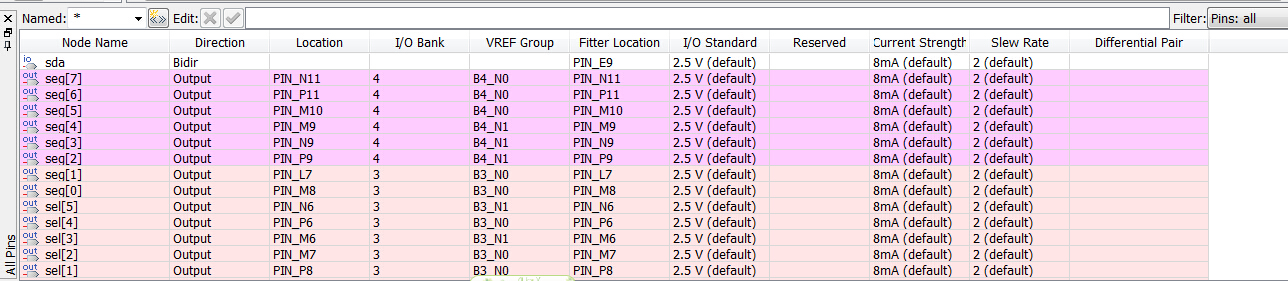

再后面就是all pin list 窗口

此窗口中可以指定pin位置,电压,电流等一系列信息,每一个bank只有一种电压,那么是不是指定多少电压,电流就一定输出这么多呢? 后续讨论

细心的朋友会发现这个sda怎么没有bank,我查了一下,发现我的tcl里面没有对sda进行约束,Q对这个管脚做了一个随机分配—— 这是一个USB的数据信号线。

网上有朋友简要的说明了一下 :如果I/O standard設2.5V,但它的VREF是接1.8V那麼當然該I/O打不出2.5V。

Current strength並非越大越好,過強的I/O驅動能力會導致較強的SSN與overshooting issue。但過弱的Current strength可能多顆FPGA互聯,或外接較多fan-out時會推不動