在上一篇博文中 verilog中连续性赋值中的延时中对assign的延时做了讨论,现在对always块中的延时做一个讨论。

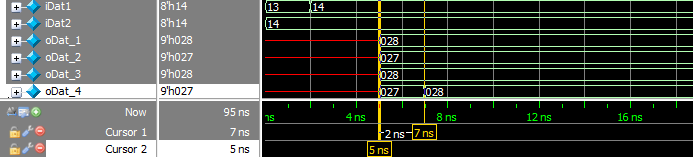

观测下面的程序,@0时刻,输入的数据分别是0x13,0x14 。

@2时刻,输入数据分别是0x14,,0x14 。

四个输出应该是什么样子呢?

1 always @ (iDat1 or iDat2) 2 #5 oDat_1 = iDat1 + iDat2; 3 4 always @ (iDat1 or iDat2) 5 oDat_2 = #5 iDat1 + iDat2; 6 7 always @ (iDat1 or iDat2) 8 #5 oDat_3 <= iDat1 + iDat2; 9 10 always @(iDat1 or iDat2) 11 oDat_4 <= #5 iDat1 + iDat2;

直接上图吧

作为阻塞性赋值语句,延时放在前面,就是先延时,再取值赋值。所以oData_1延时之后取了新值。

延时放在后面,就是先取值,再延时赋值。oData_2 是先取了旧值,再延时赋值,中间如果等号右边有变化,被阻塞了。所以oData_2是旧值 。

1 always @ (iDat1 or iDat2) 2 #5 oDat_1 = iDat1 + iDat2; 3 4 always @ (iDat1 or iDat2) 5 oDat_2 = #5 iDat1 + iDat2;

作为非阻塞性赋值语句,延时放在前面,就是先延时,再取值赋值。所以oData_3延时之后取了新值。

延时放在后面,就是先取值,再延时赋值。oData_4 是先取了旧值,再延时赋值,中间如果等号右边有变化,没有被阻塞,新建event,所以oData_2是旧值之后再更新为新值 。

1 always @ (iDat1 or iDat2) 2 #5 oDat_3 <= iDat1 + iDat2; 3 4 always @(iDat1 or iDat2) 5 oDat_4 <= #5 iDat1 + iDat2;

所以,这以后写TB的时候要慎重啊。

欢迎加入: FPGA广东交流群:162664354

FPGA开发者联盟: 485678884