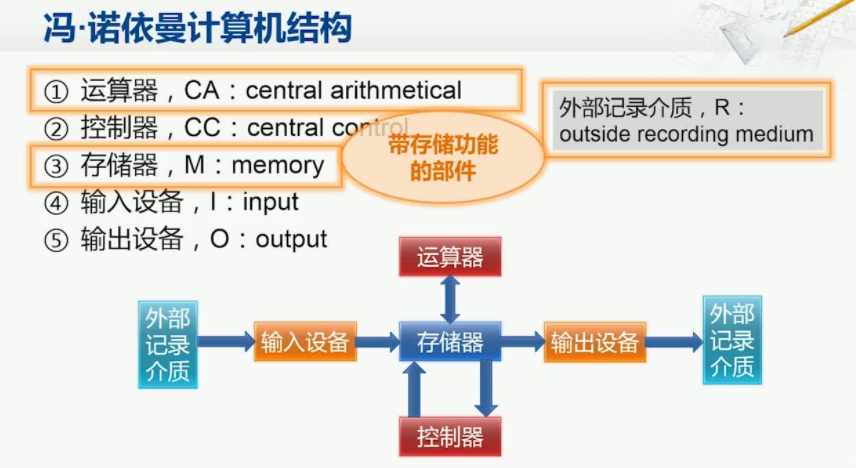

先来看看冯诺依曼计算机结构

老师:

如果CPU爱好哲♂学

他肯定要问 我要运算的的数据从哪里来,又到哪里去。

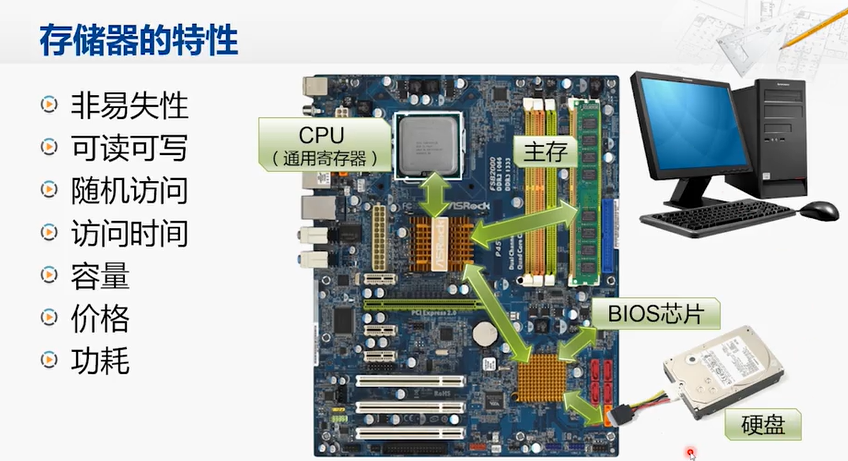

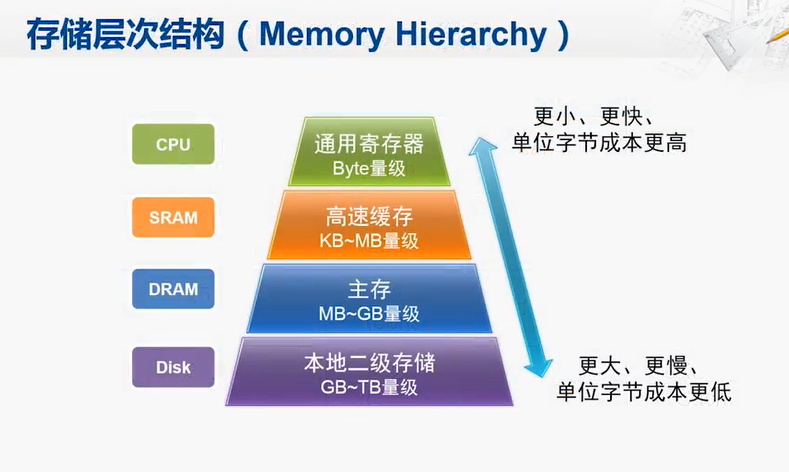

易失性: 储存 CPU中的通用寄存器

- 非易失性:BIOS 硬盘

- 可读也可写

BIOS:只读,写要借助特殊的设备 - 随机访问

+访问时间 主存高于硬盘

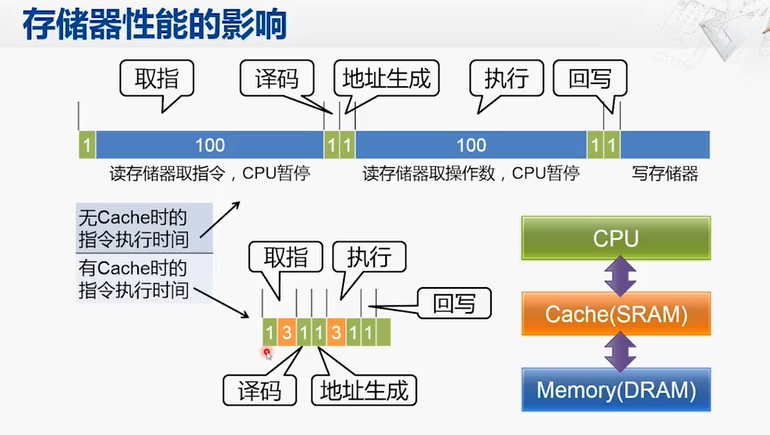

加加加(Cache)

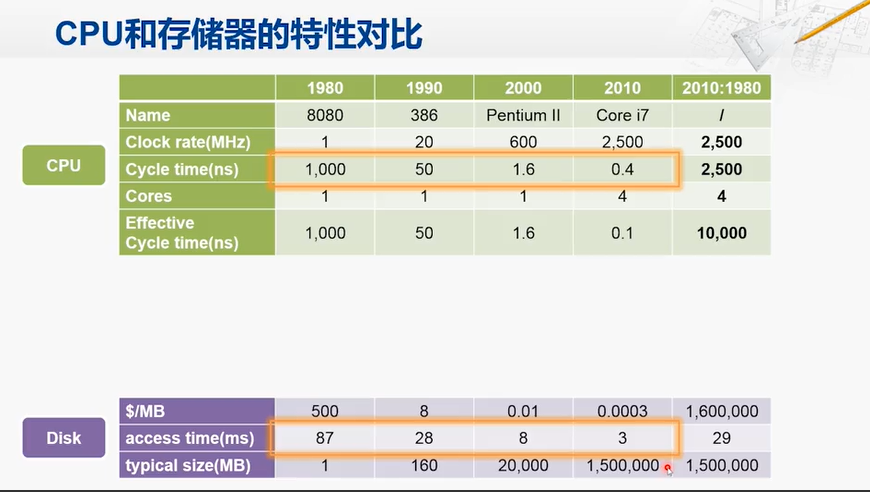

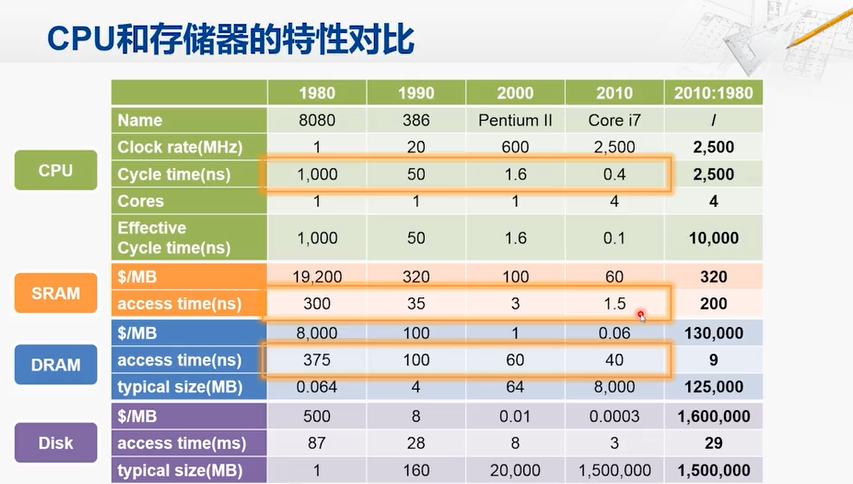

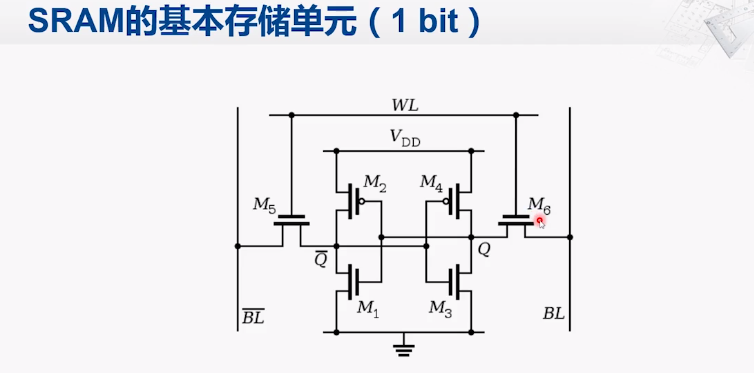

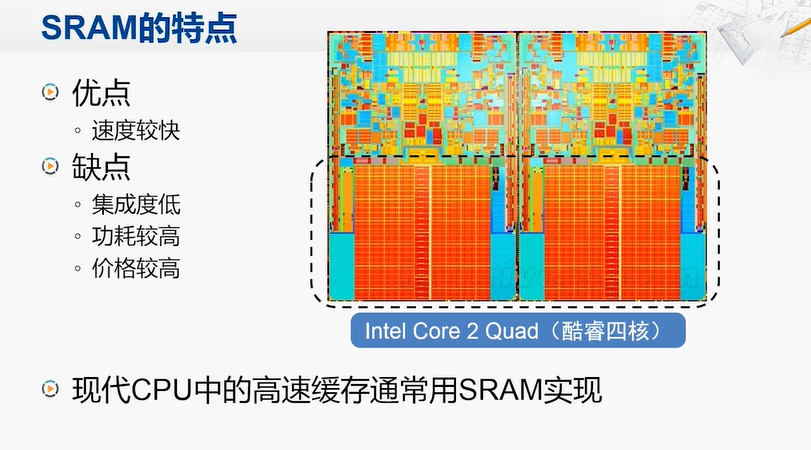

看表SRAM

2010年SRAM价格是DRAM价格的1000倍

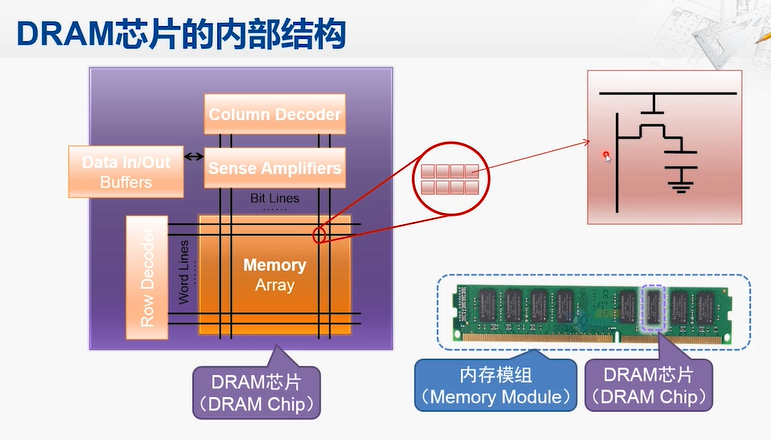

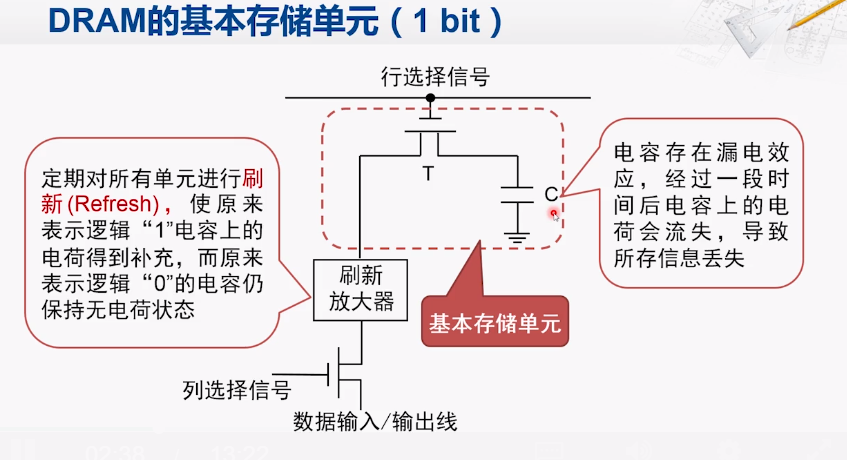

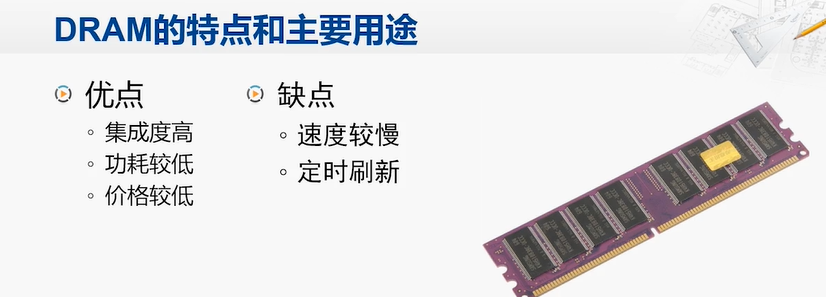

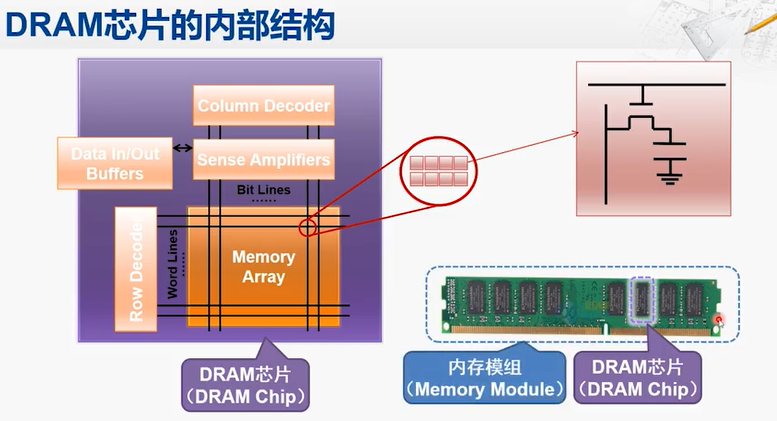

DRAM和SRAM###

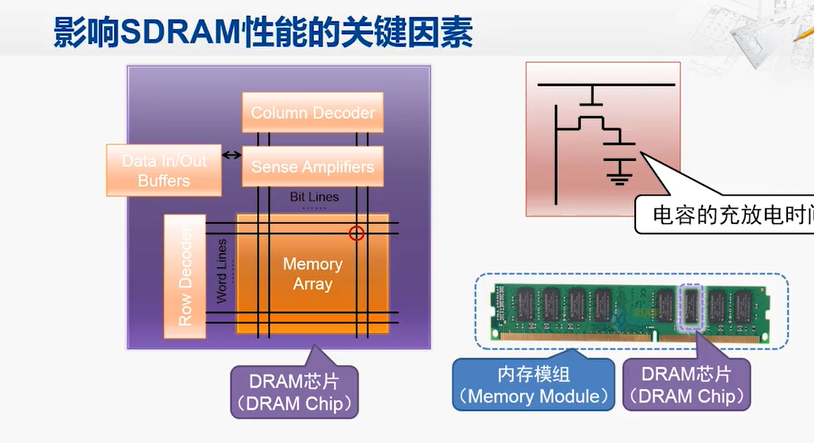

为什么DRAM慢而SRAM快

通过行列选择信号

在SDRAM上进行的改进

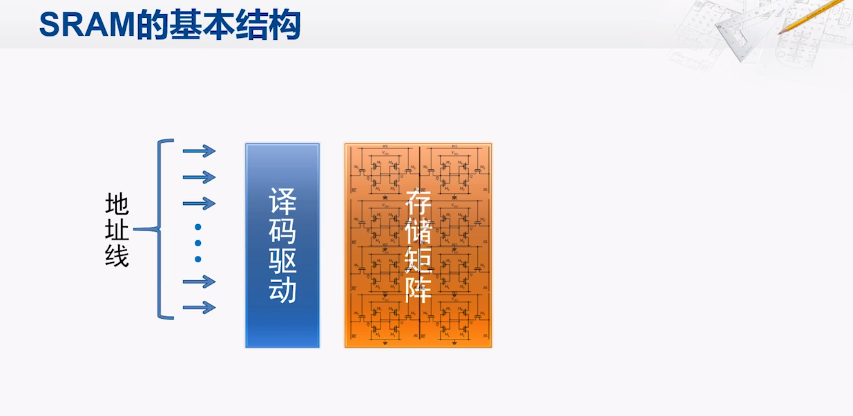

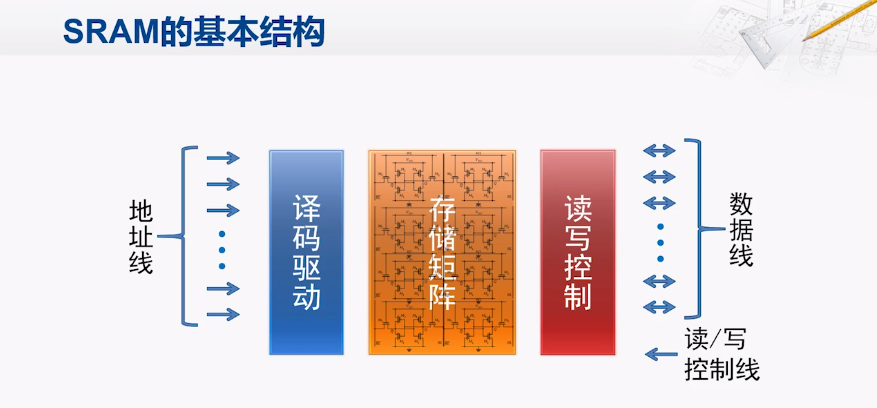

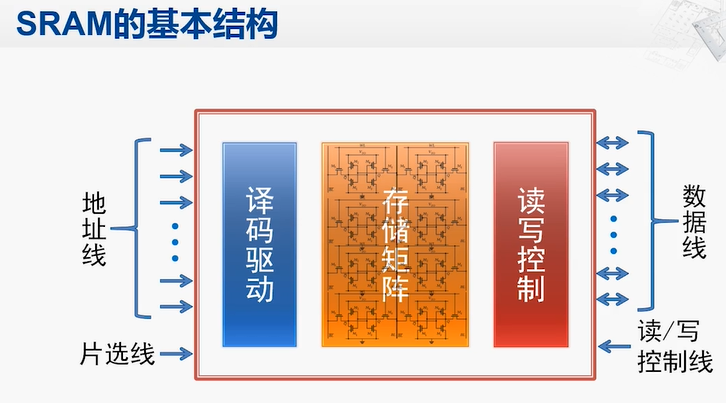

SRAM###

主存的工作原理###

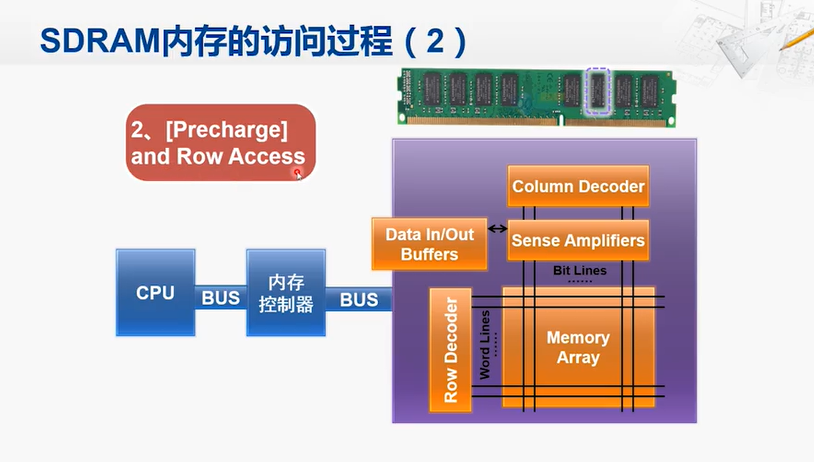

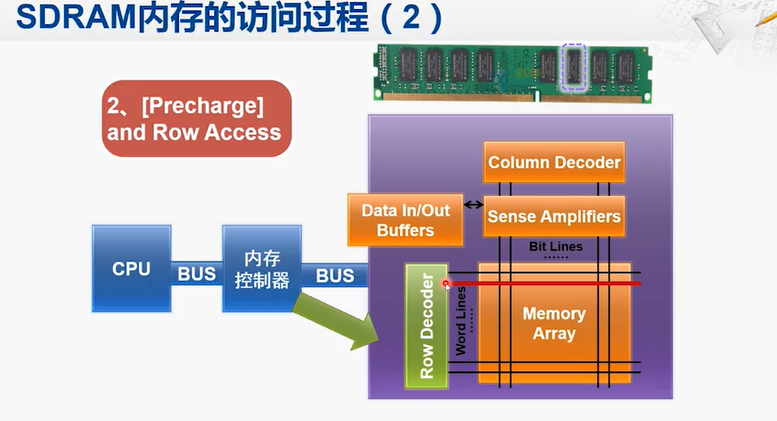

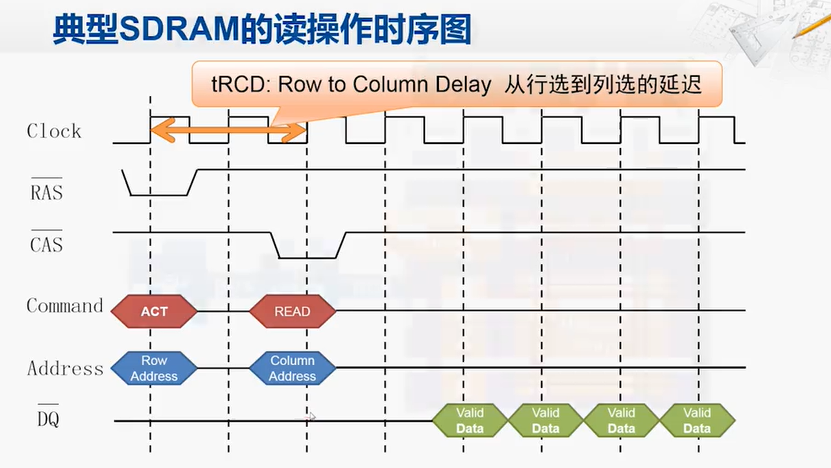

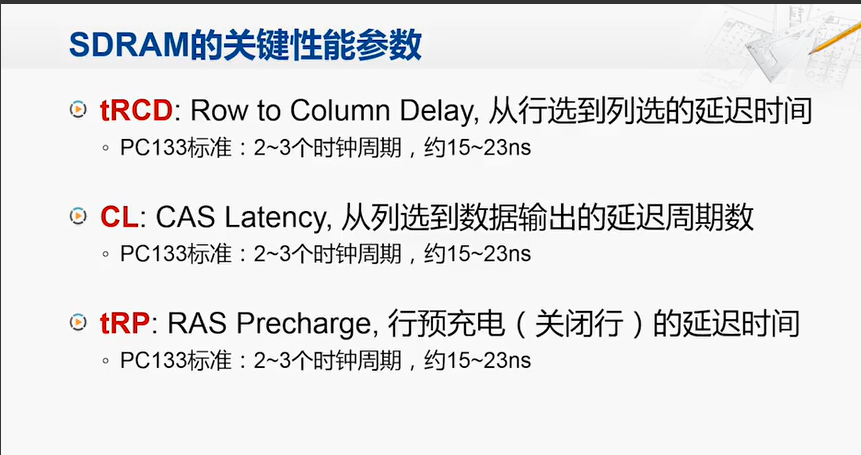

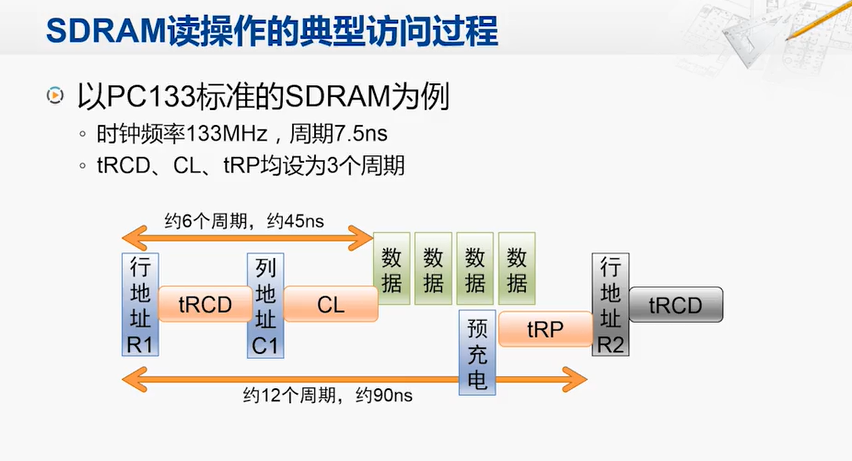

SDRAM:同步的DRAM

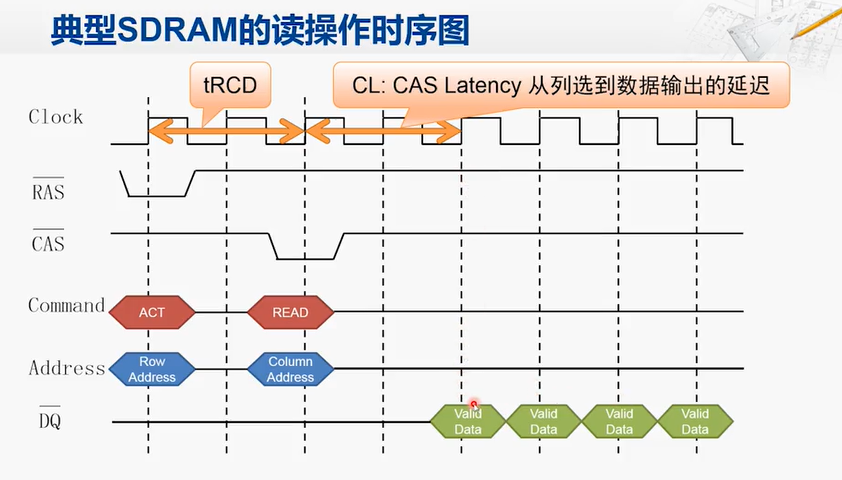

激活(行访问)

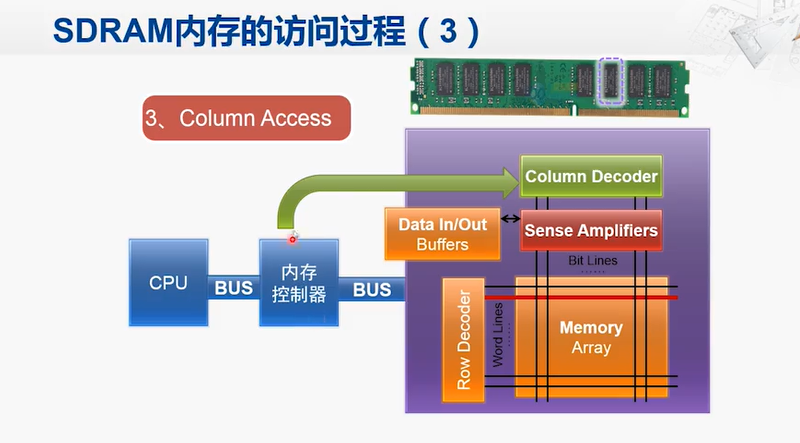

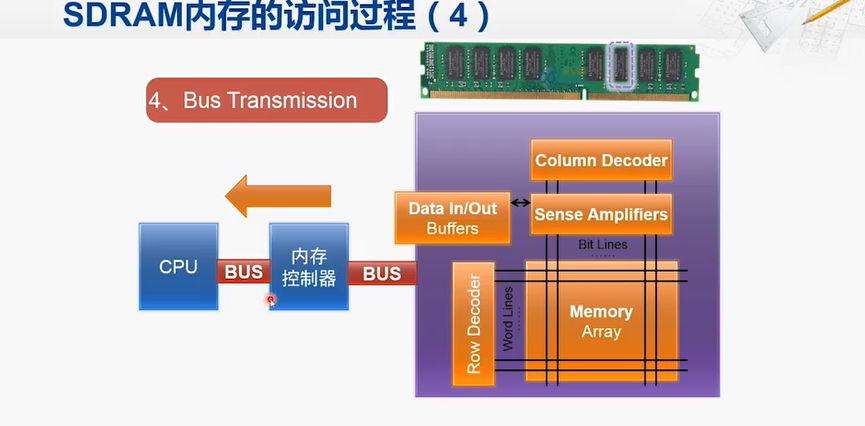

列访问

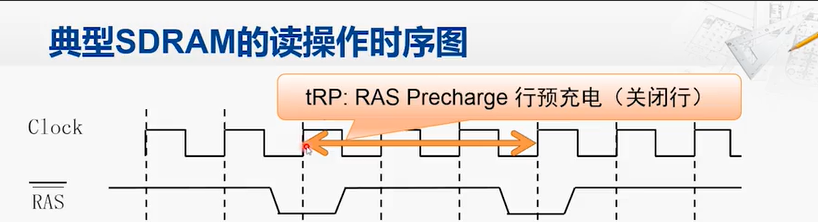

把激活的这一个过程称为预充电

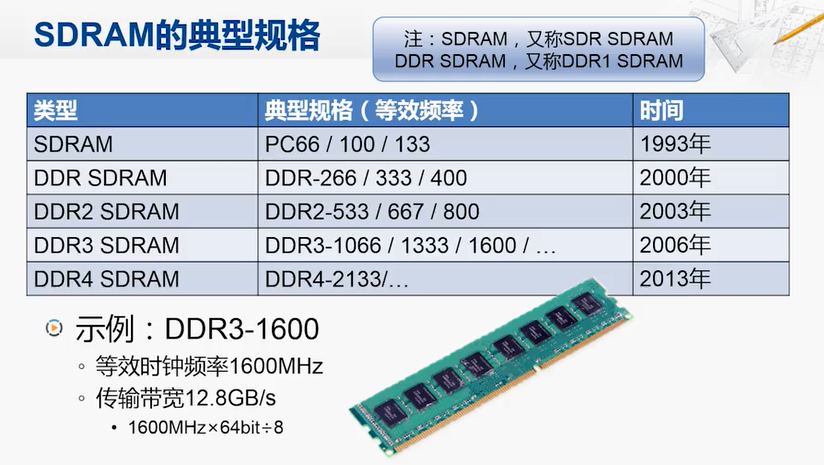

主存技术的发展###

内存行选的时间

红点是 升级后的第一代

cache的原理###

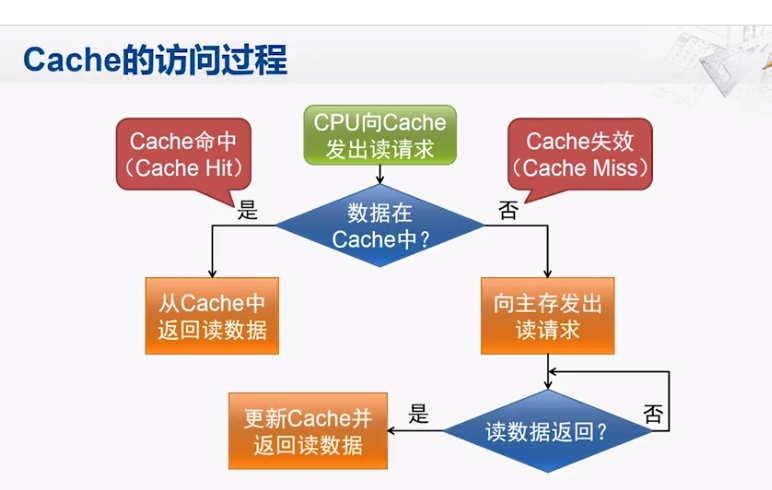

Cache的访问过程###

估计是打错了。

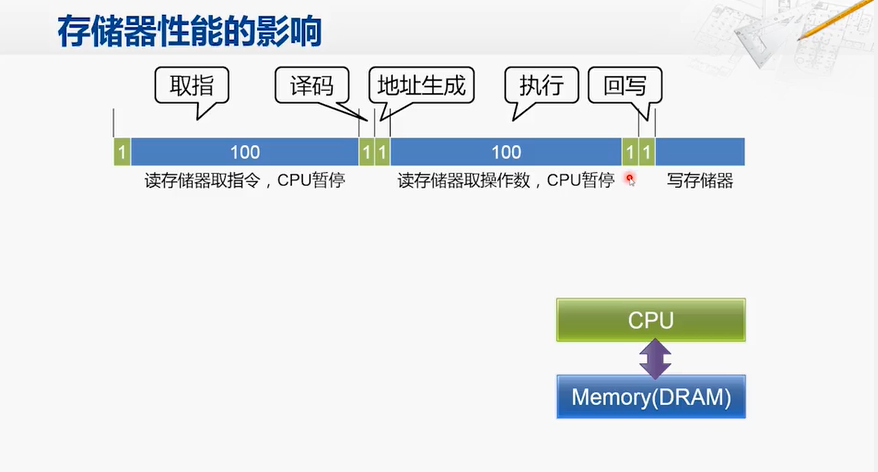

性能不高

性能高

Cache的组织结构###

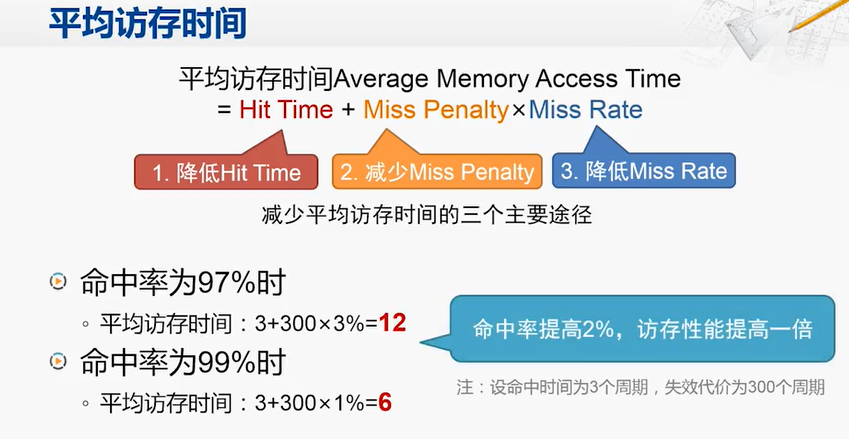

- 平均访存时间

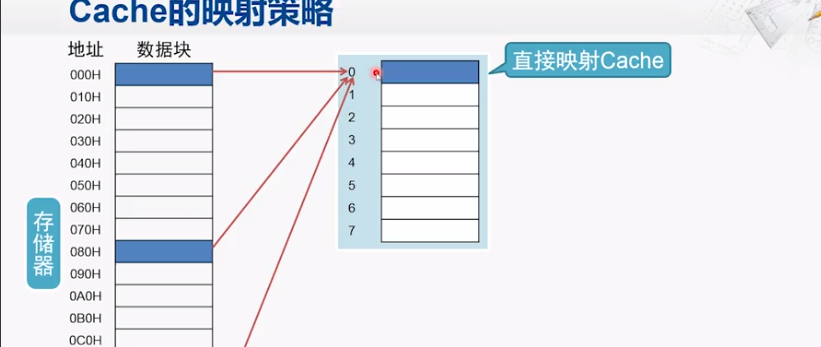

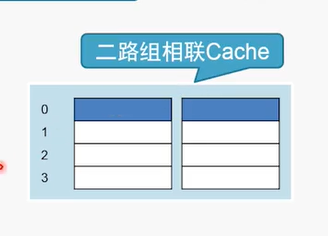

Cache的映射策略###

直接映射

全相连的cache 控制逻辑特别复杂

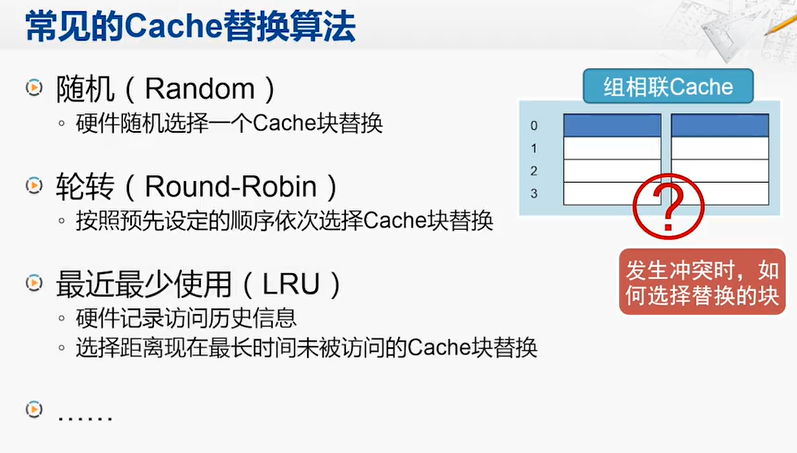

常见的Cache的替换算法

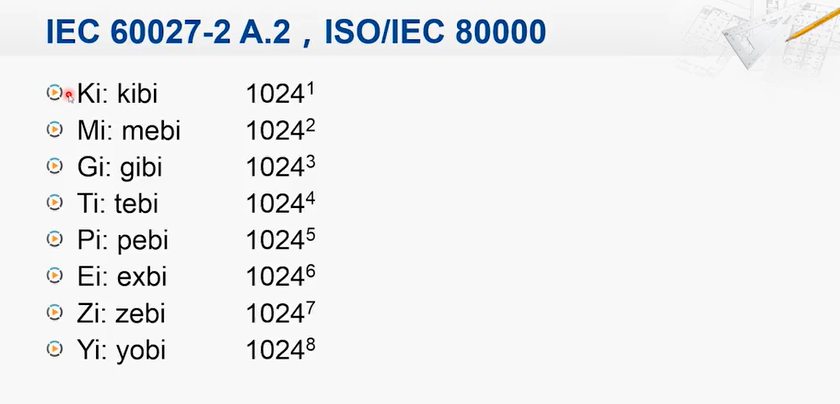

存储容量的计算###

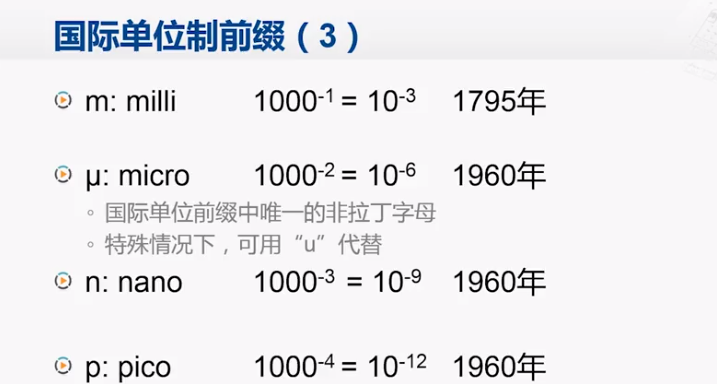

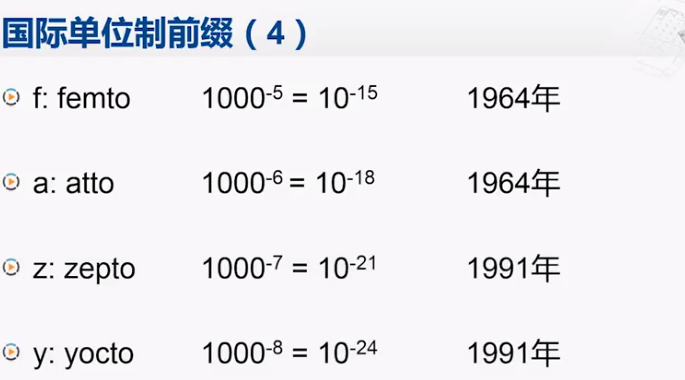

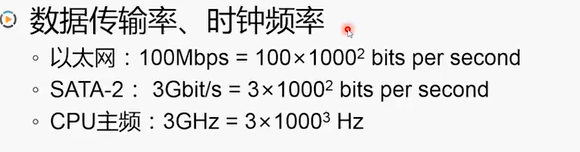

单位的前缀

计算的问题#

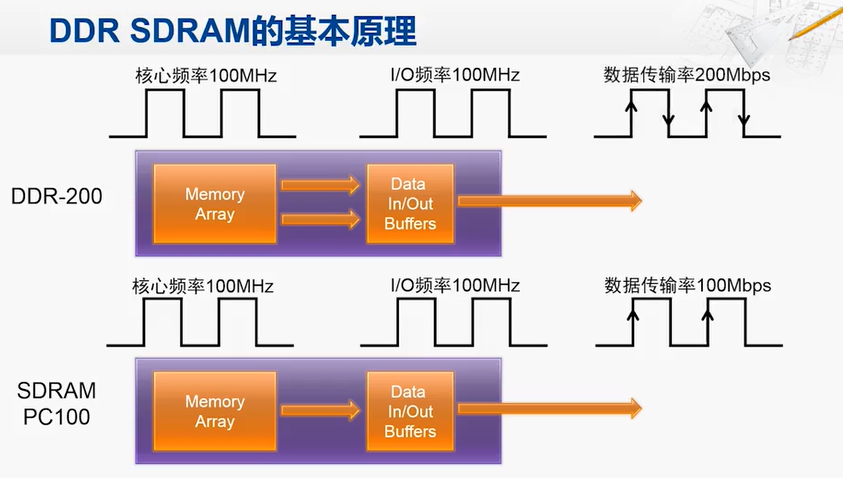

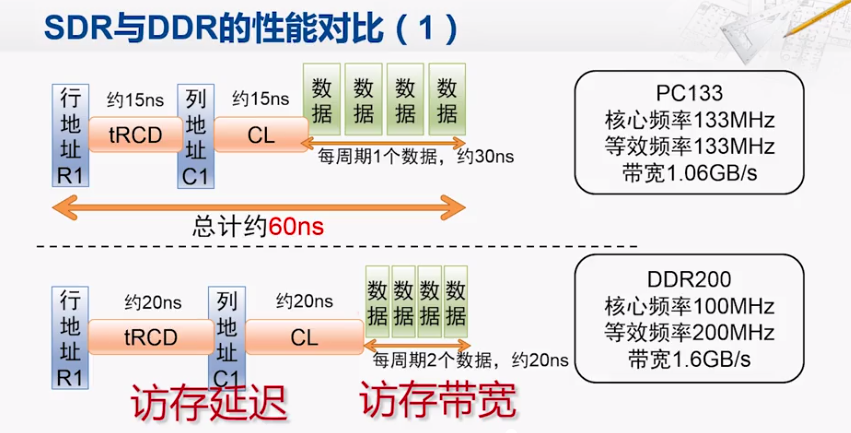

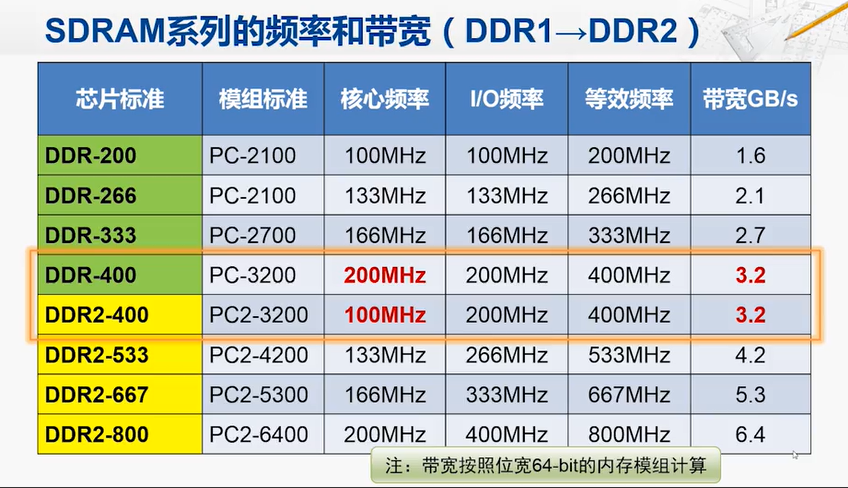

等效时钟频率X数据宽度 /8 == 峰值带宽

这是我自己的理解

峰值带宽=等效频率*数据宽度/8

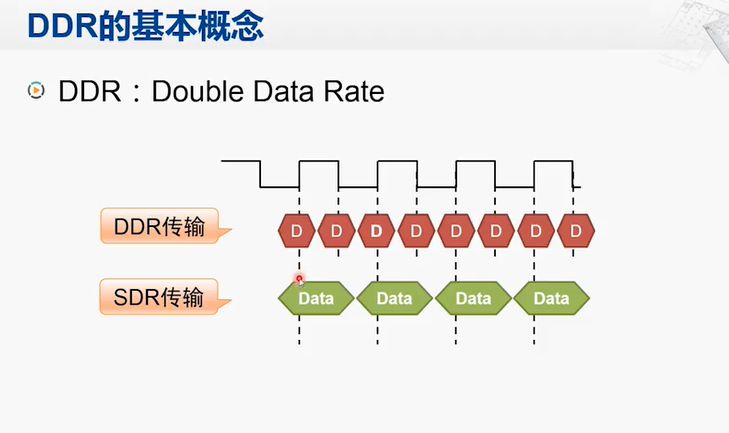

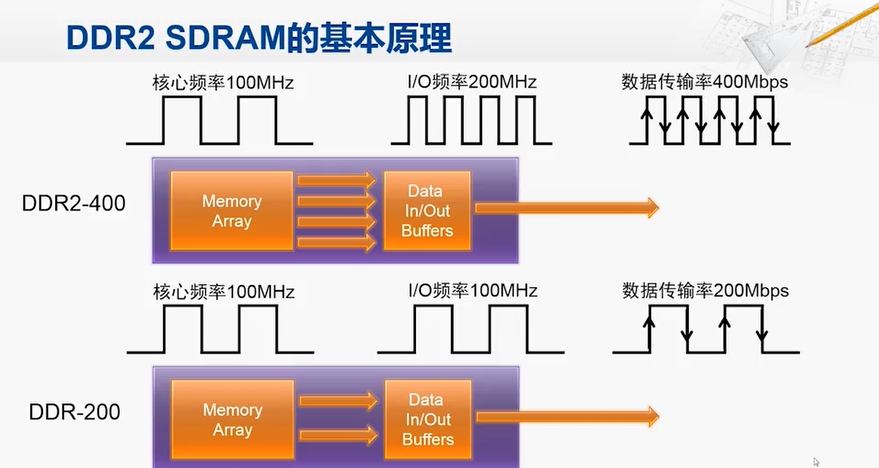

对于SDR RAM: 核心频率OI频率等效频率

对于DDR : 2核心频率==2OI频率==等效频率

对于DDR2:4核心频率==2OI频率==等效频率

对于DDR3:8核心频率==2OI频率==等效频率

接口时钟频率是向外写数据的信号频率,SDR只在上升沿写数据,所以是相等,其余都是2倍关系

因为要写出更多的数据就要读更多的数据。

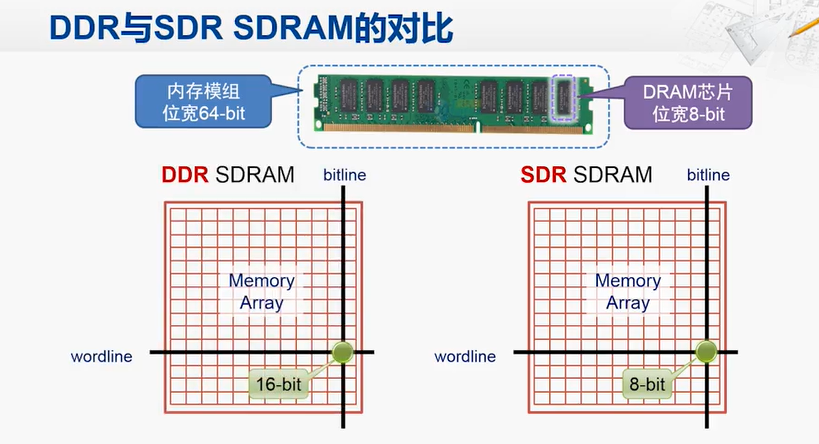

SDR 一次读一位

DDR读两位,然后类推

所以DDR3 就是读8位数据了,

所以OI频率和核心频率不相等

这里的每位指数据位宽