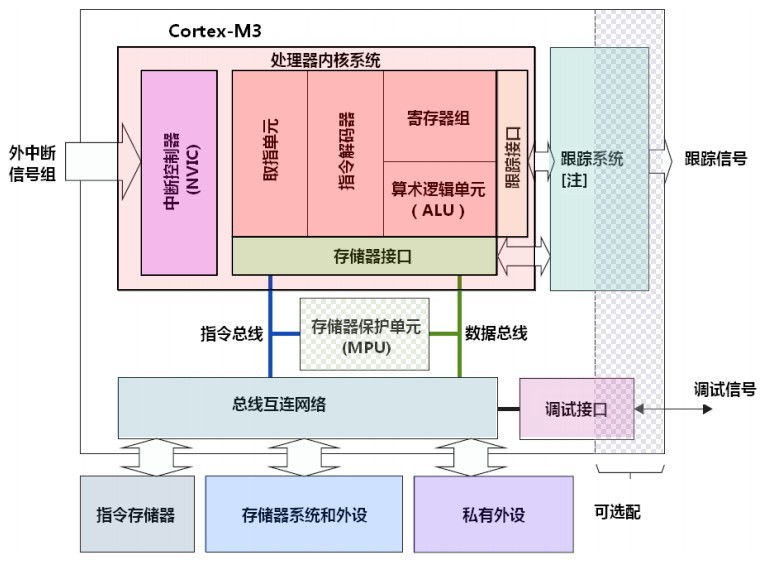

Cortex-M3是一个 32位处理器内核。内部的数据路径是 32位的,寄存器是 32位的,存储器接口也是 32 位的。CM3 采用了哈佛结构,拥有独立的指令总线和数据总线,可以让取指与数据访问并行不悖。这样一来数据访问不再占用指令总线,从而提升了性能。为实现这个特性, CM3内部含有好几条总线接口,每条都为自己的应用场合优化过,并且它们可以并行工作。但是另一方面,指令总线和数据总线共享同一个存储器空间(一个统一的存储器系统)。

比较复杂的应用可能需要更多的存储系统功能,为此CM3提供一个可选的MPU,而且在需要的情况下也可以使用外部的 cache。另外在CM3中,Both小端模式和大端模式都是支持的。

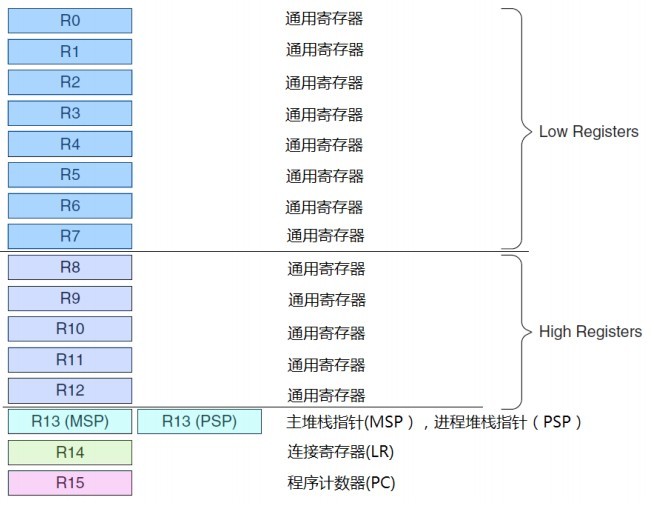

寄存器组 : 处理器拥有R0-R15的寄存器组,

其中R13最为堆栈指针SP,SP有两个,但是同一时刻只能有一个可以看到,这就是所谓的“banked”寄存器。

R0-R12都是32位通用寄存器,用于数据操作。

但是注意:绝大多数 16位Thumb指令只能访问R0-R7,而 32位 Thumb-2指令可以访问所有寄存器。

R13 堆栈指针 Cortex-M3拥有两个堆栈指针,然而它们是 banked,因此任一时刻只能使用其中的一个。

主堆栈指针(MSP):复位后缺省使用的堆栈指针,用于操作系统内核以及异常处理例程(包括中断服务例程)

进程堆栈指针(PSP):由用户的应用程序代码使用。

堆栈指针的最低两位永远是0,这意味着堆栈总是4字节对齐的。

R14:连接寄存器--当呼叫一个子程序时,由R14存储返回地址

R15:程序计数寄存器--指向当前的程序地址,如果修改它的值,就能改变程序的执行流(这里有很多高级技巧)

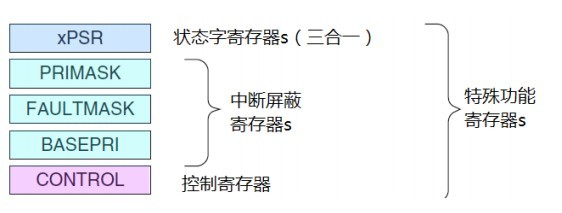

程序状态字寄存器组(PSRs)

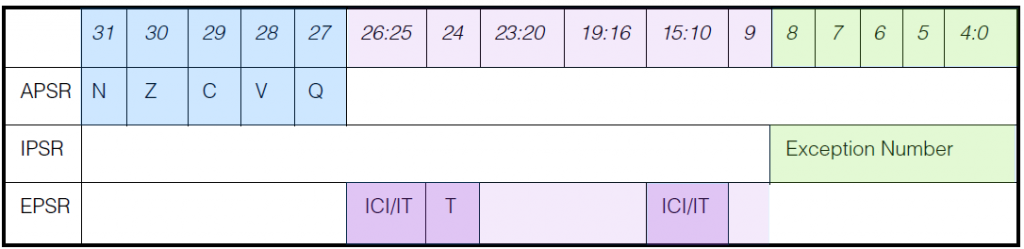

程序状态寄存器在其内部又被分为三个子状态寄存器:

应用程序PSR(APSR)

中断号PSR(IPSR)

执行PSR(EPSR)

PRIMASK,FAULTMASK和BASEPRI 控制中断和异常的开启和屏蔽 <只有在特权级下,才允许访问这3个寄存器>

PRIMASK = 1后 只有NMI和硬fault可以响应,默认为0

FAULTMASK = 1 后只有NMI和硬fault可以响应,默认为0

BASEPRI:优先级号大于等于此值的中断都被屏蔽 <0 : 无效果 >

控制寄存器(CONTROL)

CONTROL[0]=1,用户级的线程模式

CONTROL[0]=0,特权级的线程模式

CONTROL[1]=1,选择使用PSP

CONTROL[1]=0,选择使用MSP

存储器映射