vt-d spec

通用平台的拓扑

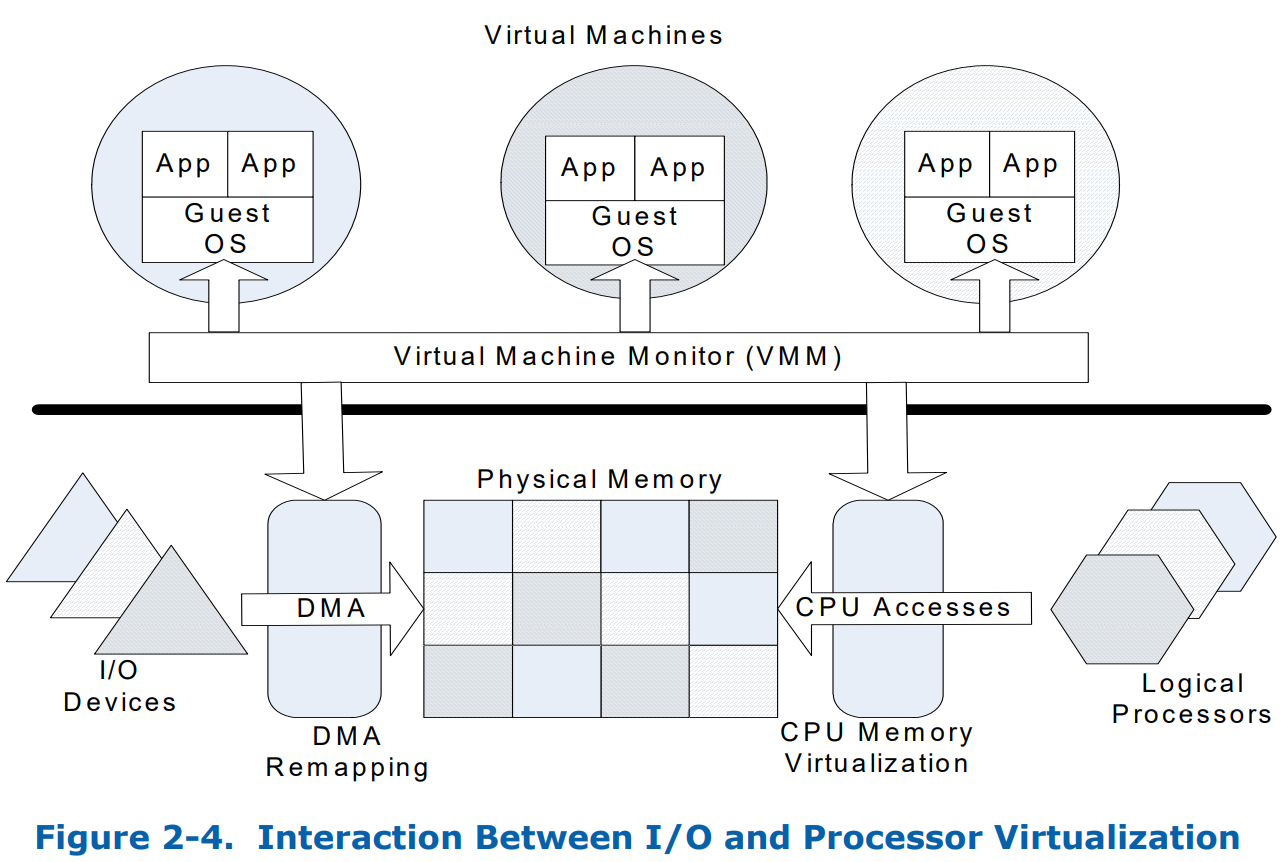

2.2 VMM和虚拟机

VMM - qemu

guest software - 虚拟机里运行的软件(guest os + app)

2.3. 处理器虚拟化 - VMX

2.4 IO虚拟化

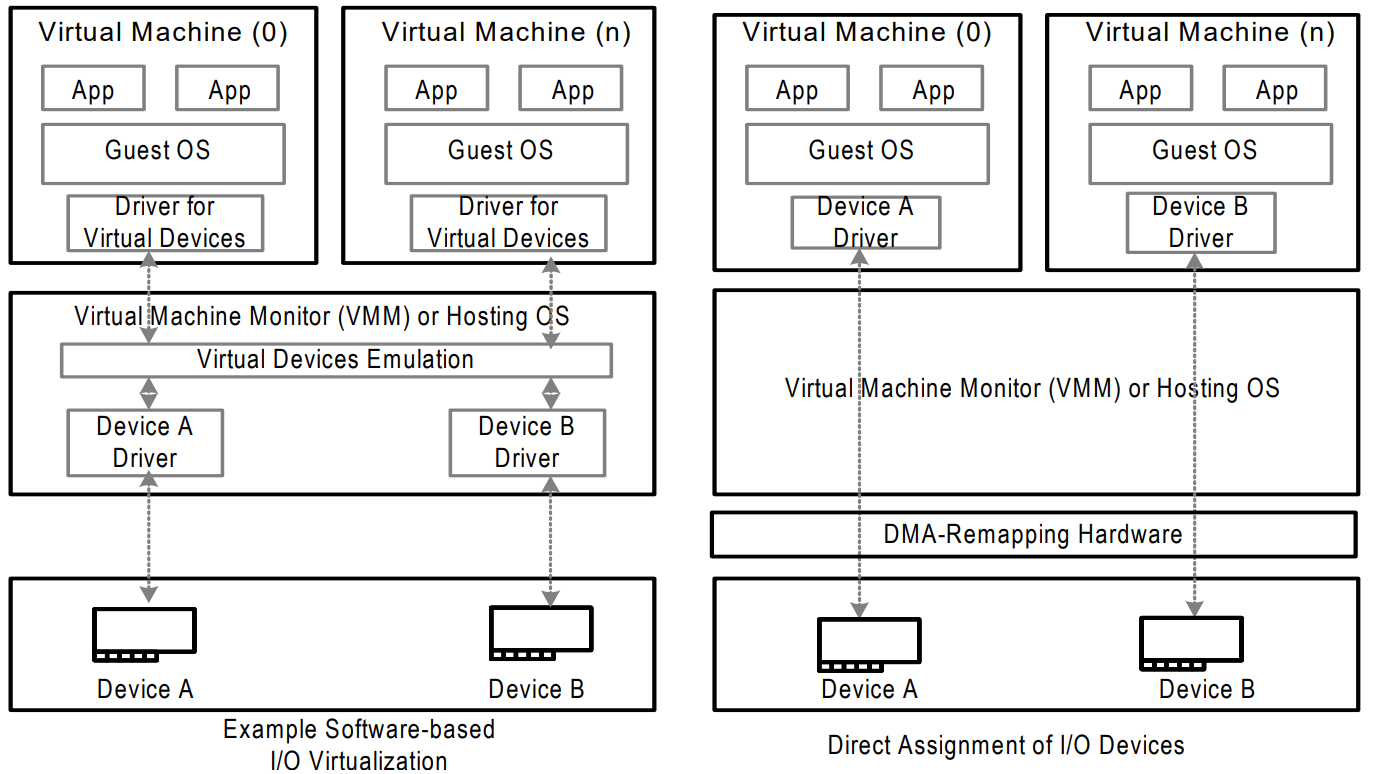

Emulation - 纯粹软件模拟, 比如e1000模拟的网卡

New Software Interfaces - 比如 SRIOV

Assignment - 直接物理IO 设备分给VM

I/O Device Sharing - IO设备共享,SRIOV/SIOV

2.5 Intel® Virtualization Technology For Directed I/O

IO虚拟化的要求,隔离和限制资源访问

I/O device assignment -

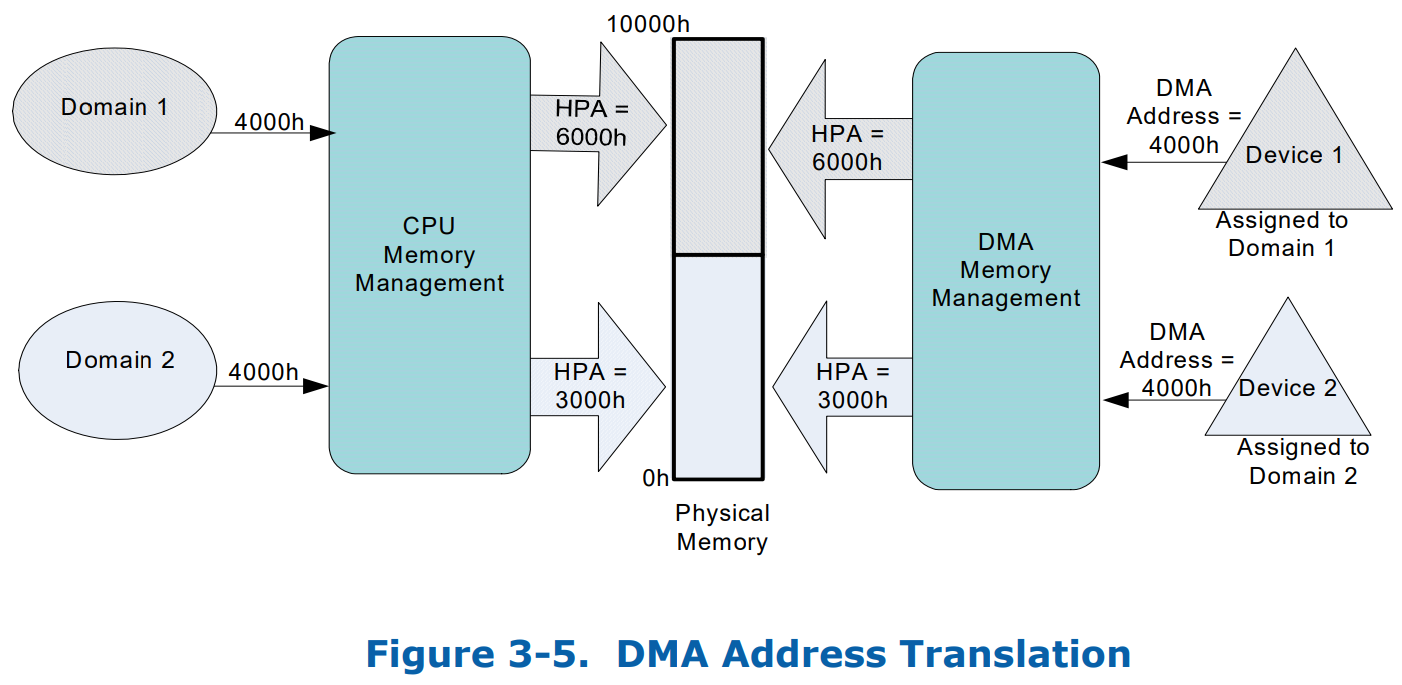

DMA remapping - DMA地址转换

Interrupt remapping: - 隔离并路由正确的中断到|VM

Interrupt posting - 直接投递中断

Reliability - 记录和报告 DMA/中断的错误

2.5.1 Hardware Support for DMA Remapping

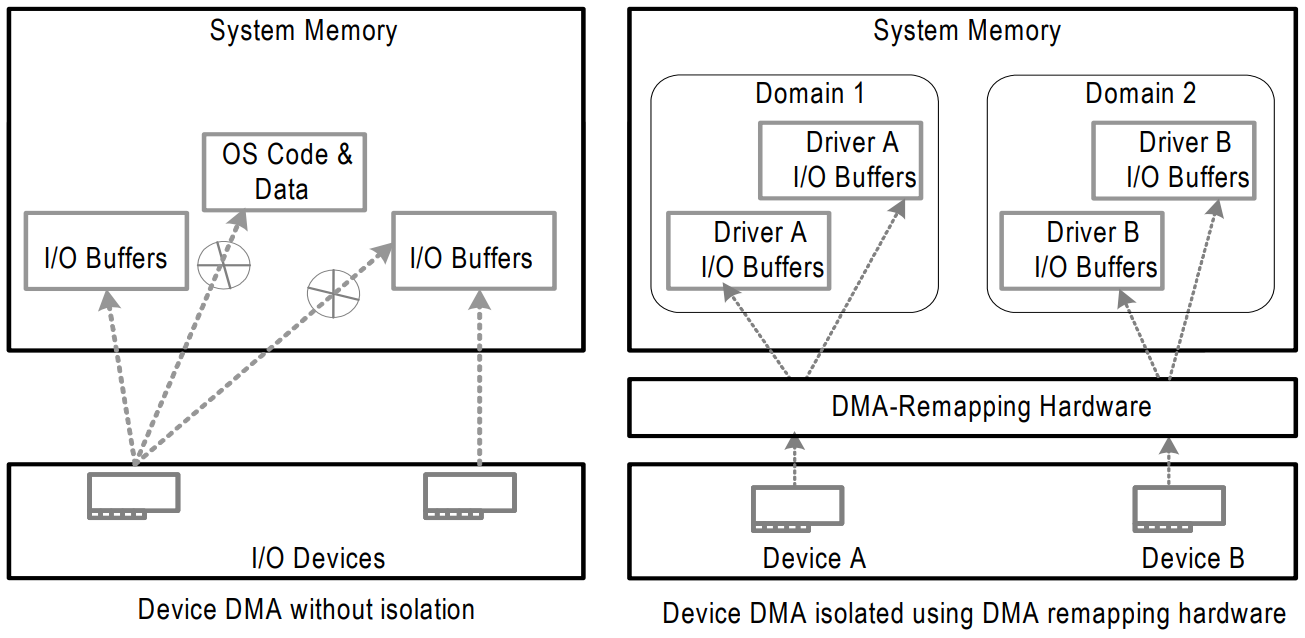

DMA-remapping 硬件截获系统内存访问,利用页表,决定访问是不是不允许,以及访问的实际位置。

常用的分页结构可以缓存在硬件中。 DMA重新映射可以为每个设备独立配置,也可以跨多个设备共同配置。

2.5.1.1 OS Usages of DMA Remapping

操作系统保护:操作系统可以定义一个包含其关键代码和数据结构的domain,并限制系统中所有I / O设备对该domain的访问。 这允许操作系统通过设备驱动程序对设备进行不正确的编程来限制其数据和代码的错误或意外损坏,从而提高了操作系统的健壮性和可靠性。

功能支持:操作系统可以使用domain来更好地管理从旧版设备到高内存的DMA(例如,访问4GB以上内存的32位PCI设备)。 这是通过对I / O页表进行编程以将DMA从这些设备重新映射到高内存来实现的。 没有这样的支持,软件就必须通过OS的“反弹缓冲区(bounce buffers)”来复制数据。

DMA隔离:OS可以通过创建多个domain并将一个或多个I / O设备分配给每个域来管理I / O。每个设备驱动程序都会在操作系统中显式注册其I / O缓冲区,然后操作系统会使用硬件实施DMA域保护,从而将这些I / O缓冲区分配给特定的domain。请参见图2-2。

共享虚拟内存:对于支持适当PCI Express1功能(PCI Express *基本规范中的进程地址空间ID - PASID功能)的设备,操作系统可以使用DMA重映射硬件功能与I / O设备共享应用程序进程的虚拟地址空间。共享的虚拟内存以及对I / O页面故障的支持,使应用程序可以将任意数据结构自由地传递到图形处理器或加速器等设备,而无需进行数据固定和编组的开销。

图2-2

2.5.1.2 VMM Usages of DMA Remapping

DMA重新映射的硬件支持可实现设备直接分配,而无需或者最小VMM接入(配置空间和中断管理), VMM不需要感知设备的特殊知识。

IO设备分配,可以IO共享。一个IO分区的设备,可以给其他分区提供分享。

2.5.1.3 DMA Remapping Usages by Guests

VMM可以将重新映射的硬件虚拟化给guest。

VMM可以拦截来宾对虚拟重映射硬件寄存器的访问,并管理guest的重映射结构的影子拷贝。来宾更新I / O页表时,来宾软件执行适当的虚拟无效操作。虚拟无效请求可以被VMM拦截,以更新相应的影子页表并执行重新映射硬件操作。

由于故障DMA事务的不可重启性(与CPU内存管理虚拟化不同),VMM无法对其影子重映射结构执行延迟更新。

为了使影子结构与来宾结构保持一致,VMM可能会以急切的预取行为(包括缓存不存在的条目)暴露虚拟重映射硬件,或使用处理器内存管理机制对guest重映射结构进行写保护。

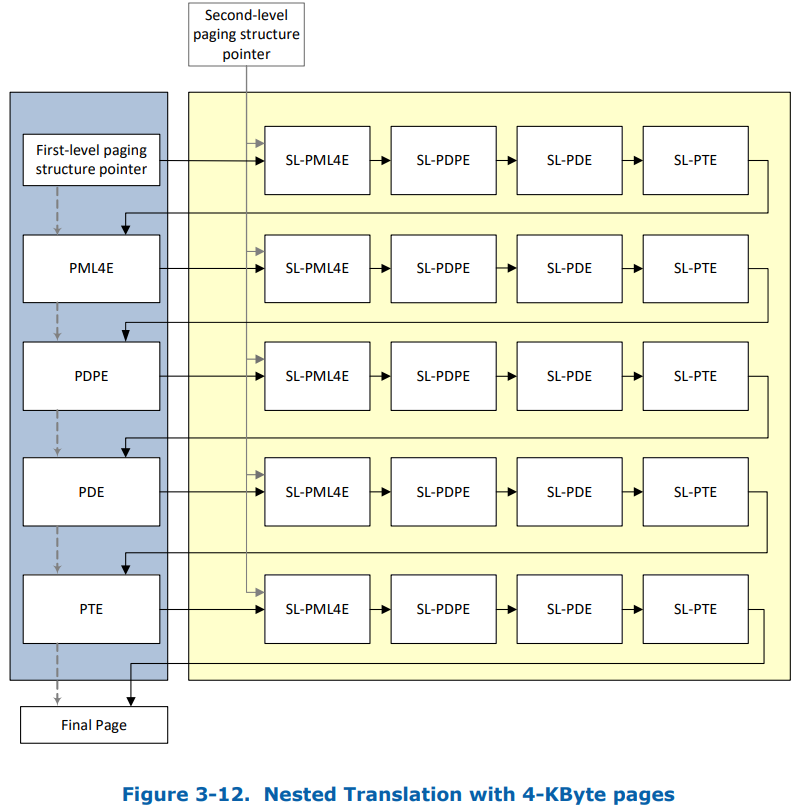

在支持两级地址转换(将虚拟地址重新映射到guest物理地址的第一级转换,以及将guest物理地址重新映射到host物理地址的第二级转换)的硬件实现上,VMM可以通过配置硬件以执行第一级和第二级的嵌套地址转换,而不需要影子页表来虚拟化guest操作系统对第一级转换。

2.5.2 Hardware Support for Interrupt Remapping

通过是能中断的重映射,实现分区隔离。

2.5.2.1 Interrupt Isolation

RC(Root-Complex) 通过在地址范围(0xFEEx_xxxxh)的写事务来标识中断请求。

中断是自描述的(中断请求的属性,编码在请求的地址和数据中), 允许任何DMA启动器来生成具有任何属性的中断消息。

VMM利用中断重映射实现domain中间的外部中断隔离。 利用中断重映射硬件,来区分来自特定设备的中断,并将其路由到分配了该设备的VM上。

VMM还可以利用中断重映射硬件来控制这些中断请求的属性,例如目标CPU,中断向量,传送模式等。

VMM还可以使用中断重映射硬件来区分外部中断与VMM拥有的处理器间中断(IPI)。软件可以 通过 任何外部重映射中断的属性(例如向量号)都不匹配VMM IPI的属性 来确认。

2.5.2.2 Interrupt Migration

中断重映射体系结构通过中断的动态重定向, 来实现中断请求目的从一个逻辑处理器迁移到另一个上。

如果没有中断重映射硬件支持,需要软件对中断源进行重新编程。 但是,这些资源的重新编程是非原子性的(要求要重新编程多个寄存器),通常很复杂(可能需要临时屏蔽中断源),并且取决于中断源的特性(例如,某些中断源没有屏蔽能力;在某些源上被屏蔽时,升降沿中断可能会丢失)。

中断重新映射使软件能够有效地重定向中断,而无需在中断源上重新编程配置。

OS软件可以使用中断迁移来平衡处理器之间的负载(例如,在运行I / O密集型工作负载时)。

通过中断迁移, VMM可以实现将带有设备分区的虚拟CPU在物理CPU之间进行迁移,以提高CPU利用率。

2.5.2.3 x2APIC Support

英特尔®64 x2APIC架构将APIC寻址能力扩展到32位(从8位)。 有关详细信息,请参阅《英特尔®64体系结构软件开发人员手册,第3B卷:系统编程指南》(Intel® 64 Architecture Software Developer's Manual, Volume 3B: System Programming Guide)。

中断重新映射使x2APIC支持外部中断的扩展APIC可寻址性,而无需对中断源(例如I / OxAPIC和MSI / MSIX设备)进行硬件更改。

2.5.3 Hardware Support for Interrupt Posting

通过硬件支持,优化处理直接分配给虚拟机的I / O设备(PF,SR-IOV的VF或英特尔® SIOV的可分配设备接口ADI,Assignable Device Interfaces )的中断请求。

2.5.3.1 Interrupt Vector Scalability

来自分配给虚拟机的PF,VF 或 ADI 设备/资源的中断请求被称为虚拟中断,因为它们针对已分配VM的虚拟处理器。

每个VF或ADI都需要其自己的独立中断资源,这比没有I / O虚拟化的情况,需要更多的中断向量。

没有中断投递硬件支持,平台中的所有中断源都映射到相同的物理中断向量空间(Intel®64处理器上,每个逻辑CPU 8位向量空间)。

对于虚拟化用途,当虚拟进程与逻辑处理器之间没有静态亲和时,在动态环境中跨虚拟处理器划分物理向量空间是一项挑战。

对支持中断投递的硬件,通过允许来自分配给虚拟机的设备中断请求在虚拟矢量空间中处理,从而自然地可随虚拟机或虚拟处理器的数量进行中断向量伸缩。

2.5.3.2 Interrupt Virtualization Efficiency

如果没有硬件中断post,需要通过VMM软件处理分配给VM的设备中断。

当CPU接收到发往VM的外部中断时,控制权就会转移到VMM,要求VMM处理并将相应的虚拟中断注入虚拟机。VMM处理外部中断相关的控制转移会导致硬件和软件开销。

有硬件中断post,设备(PF,VF或ADI)中断被投递(记录)到VMM指定的内存描述符中,并根据中断目标vCPU的运行状态进行处理。

如果目标虚拟处理器可在任何逻辑处理器上运行,硬件可直接向虚拟处理器传递外部中断,而无需任何VMM干预。

当目标vCPU被抢占(等待其运行)时收到的中断可以由硬件累积在内存中,以便在以后调度vCPU时进行传递。这避免了在非运行VM的外部中断到来打乱当前正在运行的vCPU的执行。

如果目标vCPU在中断到达时暂停(空闲),或者如果中断符合要求实时处理的条件,则硬件可以将控制权转移给VMM,从而使VMM可以调度vCPU, 让硬件直接传递pending的中断到该vCPU。

基于目标vCPU状态的中断处理降低了对虚拟机的中断总时延,并减少了VMM为虚拟化中断而产生的开销。

2.5.3.3 Virtual Interrupt Migration

为了优化整体平台利用率,VMM软件可能需要动态评估最佳逻辑处理器以调度vCPU,导致跨CPU迁移vCPU。

对于带有设备的虚拟机,跨逻辑处理器迁移vCPU会导致软件中转中断带来开销(例如,通过VMM生成的IPI),或者会导致vCPU的每个中断独立迁移到新逻辑CPU的复杂性。

中断post的硬件支持,使VMM软件能够在vCPU被调度到另一个逻辑处理器时,以原子方式对所有针对该vCPU的中断进行迁移。

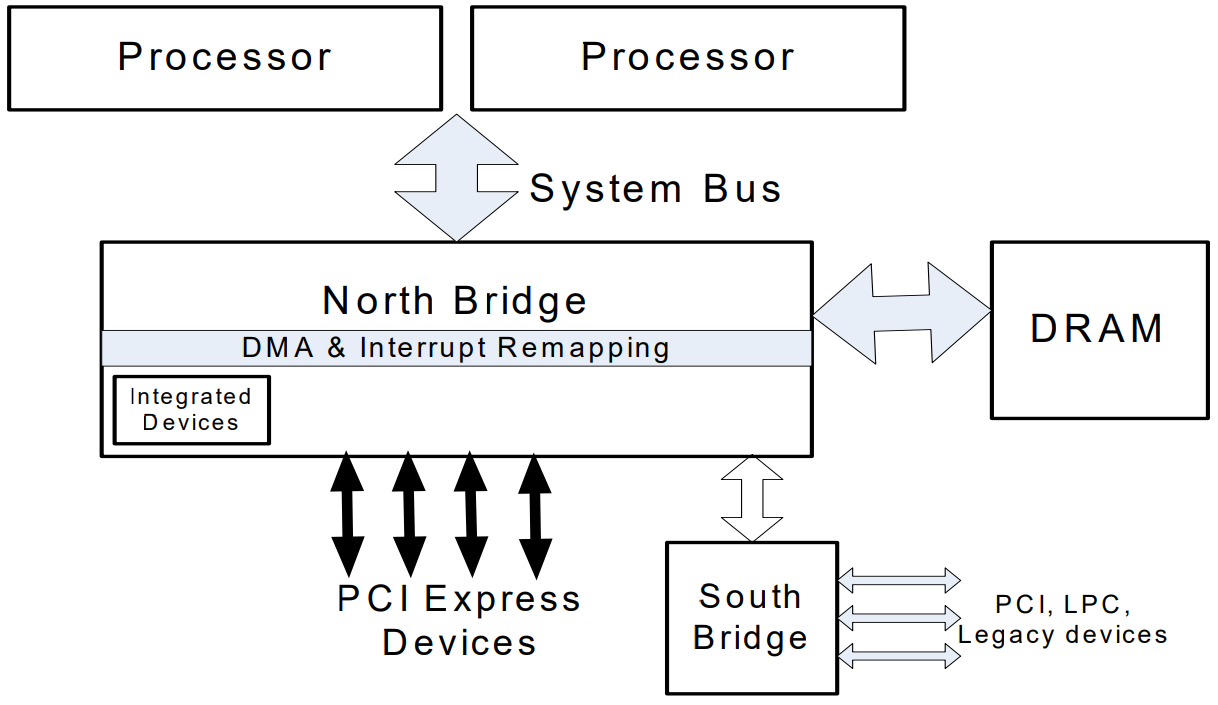

3 DMA Remapping

介绍用于DMA重新映射的硬件体系结构。该硬件将在集成到处理器组合(Complex)中的Root-Complex(RC)或核心逻辑芯片组组件中实现。

3.1 Types of DMA requests

DMA 可以是来自RC集成的device后者是PCI离散的设备。

共分两类:

- 不带有地址空间描述符的请求: 指定访问类型(读/写/原子),目标DMA地址/大小以及发起请求的设备的源ID(BDF)。

- 带有地址空间描述符的请求: 出来带有PASID,还有可选属性,例如Execute-Requested(ER)标志(以指示读取为指令提取)和Privileged-Mode-Requested(PR)标志(以区分用户访问权限和超级访问权限)。

3.2 Domains and Address Translation

DMA重映射将I / O设备发出的DMA请求中的地址转换为其相应的主机物理地址(HPA)

3.3 Remapping Hardware - Software View

支持 PCI segment 组重映射(每个组一个重映射硬件),或者组中互斥设备子集的重映射。

可以是根总线上实现硬件重映射,也可以是PCIE root port上实现。

3.4 Mapping Devices to Domains

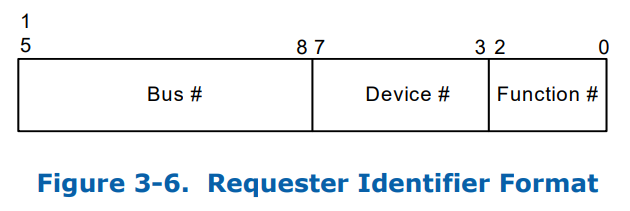

3.4.1 Source Identifier

对于RC设备,source-id基于RC内部实现派生。

对于PCIE设备,source-id就是BDF。从PCIE的传输层header中获取。

3.4.2 Legacy Mode Address Translation

Root Table Address Register (RTADDR_REG)描述见 Section 10.4.6,

(RTADDR_REG.TTM is 00b), Root Table 是4-KByte大小,包含256个root-entries, 每个root-entry 指向一个context-table,包含256个context-entries.

Root-entry 格式描述见Section 9.1, context-entry 格式描述见Section 9.3.

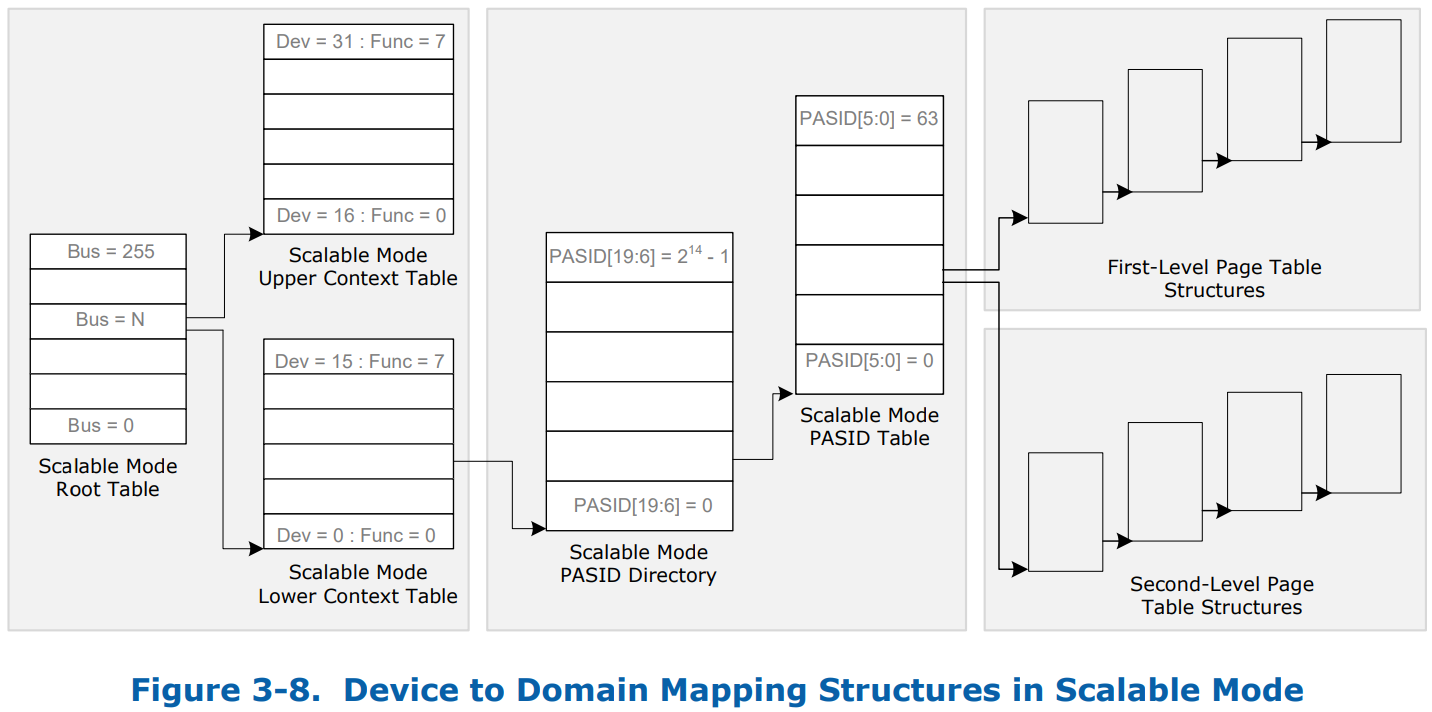

3.4.3 Scalable Mode Address Translation

RTADDR_REG.TTM is 01b,

context-table 是4-KByte 大小,包含 128 scalable-mode context entries.

context-entries 支持requests-without-PASID 和 requests-with-PASID.

root-entry 格式描述见Section 9.2,context-entry 格式描述见 Section 9.4, PASID-directory-entry 格式描述见Section 9.5, PASID-table entry 格式描述见 Section 9.6.

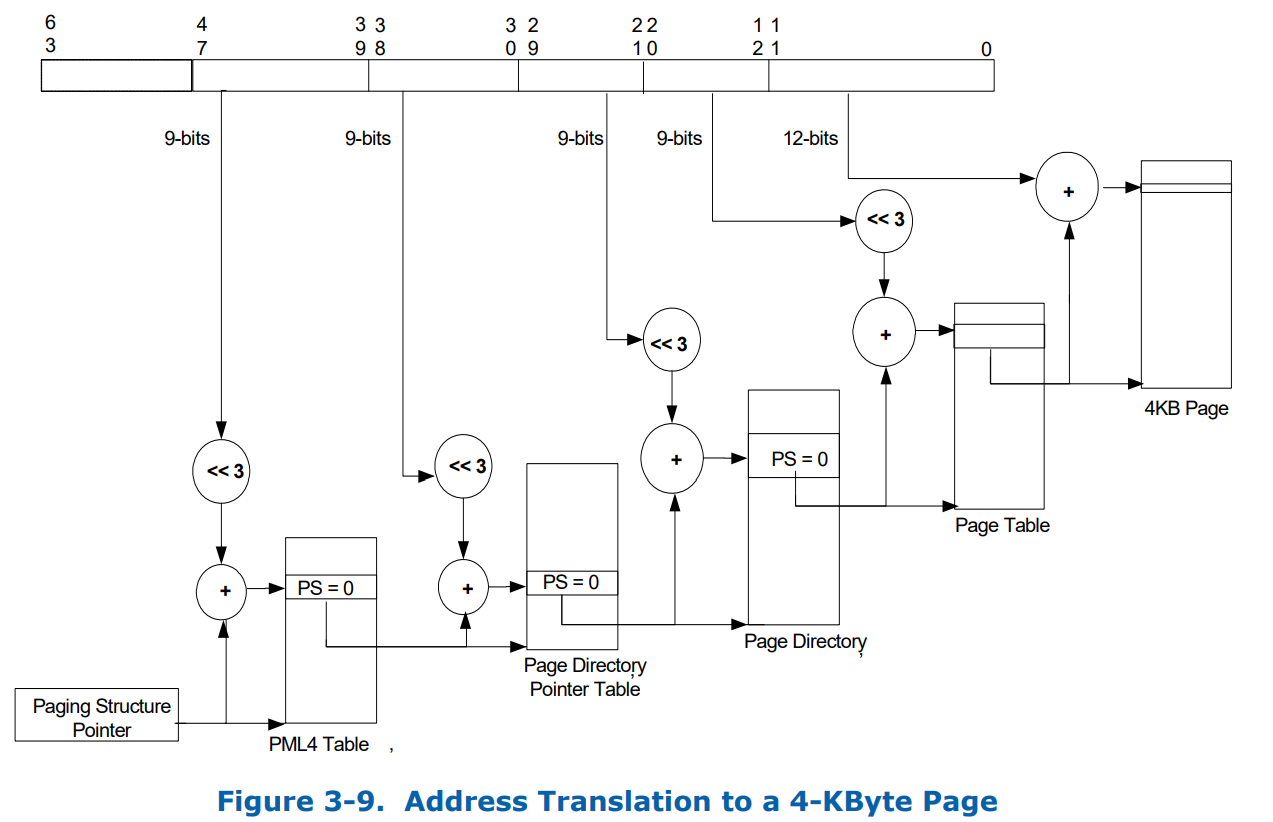

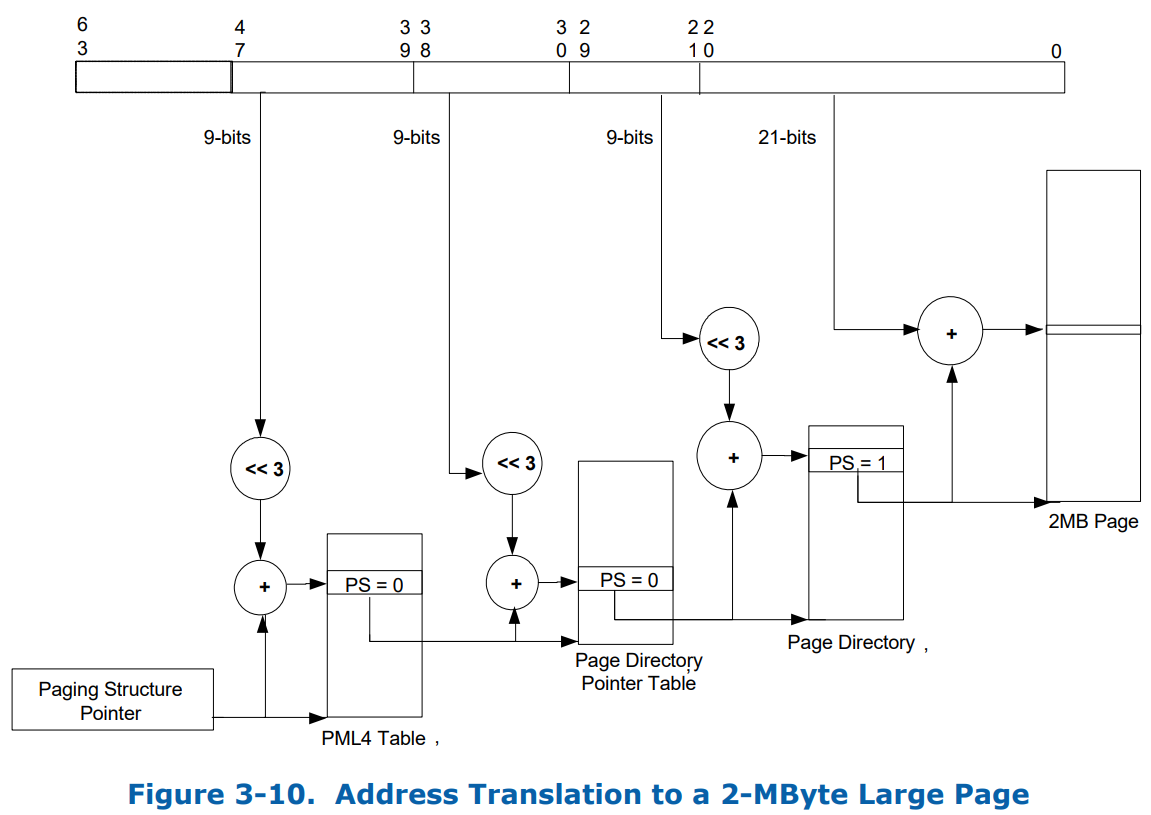

3.5 Hierarchical Translation Structures

支持1级,2级和嵌套转换。

层次结构中的每个分页结构的大小均为4 KB,带有512个8字节条目,,支持4级和5级页表。

3.6 First-Level Translation

一级转换将输入地址限制为经典地址(即地址位63:N与地址位[N-1]具有相同的值,其中N是4级分页的48位,而N是 5级分页的57位)。重映射硬件对第一层转换的请求将进行经典的地址检查,作为进行第一层转换的前提条件,将违反视为转化错误。

3.6.1 Access Rights

3.6.2 Accessed, Extended Accessed, and Dirty Flags

这两节在写代码时候关心吧。

3.7 Second-Level Translation

两级转换,就是整个一级转换完,再去索引二级转换。嵌套转换,第一级的页表除了PML4E,其他的都有第二级转换索引到。

可以将Context entries和可伸缩模式PASID-Table entries配置为支持第二级转换。对于Context entries,第二级转换仅适用于没有PASID的请求。

使用可伸缩模式的PASID-Table entries,可以将第二级转换应用于所有请求(带有或不带有PASID),适用于嵌套转换。

每个Context entries都包含一个指向第二级转换结构基础的指针。第9.3节描述了Context entries的确切格式。可伸缩模式Context entries引用可伸缩模式PASID结构。

每个可伸缩模式的PASID-Table entries都包含一个指向第二级转换结构基础的指针。

二级转换将输入地址限制为通过功能寄存器中的最大guest地址宽度(MGAW)字段 报告实现的地址宽度。输入地址需要进行MGAW地址检查,任何违规都将被视为翻译错误。

第7章详细介绍了故障情况及其对软件的报告。

3.8 Nested Translation

5 Interrupt Remapping

中断重映射体系结构包括中断重映射和中断post。

5.1 Interrupt Remapping

中断重新映射架构使系统软件能够控制和审查由所有中断源生成的外部中断请求,包括来自中断控制器(I / OxAPIC)的请求,支持MSI / MSI-X的设备(包括端点,根端口和Root-Complex集成终端)的请求。

由重映射硬件本身生成的中断(故障事件和失效完成事件)不受中断重映射的约束。

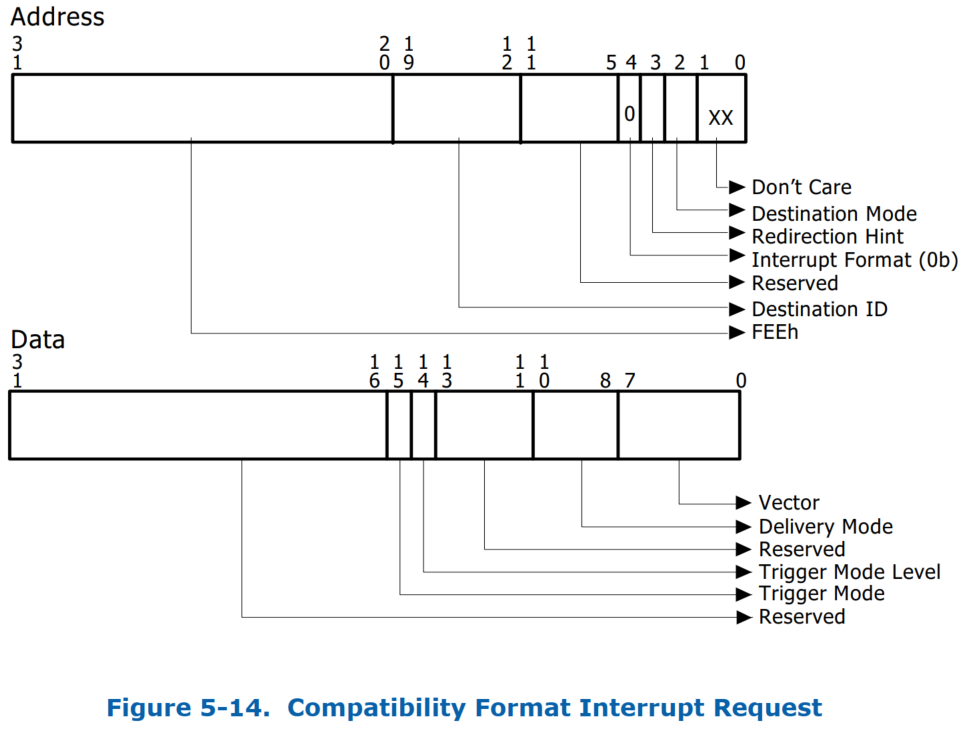

中断请求在Root-Complex这里,显示为对上游内存的中断地址范围0xFEEX_XXXXh写入请求。

由于中断请求作为写请求到达RC,因此中断重映射与重映射硬件单元(这里指DMA?)位于同一位置。 通过扩展功能寄存器可知道是否支持中断重映射功能。

5.1.1 Identifying Origination of Interrupt Requests

就是第三节说的source-id

包括,来自各种RC/PCIE/PCI桥的MSI, 遗留的PIN中断,以及其他的MSI(不如高精度时钟,由ACPI描述)

5.1.2 Interrupt Request Formats On Intel® 64 Platforms

5.1.2.1 Interrupt Requests in Compatibility Format

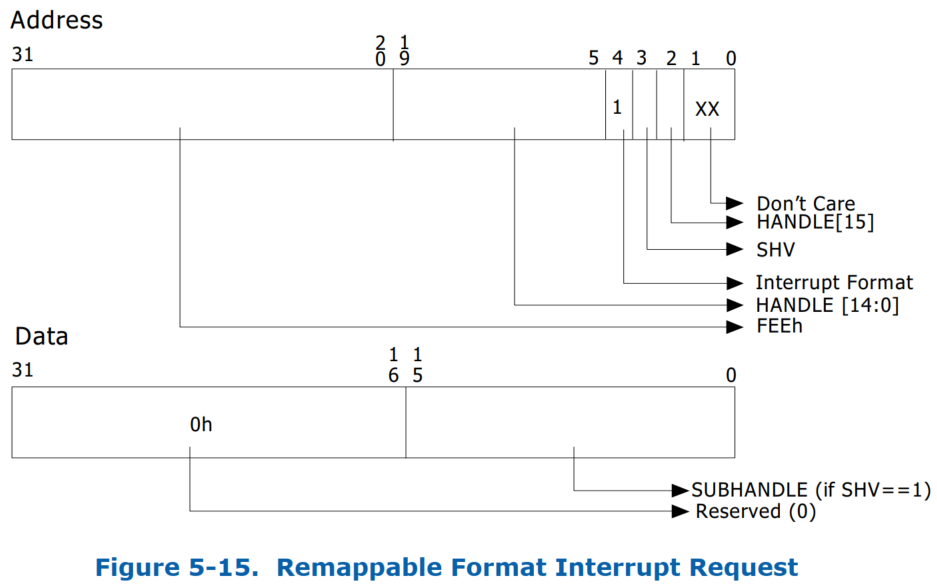

5.1.2.2 Interrupt Requests in Remappable Format

5.1.3 Interrupt Remapping Table

中断重映射硬件使用了 驻留在内存中的单级表(DMA都是多级页表),称为中断重映射表。

中断重映射表将由系统软件创建,其基地址和大小通过中断重映射表地址寄存器指定。

该表中的每个条目的大小均为128位,称为中断重映射表条目IRTE(Interrupt Remapping Table Entry)。第9.10节说明了IRTE格式。

对于中断请求的可重映射格式,中断重映射硬件将如下计算“ interrupt_index”。 Handle, SHV 和 Subhandle分别对应可重映射中断格式中的地址或数据中的字段。

if (address.SHV == 0) { interrupt_index = address.handle; } else { interrupt_index = (address.handle + data.subhandle); }

中断重映射表地址寄存器由软件编程,并指定中断重映射表中的IRTE数量(中断重映射表中的IRTE的最大数量为64K)。

平台中的重映射硬件单元可以配置为共享中断重映射表或使用独立的表。

interrupt_index用于在中断新映射表中索引适当的IRTE表项。

如果计算出的interrupt_index值等于或大于重映射表中IRTE的数量,则硬件视该中断请求为错误。

兼容中断格式, 所有中断属性都编码在中断请求的地址/数据中,而可重映射中断格式仅指定了计算interrupt_index所需的字段。

重映射中断请求的属性在IRTE表项中指定,可以通过interrupt_index索引表项.

中断重映射体系结构定义了对硬件对常用的IRTE缓存的支持,以提高性能。对于软件可能需要动态更新IRTE的场景,体系结构定义了使IEC无效的命令。

第6章介绍了缓存结构和相关的无效命令。

5.1.4 Interrupt-Remapping Hardware Operation

硬件操作概览:

- 硬件将中断请求标识为DWORD大小的请求,写入范围为0xFEEx_xxxx的中断地址。

- 当未启用中断重映射时(全局状态寄存器中的IRES字段为Clear),将按照第5.1.2.1节中描述的兼容性中断请求格式处理中断请求。

- 若启用中断重映射(全局状态寄存器中的IRES字段为set),中断请求将按以下方式处理:

- 兼容格式的中断请求(即“中断格式”字段为“Clear”的请求)按以下方式处理:

-

如果启用了扩展中断模式(中断重映射表地址寄存器的EIME字段为set),或者禁用了兼容格式的中断(全局状态寄存器中的CFIS字段为Clear),则兼容格式的中断被阻止。

-

否则,兼容格式中断将作为直通处理(绕过中断重映射)

-

-

可重映射格式的中断请求(“中断格式”字段为set请求)的处理方式如下:

-

检查可重映射中断请求中的保留字段是否为零。如果保留字段检查失败,则中断请求将被阻止。否则,从中断请求中检索Source-id,Handle,SHV和Subhandle字段。

- 硬件根据第5.1.3节中所述的算法计算interrupt_index。验证计算出的interrupt_index小于“中断重映射表地址寄存器”中配置的中断重映射表大小。如果边界检查失败,则中断请求被阻止。

-

如果边界检查成功,则从中断条目缓存中检索与interrupt_index值相对应的IRTE,或从中断重新映射表中获取该中断。

- 如果相关字段(C)在扩展功能寄存器中设置为“清除”,则从内存中提取IRTE,而不会监听处理器缓存。硬件必须以单个操作读取整个IRTE,不能使用多次读取来获取IRTE的内容,因为软件可能会自动更改IRTE的内容。

- 如果IRTE存在(P = 1),则硬件会按照第9.10节中所述,通过对IRTE中的SVT,SID和SQ字段进行编程来验证中断请求者。如果源ID检查失败,则中断请求将被阻止。

-

- 如果IRTE 的Mode 字段为 clear (IM=0):

-

硬件以可重映射格式解释IRTE(如第9.10节所述)。如果检测到对可重映射格式IRTE的编程无效,则中断请求将被阻止。

-

如果以上检查成功,则根据IRTE字段,编程生成重新映射的中断请求。(remap完成)

-

- 兼容格式的中断请求(即“中断格式”字段为“Clear”的请求)按以下方式处理:

5.1.4.1 Interrupt Remapping Fault Conditions

编程的时候需要看这一节。

5.1.5 Programming Interrupt Sources To Generate Remappable Interrupts

软件执行以下常规步骤,配置中断源生成可重映射的中断:

- 分配一个空闲的中断重映射表条目(IRTE),并按照9.10节中所述的IRTE格式对重映射的中断属性进行编程。

- 对中断源进行编程,以生成可重映射格式的中断。包括设置适当的句柄,子句柄和SHV字段,这些字段可将分配IRTE的索引有效编码为interrupt_index(5.1.3节中定义的)。可用以下任何一种方式,使用handle,subhandle和SHV字段对interrupt_index进行编码:

— SHV = 0; handle = interrupt_index;

— SHV = 1; handle = interrupt_index; subhandle = 0;

— SHV = 1; handle = 0; subhandle = interrupt_index;

— SHV = 1; handle = interrupt_index - subhandle;

5.1.5.1 I/OxAPIC Programming

编程的时候需要看这一节。

5.1.5.2 MSI and MSI-X Register Programming

编程的时候需要看这一节。

5.1.6 Remapping Hardware - Interrupt Programming

由重映射硬件本身生成的中断(故障事件和无效完成事件)不受中断重映射的约束。

以下各节介绍了Intel 64平台上的故障事件和无效完成事件的数据/地址寄存器的编程。

5.1.7 Programming in Intel® 64 xAPIC Mode

5.1.8 Programming in Intel® 64 x2APIC Mode1

5.1.9 Handling of Platform Events

5.2 Interrupt Posting

中断发布(投递?)功能是中断重映射硬件的扩展,用于扩展处理可重映射格式的中断请求。中断发布使可重映射格式的中断请求被发布(记录)在一致主存中的数据结构中,同时向CPU complex通知事件(可选),通过信号通知挂起的中断投递。

中断发布功能(以及Intel 64处理器对发布后中断处理和APIC虚拟化的支持)使虚拟机监视器(VMM)软件可以有效地处理分配给虚拟机的设备中断。

2.5.3节描述了中断发布的高级用法和好处。

请参阅“英特尔®64体系结构软件开发人员手册,第3B卷:系统编程”《Intel® 64 Architecture Software Developer's Manual, Volume 3B: System Programming》,以获取有关APIC支持虚拟化和中断后处理的英特尔64处理器的详细信息。

通过功能寄存器(CAP_REG)中的“发布的中断支持(PI)”字段查看对重映射硬件对中断发布功能的支持。

10.4.2节介绍了中断发布功能

5.2.1 Interrupt Remapping Table Support for Interrupt Posting

Interrupt Remapping Table Entry (IRTE)中的Mode (IM) 字段,描述IRTE 为interrupt-remapping 或者interrupt-posting.

- IM=0,IRTE 为 remappable格式

- IM=0,IRTE 为 posted 格式

POST格式的IRTE条目支持以下新字段:

•“POST中断描述符”数据结构的地址, 用来post中断。第5.2.2节描述了POST的中断描述符。

•紧急(URG)资格,指示通过此IRTE处理的中断请求是否需要实时处理。 5.2.3节描述了该字段的硬件操作。

•向量字段,指定POST中断 通过IRTE处理时 使用的向量。与可重映射格式不同(在生成重映射的中断请求时使用Vector字段),POST格式的IRTE Vector字段用于确定当中断发布到IRTE引用的中断描述符时, 要设置的bit位。

5.2.2 Posted Interrupt Descriptor

POST中断描述符是内存中一个64字节对齐的结构,中断投递硬件用来投递(记录)要发布的中断请求。第9.12节介绍了POST的中断描述符格式。系统软件必须在一致的(写回)主存储器中分配POST中断描述符。

POST中断描述符包含以下字段:

•发布中断请求(PIR)字段: 用于存储POST(记录)中断(每个向量1 bit,最多256个向量)。

•未清通知(ON)字段: 指示此已发布中断描述符是否存在未处理的通知事件(没有被处理器或软件处理)。当此字段为0时,硬件将在生成通知事件时将其从0修改为1,接收通知事件的实体(处理器或软件)会将其重置为POST中断处理的一部分。

•“禁止通知”(SN)字段: 指示是否要针对非紧急中断请求(通过URG = 0的IRTE处理的中断)抑制(不生成)通知事件。

•通知向量(NV)字段: 指定通知事件(中断)的向量。

•通知目标(NDST)字段: 指定通知事件的目标逻辑处理器的物理APIC-ID。

5.2.3 Interrupt-Posting Hardware Operation

可重映射格式的中断请求由硬件处理,如第5.1.4节所述。

当此类处理遇到POST格式(IM = 1)的IRTE条目时,将通过POST处理中断请求(而不是重新映射)。 以下内容提供了中断POST硬件操作的功能概述:

•如果取到的IRTE设置了“模式”字段(IM = 1)

—硬件以POST格式解释IRTE(如第9.11节所述)。如果检测到POST格式IRTE的编程无效,则中断请求将被阻止。

—如果以上检查成功,则IRTE将提供指向已POST中断描述符(PDA-L / PDA-H)的指针,投递中断向量值(Vector),以及是否将中断请求视为紧急(URG)

•硬件对POST中断描述符执行 一致的原子 读取-修改-写入 操作,如下所示:

—reporting 内存类型支持(ECAP_REG中的MTS = 1)的硬件实现, 必须使用回写(WB)内存类型 并原子操作来更新POST中断描述符。

—无论扩展功能寄存器(ECAP_REG)中的Pagewalk Coherency (C) 字段的值如何,此原子性的读取,修改,写入操作将始终监听处理器缓存。

—读取POST中断描述符的内容,声称其托管cache-line的专有权。如果检测到POST中断描述符的无效编程(例如,非零保留字段),则释放高速缓存行的所有权,并阻止中断请求。

—如果以上检查成功,则在中断描述符中,获取“POST中断请求”(PIR位255:0),“未清通知”(ON),“禁止通知”(SN),“通知向量”(NV)和“通知目标”(NDST)等字段的当前值。

—原子地修改以下描述符字段值:

•将PIR中的位设置为与IRTE中的矢量字段值相对应

•计算X =(((ON == 0)&(URG |(SN == 0)))

•如果(X == 1),则设置ON字段。

—提升缓存行在全局范围内可观察,以便其他缓存代理可以看到修改。在此步骤之后,硬件可以随时写回高速缓存行。

—如果上一步(X == 1),则生成具有以下属性的通知事件(中断):

•NSDT字段:指定目标逻辑CPU的物理APIC-ID。关于xAPIC和x2APIC模式如何解释该字段,请参见第9.12节。

•NV字段: 指定用于通知中断的向量,以向目标CPU发出有关挂起的POST中断的信号。

•通知中断的传递模式字段: 被强制为固定(000b)

•通知中断的重定向提示字段: 被强制清除(0b)

•通知中断的“触发模式”字段: 被强制为边沿(0b)

•通知中断的“触发模式级别”字段: 被强制设置为“有效”(1b)。

•以上任何导致中断请求被阻止的检查均被视为中断重映射故障条件,如第5.1.4.1节中所述。

5.2.4 Ordering Requirements for Interrupt Posting

本节总结了POST中断的硬件要满足的顺序要求。

•中断请求是POST事务,并遵循PCI Express POST的订购规则。这样可以确保在所有先前的入站POST请求(写操作)提交到其目的地之前,软件不会观察到之后的中断请求。

— 即使已投递了该中断请求,也需要保持此要求。也就是说,在将中断投递(记录)到POST中断描述符中并使其对软件可见之前,必须先完成所有先前发布的请求。

•由于中断请求是POST事务,因此 上游读取完成时 必须推送先前的中断请求。upstream read completions must push preceding interrupt requests.

— 即使一个或多个先前的中断请求被投递了,也需要保持此要求。即,上游读取完成必须等待,直到所有先前的中断(无论它们是重新映射还是POST)都已完成。如果POST了一个中断,则“完成”意味着该POST中断描述符的原子更新和相关的通知事件均已完成。

•在中断POST操作中,硬件必须确保在POST该中断描述符的通知事件之前,软件可以观察到对该中断描述符的修改。

5.2.5 Using Interrupt Posting for Virtual Interrupt Delivery

本章主要介绍,VMM怎么使用post中断硬件,有效的将来自设备的虚拟中断传递给VM。

VMM软件为虚拟机启用中断发布流程如下:

•对于虚拟机中的每个vCPU,VMM软件分配POST中断描述符。用于分发将要 传递到给vCPU的所有中断。

— 软件必须阻止设备访问POST中断描述符所在的内存。实现此目的一种方法是设置重映射表,以便重映射硬件阻止从设备到POST中断描述符的访问。

— 如果设备能够写入POST中断描述符,则不能保证POST中断操作的原子性。

•VMM软件为通知事件分配了两个物理中断向量(平台中跨所有逻辑CPU)。

— “活动通知向量”(ANV),用于向投递中断时处于活动状态(正在执行)的任何vCPU投递中断通知。

—“唤醒通知向量”(WNV),用于向POST中断时被阻止(停止)的vCPU的中断通知发布。

•对于设备到VM的每个中断源,VMM软件都可以拦截和虚拟化中断资源(IOxAPIC条目和/或MSI / MSI-X寄存器)的客户软件编程。通过这种虚拟化,VMM软件可以检测目标vGPU和来宾软件分配的虚拟矢量。

•对于每个此类中断源,VMM软件都会分配一个POST格式的IRTE。

— 每个此类IRTE中的向量字段均由VMM软件编程,并由来宾软件为中断源分配了相应的虚拟向量值。

— 每个此类IRTE中的POST描述符地址字段均由VMM软件编程,以引用guest软件针对vCPU中断源分配的POST描述符,。

— 如果将相应的中断源指定为需要立即(非延迟)处理,则VMM软件会设置IRTE中的紧急(URG)字段。

•VMM软件配置处理器硬件,为vCPU启用APIC虚拟化(包括“虚拟中断delivery”和“进程投递中断”功能)。

— 虚拟处理器的“POST中断通知向量”已配置有本节前面介绍的“活动通知向量”(ANV)值。

— 虚拟处理器的“POST中断描述符”配置有分配给各个vCPU的POST中断描述符的地址。

•VMM调度程序可以按以下方式管理虚拟处理器的调度状态:

— 当选择要执行的虚拟处理器时,在进入/恢复虚拟处理器之前,该虚拟处理器的状态被指定为“活动”。通过使用ANV向量的value对其通知向量(NV)字段进行编程,可以在其POST中断描述符中指定此状态。这样,该vCPU在活动(运行)期间收到的所有中断都可以由处理器硬件处理,而无需将控制权转移给VMM软件。处理器硬件处理这些通知事件(具有ANV向量值), 是通过将“POST中断描述符”中的所有POST中断传输到vCPU的Virtual-APIC页面,并将其直接传递到vCPU(无需VMM软件干预)。有关英特尔64处理器对APIC虚拟化和POST中断处理的支持的详细信息,请参阅《“英特尔®64体系结构软件开发人员手册,第3卷:系统编程指南”》(‘Intel® 64 Architecture Software Developer's Manual, Volume 3: System Programming Guide’ )。

— vCPU被抢占时(例如,在量子过期时),vCPU状态被指定为“准备运行”。可以通过设置制通知(SN)字段1,指定其POST中断描述符中的该状态。 这允许将该vCPU处于抢占状态的所有非紧急中断投递到其“POST中断描述符”中,而不会产生通知中断(从而避免打断当前运行的vCPU)。 如果存在符合目标为该vCPU的紧急条件的中断源,则VMM软件还可以将“POST中断描述符”中的NV字段修改为WNV向量值。这使VMM软件 可以在紧急中断被投递而vCPU未运行时 接收通知(带有WNV向量值),从而允许采取适当的软件操作(例如抢占当前正在运行的vCPU并立即调度该vCPU)。

— 当虚拟处理器停止运行时(例如,在执行HLT指令时),VMM软件可能会获得控制权,阻止进一步执行vCPU并将vCPU状态指定为“已停止”。 通过使用WNV向量值对其通知向量(NV)字段进行编程,从而在POST中断描述符中指定此状态。这样,当为该虚拟处理器发布任何中断(紧急或非紧急)时,VMM软件就可以接收通知(带有WNV向量值),从而允许采取适当的软件操作(例如调度虚拟处理器或立即激活)。

•进入/恢复虚拟处理器时,VMM软件可以按以下方式处理其POST描述符中的所有未决的POST中断:

— VMM首先通过将POST中断描述符中的通知向量设置为ANV向量值,将虚拟CPU转换为“活动”状态。

— VMM可以检查POST描述符中是否有待处理的中断(例如,通过扫描PIR字段中的非零值)。

— 如果有待处理的POST中断,则VMM可以通过本地xAPIC生成一个向量IPV(同一个逻辑CPU的处理器间中断),其向量值为ANV。一旦在虚拟处理器进入/恢复路径中启用了中断,处理器便会识别此中断。由于vCPU配置由ANV向量值作为“POST中断通知向量”, 因此处理器硬件将对其进行的处理,与虚拟处理器处于活动状态时可能收到的任何通知事件相同。这种方法使VMM软件可以将POST的中断处理(例如通过Virtual-APIC将中断传递到虚拟处理器)“卸载”到处理器硬件, 通过将硬件重新映射到“POST中断描述符”来投递中断时,不不用关系vCPU的调度状态如何。

•VMM软件还可以应用处理器的“后期中断处理”功能,以将VMM软件生成的虚拟中断注入到虚拟机(in addition to 从直接分配的设备到虚拟机的中断)。这可以通过VMM软件以原子方式“将”虚拟中断“发布”到“POST中断描述符”(使用强制执行高速缓存行更新原子性的atomic / LOCK指令)来完成。并生成一个通知事件(作为IPI)给在POST中断描述符中标识为通知目标的逻辑处理器。

•VMM软件可以通过原子地将POST中断描述符中的通知目标(NDST)字段, 更新为虚拟处理器要迁移到的逻辑处理器的物理APIC-ID,来处理跨逻辑处理器的虚拟处理器迁移。这使得来自该虚拟处理器的POST描述符的所有新通知事件都可以路由到新逻辑处理器

5.2.6 Interrupt Posting for Level Triggered Interrupts

通过IOxAPIC重定向表条目生成的电平触发中断(如图5-16所示)可以通过POST中断的中断重映射表条目(IRTE)进行处理(如第9.11节所示)。

但是,与中断重新映射不同,由POST中断处理硬件处理的所有中断(包括级别中断)都被视为边沿触发的中断。

因此,启用水平触发的中断投递的VMM软件必须格外小心,以正确虚拟化虚拟处理器的中断结束(EOI)处理。

例如,VMM软件可以设置vCPU执行控件,使guest软件获得对虚拟APIC控制器的EOI操作的控制权,并通过对产生水平触发中断的IOxAPIC执行DirectedEOI来虚拟化该操作。

软件直接写入IOxAPIC EOI寄存器来操作定向EOI。有关IOxAPIC EOI寄存器的详细信息,请参见IOxAPIC规范。