外部时钟

时钟信号的来源在FPGA芯片外部,通常的,外部时钟对于FPGA来说是必需的,因为FPGA内部没有供内部逻辑使用的时钟和激励电路。

2内部时钟

再生时钟

再生时钟是以一个输入时钟作为参考,在此基础上通过调整其频率和相位产生的新时钟,FPGA中产生再生时钟信号的模块只有PLL和DCM(注意,两者都能产生时钟信号)

时钟域

引入时钟域在于通常一个FPGA设计中会用到多个时钟信号。因此必然涉及到这样一个问题:时钟信号的管理范围时多大?这就是时钟域的问题

时钟树

通常描述的一个电路中,微观来看,由许多触发器构成,那么,问题在于这些触发器所共用的时钟信号能否同时到达每个寄存器的输入端,时钟树的存在就是为了保证信号到达时钟域内不同触发器的时间差最小。

现在注意到这样一个事情:时钟信号由FPGA的外部引脚产生,硬件连接时,需要将外部的时钟电路专门的连接道特定的全局时钟设计管脚,以及FPGA芯片外围引脚也有专门为区域时钟和IO时钟设计的专有引脚。

为什么需要这些专有引脚呢,因为这些引脚具有时钟树管理资源,进而确保时钟能够有正确的时序约束!!!

但是仅仅约束到正确的管脚,未必一定完成了正确的时钟树!!通常还需要进行使用原语这一编程行为来保证时钟信号的正确约束(关于具体的请参考FPGA之道这本书籍)。

跨时钟域问题:

FPGA设计中不可能所有的模块设计都采用一个时钟,因此必然存在跨时钟域问题。

现在思考这样一个问题:

当两个不同时钟域之间进行信息交互的时候,会存在什么问题???

如果两个时钟域的时钟信号从时间上讲,永远对不准,会发生什么???

例子:

“一发一收”穿墙雷达的PLL输出,设置为120MHz,30MHz,20MHz,12MHz。这些频率之间都是有最小公倍数的,即意味着在某一时刻,他们能够满足相位对准。通常我们在进行时钟设计的时候,PLL的输出频率不要完全互质,导致时钟需要很长的周期才能对准。

思考时钟设计背后的意义。

关于时钟树的应用:

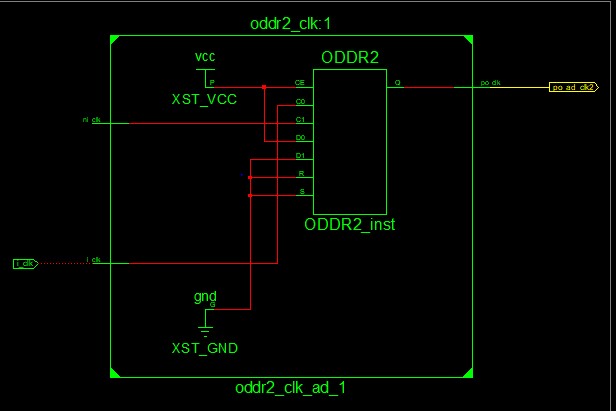

上图是穿墙雷达,AD时钟输入的前端子的原语描述时钟的RTL级网表。网表结构显示,锁相环产生的时钟,如果直接通过IO端连接到AD芯片的时钟输入端,需要引入一个ODDR模块,而这个模块的作用即保证了建立IO时钟的时钟树,这与上文中的描述是一致的。