TLB和Cache本质上都是一种高速的SRAM,Cache存放的是内存中的数据或者代码,而TLB存放的是页表项。

分页是指把物理内存分成固定大小的块,按照页来进行分配和释放。一般常规页大小为4K个字节,之后又因为一些需要,出现了大页,比如2M个字节.

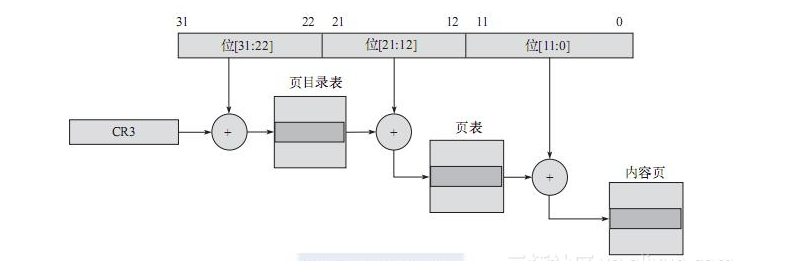

逻辑地址转换物理地址

对于32位X86的处理器来说,把一个逻辑地址分为3段,每一段对应一个偏移地址。查表的顺序如下:

- 根据位

[31:22]加上寄存器CR3存放的页目录表的基址,获得页目录表中对应表项的物理地址,读内存,从内存中获得该表项内容,从而获得下一级页表的基址。 - 根据位

[21:12]页表加上上一步获得的页表基址,获得页表中对应表项的物理地址,读内存,从内存中获得该表项内容,从而获得内容页的基址。 - 根据为

[11:0]加上上一步获得的内容页的基址得到准确的物理地址,读内容获得真正的内容。

TLB

为了提高效率,X86架构的TLB被分为4组:

缓存一般页表(4KB页面)的指令页表缓存(Instruction-TLB)。

缓存一般页表(4KB页面)的数据页表缓存(Data-TLB)。

缓存大尺寸页表(2MB/4MB页面)的指令页表缓存(Instruction-TLB)。

缓存大尺寸页表(2MB/4MB页面)的数据页表缓存(Data-TLB)。

使用大页

使用大页的理由:

- TLB空间很小,使用大页可以减少页表项.

- 提高了命中率.