前一节我们已经详细解释了旁路电容在数字电路系统中所起的基本且重要作用,即储能与为高频噪声电流提供低阻抗路径,尽管还并未给旁路电容的这些功能概括一个“高大上”的名字,然而旁路电容所起的终极作用就是为了电源完整性(Power Integrity, PI),它与信号完整性(Signal Integrity, SI)均为高速数字PCB设计中的重要组成部分,后续有机会我们将会进行详细讲解。

事实上,旁路电容的这两个基本功能在某种意义上来讲是完全统一的:你可以认为旁路电容的储能为高频开关切换(充电)提供瞬间电荷,从而避免开关产生的高频噪声向距离芯片更远的方向扩散,因为开关切换需要的能量已经在靠近芯片的旁路电容中获取到了,你也可以认为旁路电容提供了高频噪声电流的低阻抗路径,从而避免了高频开关时需要向更远的电源索取瞬间电荷能量。

有一定经验的工程师都会发现:旁路电容的容值大多数为0.1uF(100nF),这也是数字电路中最常见的,如下图所示为FPGA芯片的旁路电容:

那这个值是怎么来的呢?这一节我们就来讨论一下这个问题。

前面已经提到过,实际的电容器都有自谐振频率,考虑到这个因素,作为数字电路旁路电容的容量一般不超过 1uF,当然,容量太小也不行,因为储存的电荷无法满足开关切换时瞬间要求的电荷,那旁路电容的容量到底应该至少需要多大呢?我们用最简单的反相器逻辑芯片(74HC04)实例计算一下就知道了。

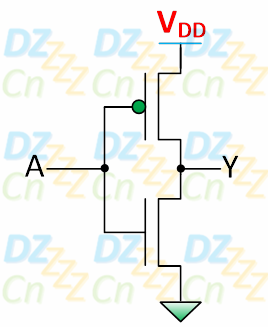

实际芯片的每个逻辑门基本结构如下图所示(以下均来自Philips 74HC04数据手册)

而每个CMOS反相器的基本结构如下图所示(具体参考文章【逻辑门(1)】):

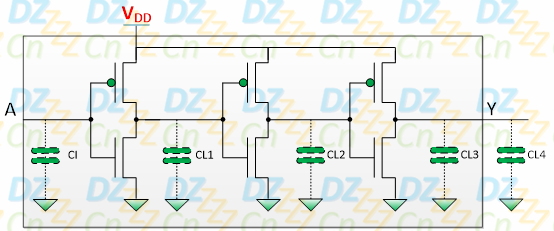

每个逻辑非门(Gate)由三个反相器串联组成,如下图所示(芯片为什么会这样设计可参考文章“逻辑门”):

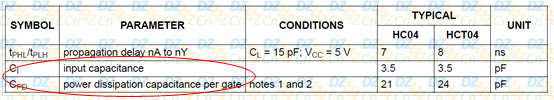

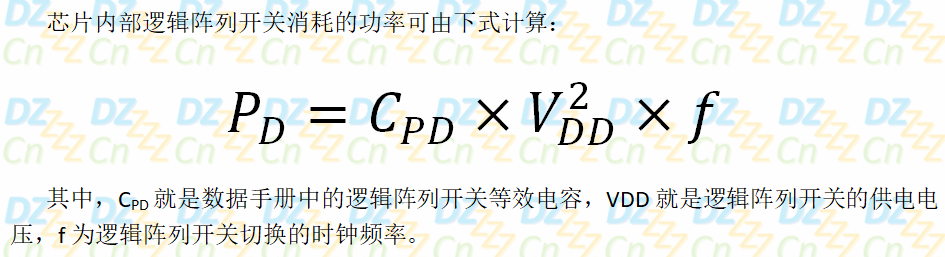

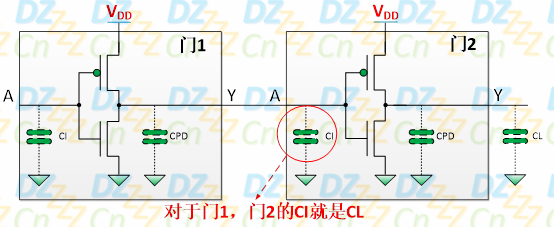

上图中,CI表示芯片信号引脚的输入电容(Input capacitance),CL表示输出负载电容(Output Load capacitance)。对于每一级反相器,后一级反相器的输入电容CI即作为前一级开关的输出负载电容,当然,反相器开关本身也会有一定的输出寄生电容,它们也包含在CL内,一个逻辑非门(包含三个反相器)的所有等效负载电容就是内部逻辑阵列开关在切换时需要向电源VDD索取能量的来源(换言之,开关切换时需要对这个等效负载电容进行充放电操作),这个逻辑阵列开关等效电容在数据手册中通常用CPD(power dissipation capacitance per gate)表示,如下图所示 :

注意:在这个数据手册中,CPD是一个逻辑非门(Per Gate)的开关等效电容。

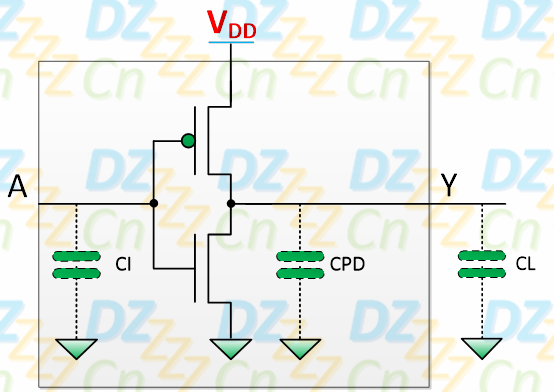

在74HC04芯片中,CPD就相当于是CL1、CL2、CL3的等效电容(不一定是简单的相加),而CL4取决于芯片外接负载,因此,我们也可以将电路等效如下图所示:

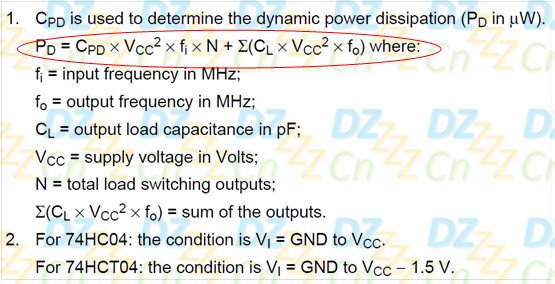

有人问:这个公式怎么来的?权威么?我书读得少,不要骗我!数据手册中有呀,如下图所示:

上图中的公式分成了两个部分,但结构是一模一样的,前面一部分与我们给出的公式是相同的,表示芯片内部逻辑阵列开关等效负载电容CPD的功耗,而后一部分与芯片外接负载CL有关(也称之为等效IO开关电容),输出引脚IO连接有多少个负载,就将相应负载电容CL的功耗全部计算起来,如下图所示:

有人问:输入电容CI就不计算进去吗?乖乖,对于芯片输出引脚连接的负载而言,负载的输入电容CI就是引脚的等效负载电容CL呀,输出负载连接(并联)越多,则等效负载电容CL就越大,消耗的功率也就越大,如下图所示:

一般而言,CL(CI)值是总是相对容易找到的,数据手册中通常都会有,因为输出连接什么负载你肯定是知道的,但CPD却不一定在数据手册能查得到,因此,我们在计算芯片的功耗时可能会分为芯片内与芯片外两个部分。

最基础的数据计算方法我们已经知道了,有两种方法可以估算旁路电容的最小容量:

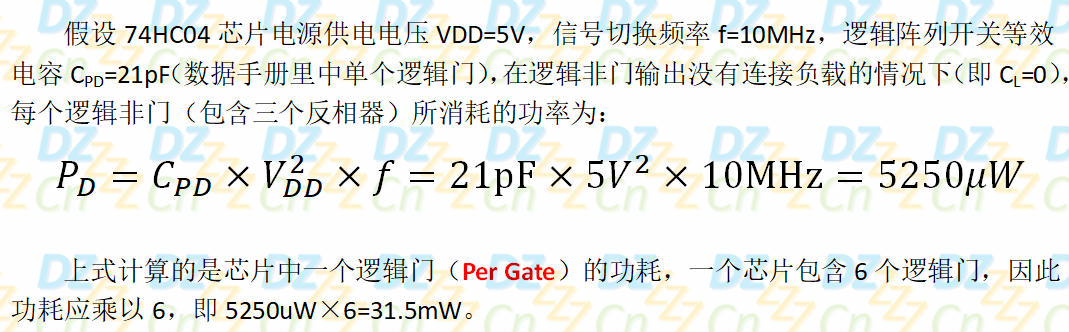

第一种计算方法思路:逻辑阵列开关等效电容(CPD)需要获取足够的电荷能量,那芯片的旁路电容的容量必定不能比芯片总CPD更小,通常旁路电容的容量比芯片总CPD大25~100倍,我们称其为旁路电容倍乘系数(bypass capacitor multiplier,这里取个中间数50),由于74HC04包含六个逻辑非门,从数据手册上也可以查到CPD约为21pF,因此,芯片总CPD应为21pF×6=126pF,再考虑到50倍的旁路电容系数,旁路电容的容量必须要大于126pF×50=6.3nF。

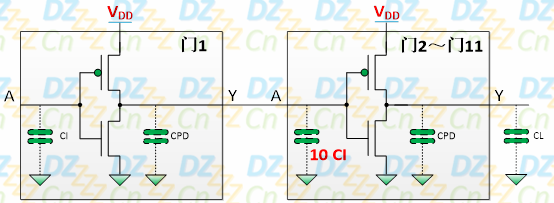

以上计算的是芯片输出未连接负载的情况,假设反相器后面并接了10个逻辑非门(CMOS门电路的扇出系数一般为20~25),则此时等效电路如下图所示:

对于门1 来说,此时芯片的输出负载电容CL=10×CI=10×7pF=70pF,对于整个系统而言,这个CL也可以算是门1的逻辑阵列开关等效电容,因为从图上可以看出,它消耗的是门1的电源能量(而不是门2~门11),这样根据上述同样的算法,门1外接旁路电容的容量至少应为(21pF+70pF)×50=4.55nF,当然,这只是一个逻辑非门的计算结果,如果芯片中其它5个非门也是同样的负载连接,则需要的旁路电容容量至少应为4.55nF×6=27.3nF,在考虑到电路设计裕量情况下,我们可以直接选择100nF的旁路电容。

那功耗PD计算的意义在哪里?前面我们是走了狗屎运,芯片够简单,所以数据手册里提供了CPD的具体值,但更多的应用场合下是没有办法直接获取这个值的,我们看看更大规模集成芯片的情况。