原文链接:

FPGA开发全攻略连载之八:从可编程器件发展看FPGA未来趋势

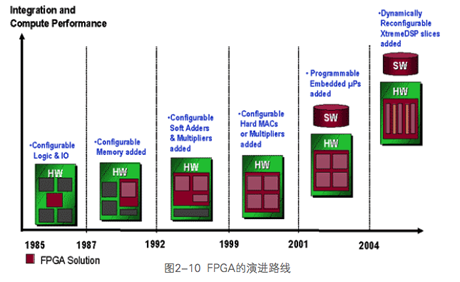

可编程逻辑器件的发展历史可编程逻辑器件的发展可以划分为4个阶段,即从20世纪70年代初到70年代中为第1段,20世纪70年代中到80年代中为第2阶段,20世纪80年代到90年代末为第3阶段,20世纪90年代末到目前为第4阶段。

第1阶段的可编程器件只有简单的可编程只读存储器(PROM)、紫外线可擦除只读存储器(EPROM)和电可擦只读存储器(EEPROM)3种,由于结构的限制,它们只能完成简单的数字逻辑功能。

第2阶段出现了结构上稍微复杂的可编程阵列逻辑(PAL)和通用阵列逻辑(GAL)器件,正式被称为PLD,能够完成各种逻辑运算功能。典型的PLD由“与”、“非”阵列组成,用“与或”表达式来实现任意组合逻辑,所以PLD能以乘积和形式完成大量的逻辑组合。

第3阶段赛灵思和Altera分别推出了与标准门阵列类似的FPGA和类似于PAL结构的扩展性CPLD,提高了逻辑运算的速度,具有体系结构和逻辑单元灵活、集成度高以及适用范围宽等特点,兼容了PLD和通用门阵列的优点,能够实现超大规模的电路,编程方式也很灵活,成为产品原型设计和中小规模(一般小于10000)产品生产的首选。这一阶段,CPLD、FPGA器件在制造工艺和产品性能都获得长足的发展,达到了0.18 工艺和系数门数百万门的规模。

第4阶段出现了SOPC和SOC技术,是PLD和ASIC技术融合的结果,涵盖了实时化数字信号处理技术、高速数据收发器、复杂计算以及嵌入式系统设计技术的全部内容。赛灵思和Altera也推出了相应SOCFPGA产品,制造工艺达到65nm ,系统门数也超过百万门。并且,这一阶段的逻辑器件内嵌了硬核高速乘法器、Gbits差分串行接口、时钟频率高达500MHz的PowerPC™微处理器、软核MicroBlaze、Picoblaze、Nios以及NiosII,不仅实现了软件需求和硬件设计的完美结合,还实现了高速与灵活性的完美结合,使其已超越了ASIC器件的性能和规模,也超越了传统意义上FPGA的概念,使PLD的应用范围从单片扩展到系统级。未来,赛灵思高层透露,该公司正在研制采用全新工艺的新型FPGA,这种FPGA将集成更大的存储单元和其他功能器件,FPGA正向超级系统芯片的方向发展!2月5日,赛灵思发布了采用40nm和45nm的Spartan-6和Virtex-6 FPGA系列,并开启了目标设计平台这一新的设计理念,相信FPGA的应用会得到更大的发展!

1984年,赛灵思发明了现场可编程门阵列(FPGA),同时它成为全球首家无晶圆半导体公司的鼻祖,赛灵思通过不断应用尖端技术来长久保持它的行业领袖地位:赛灵思 是首家采用180nm、150nm、130nm、90nm和65nm工艺技术的企业,目前提供约占世界 90% 的高端 65nm FPGA产品。据 iSuppli 的统计数据,2007年它拥有世界51%以上的可编程器件市场份额。目前FPGA领域主要的供应商是赛灵思、Altera、Actel和Lattice。其中Altera和赛灵思主要生产一般用途FPGA,其主要产品采用RAM工艺。Actel 主要提供非易失性FPGA,产品主要基于反熔丝工艺和FLASH工艺。

由于赛灵思一直在FPGA开发领域方面拥有领先优势和最大份额,故本文主要介绍赛灵思公司的FPGA产品。

3.1.1 赛灵思主要产品介绍

目前赛灵思公司有两大类FPGA产品:Spartan类和Virtex类,前者主要面向低成本的中低端应用,是目前业界成本最低的一类FPGA;后者主要面向高端应用,属于业界的顶级产品。这两个系列的差异仅限于芯片的规模和专用模块上,都采用了先进的0.13 、90甚至65制造工艺,具有相同的卓越品质。

1.Spartan类FPGA

Spartan系列适用于普通的工业、商业等领域,目前主流的芯片包括:Spartan-2、Spartan-2E、Spartan-3、Spartan-3A、Spartan-3E以及最新的Spartan-6等种类。其中Spartan-2最高可达20万系统门,Spartan-2E最高可达60万系统门,Spartan-3最高可达500万门,Spartan-3A和Spartan-3E不仅系统门数更大,还增强了大量的内嵌专用乘法器和专用块RAM资源,具备实现复杂数字信号处理和片上可编程系统的能力。

(1)Spartan-2系列

Spartan-2在Spartan系列的基础上继承了更多的逻辑资源,达到更高的性能,芯片密度高达20万系统门。由于采用了成熟的FPGA结构,支持流行的接口标准,具有适量的逻辑资源和片内RAM,并提供灵活的时钟处理,可以运行8位的PicoBlaze软核,主要应用于各类低端产品中。其主要特点如下所示: 采用0.18 工艺,密度达到5292逻辑单元; 系统时钟可以达到200MHz; 采用最大门数为20万门,具有延迟数字锁相环; 具有可编程用户I/O; 具有片上块RAM存储资源;

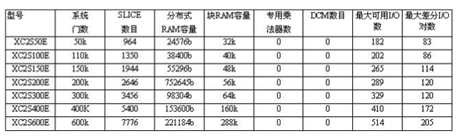

Spartan-2系列产品的主要技术特征如下表所示。

表3-1 Spartan-2系列FPGA主要技术特征

(2)Spartan-2E系列

Spartan-2E基于Virex-E架构,具有比Spartan-2更多的逻辑门、用户I/O和更高的性能。赛灵思还为其提供了包括存储器控制器、系统接口、DSP、通信以及网络等IP核,并可以运行CPU软核,对DSP有一定的支持。其主要特点如下所示: 采用0.15工艺,密度达到15552逻辑单元; 最高系统时钟可达200MHz; 最大门数为60万门,最多具有4个延时锁相环; 核电压为1.2V,I/Q电压可为1.2V、3.3V、2.5V,支持19个可选的I/O标准; 最大可达288k的块RAM和221K的分布式RAM;

Spartan-2E系列产品的主要技术特征如下表所示。

表3-2 Spartan-2E系列FPGA主要技术特征

(3)Spartan-3系列

Spartan-3基于Virtex-II FPGA架构,采用90技术,8层金属工艺,系统门数超过5百万,内嵌了硬核乘法器和数字时钟管理模块。从结构上看,Spartan-3将逻辑、存储器、数学运算、数字处理器处理器、I/O以及系统管理资源完美地结合在一起,使之有更高层次、更广泛的应用,获得了商业上的成功,占据了较大份额的中低端市场。其主要特性如下: 采用90工艺,密度高达74880逻辑单元;最高系统时钟为340MHz; 具有的专用乘法器; 核电压为1.2V,端口电压为3.3V、2.5V、1.2V,支持24种I/O标准;高达520k分布式RAM和1872k的块RAM; 具有片上时钟管理模块(DCM); 具有嵌入式Xtrema DSP功能,每秒可执行3300亿次乘加。

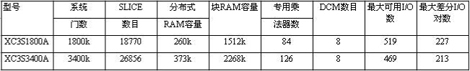

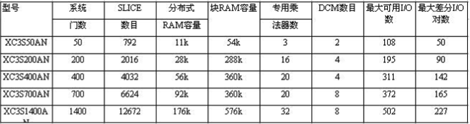

Spartan-3系列产品的主要技术特征如下表所示。

表3-3 Spartan-3系列FPGA主要技术特征

(4)Spartan-3A/3ADSP/3AN系列

Spartan-3A在Spartan-3和Spartan-3E平台的基础上,整合了各种创新特性帮助客户极大地削减了系统总成本。利用独特的器件DNA ID技术,实现业内首款FPGA电子序列号;提供了经济、功能强大的机制来防止发生窜改、克隆和过度设计的现象。并且具有集成式看门狗监控功能的增强型多重启动特性。支持商用 lash存储器,有助于削减系统总成本。其主要特性为: 采用90工艺,密度高达74880逻辑单元; 工作时钟范围为5MHz~320MHz; 领先的连接功能平台,具有最广泛的IO标准(26 种,包括新的TMDS和PPDS)支持; 利用独特的Device DNA序列号实现的业内首个功能强大的防克隆安全特性; 五个器件,具有高达1.4M的系统门和502个I/O; 灵活的功耗管理。

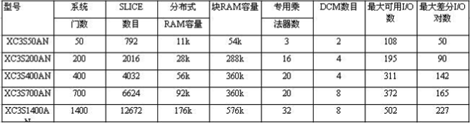

Spartan-3A系列产品的主要技术特征如下表所示。

表3-4 Spartan-3A系列FPGA主要技术特征

表3-4 Spartan-3A系列FPGA主要技术特征

Spartan-3ADSP平台提供了最具成本效益的 DSP 器件,其架构的核心就是 XtremeDSP DSP48A slice,还提供了性能超过30GMAC/s、存储器带宽高达2196 Mbps的新型 XC3SD3400A和XC3SD1800A器件。新型Spartan-3A DSP 平台是成本敏感型 DSP 算法和需要极高DSP性能的协处理应用的理想之选。其主要特征如下所示。 采用90 工艺,密度高达74880逻辑单元; 内嵌的DSP48A可以工作到250MHz; 采用结构化的SelectRAM架构,提供了大量的片上存储单元; VCCAUX的电压支持2.5V和3.3V,对于3.3V的应用简化了设计;低功耗效率,Spartan-3A DSP器件具有很高的信号处理能力4.06 GMACs/mW。

Spartan-3ADSP系列产品的主要技术特征如下表所示。

表3-5 Spartan-3ADSP系列 FPGA主要技术特征

表3-5 Spartan-3ADSP系列 FPGA主要技术特征

Spartan-3AN芯片为最高级别系统集成的非易失性安全FPGA,提供下列2个独特的性能:先进SRAM FPGA的大量特性和高性能以及非易失性FPGA的安全、节省板空间和易于配置的特性。Spartan-3AN平台是对空间要求严苛和/或安全应用及低成本嵌入式控制器的理想选择。Spartan-3AN平台的关键特性包括: 业界首款90nm非易失性FPGA,具有可以实现灵活的、低成本安全性能的Device DNA电子序列号; 业内最大的片上用户Flash,容量高达11Mb; 提供最广泛的I/O标准支持,包括26种单端与差分信号标准 灵活的电源管理模式,休眠模式下可节省超过40%的功耗 五个器件,具有高达1.4M的系统门和502个I/O。

Spartan-3AN系列产品的主要技术特征如下表所示

表3-6 Spartan-3AN系列 FPGA主要技术特征

表3-6 Spartan-3AN系列 FPGA主要技术特征

(5)Spartan-3E系列

Spartan-3E是目前Spartan系列最新的产品,具有系统门数从10万到160万的多款芯片,是在

Spartan-3成功的基础上进一步改进的产品,提供了比Spartan-3更多的I/O端口和更低的单位成本,是赛灵

思公司性价比最高的FPGA芯片。由于更好地利用了90 技术,在单位成本上实现了更多的功能和处理带宽,是

赛灵思公司新的低成本产品代表,是ASIC的有效替代品,主要面向消费电子应用,如宽带无线接入、家庭网

络接入以及数字电视设备等。其主要特点如下: 采用90 工艺; 大量用户I/O端口,最多可支持376个I/O端口

或者156对差分端口; 端口电压为3.3V、2.5V、1.8V、1.5V、1.2V ; 单端端口的传输速率可以达到622 ,支

持DDR接口; 最多可达36个 的专用乘法器、648 块RAM、231 分布式RAM; 宽的时钟频率 以及多个专用片

上数字时钟管理(DCM)模块。

Spartan-3E系列产品的主要技术特征如下表所示。

表3-7 Spartan-3E系列FPGA主要技术特征

表3-7 Spartan-3E系列FPGA主要技术特征

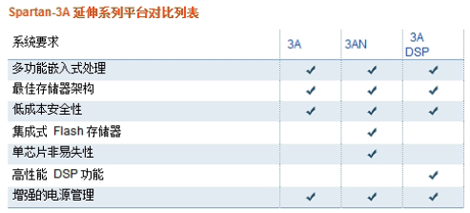

表3-8 Spartan-3A延伸系列品台性能对比

表3-8 Spartan-3A延伸系列品台性能对比

(6)Spartan-6系列

作为Spartan FPGA系列的第六代产品,Spartan-6 FPGA系列采用可靠的低功耗45nm 9层金属布线双层氧化工艺技术生产。 这一新系列产品实现了低风险、低成本、低功耗以及高性能的完美平衡。 Spartan-6 FPGA系列的高效双寄存器6输入LUT(查找表)逻辑结构利用了可靠成熟的Virtex架构,支持跨平台兼容性以及优化系统性能。 丰富的内建系统级模块包括DSP逻辑片、高速收发器以及PCI Express®接口内核,也源于Virtex系列,能够提供更高程度的系统级集成。

Spartan-6 FPGA系列专门针对成本和功率敏感的市场(如汽车娱乐、平板显示以及视频监控)采用了特殊技术。 新的高性能集成存储器控制器支持DDR、DDR2、DDR3和移动 DDR存储器,硬内核的多端口总线结构能够提供可预测的时序和高达DDR2/DDR3 800 (400MHz)的性能。 在设计向导的支持下,为Spartan-6 FPGA构建存储控制器的过程变得非常简单和直接。

先进功率管理技术方面的创新以及可选的1.0v低功耗内核使得Spartan-6 FPGA能够比前一代Spartan系列功耗降低多达65%。 快速灵活的I/O支持超过12Gbps的存储器访问带宽,兼容3.3v电压并且采用了更为绿色的RoHS兼容无铅封装。

Spartan-6系列产品的主要技术特征如下表所示:

表3-9 Spartan-6系列FPGA主要技术特征

表3-9 Spartan-6系列FPGA主要技术特征2.Virtex系列FPGA

Virtex系列是赛灵思的高端产品,也是业界的顶级FPGA产品,赛灵思公司正是凭借Virtex系列产品赢得市场,从而获得FPGA供应商领头羊的地位。可以说赛灵思以其Virtex-5、Virtex-4、Virtex-2 Pro和Virtex-2系列FPGA产品引领现场可编程门阵列行业。主要面向电信基础设施、汽车工业、高端消费电子等应用。目前的主流芯片包括:Vitrex-2、Virtex-2 Pro、Virtex-4和Virtex-5等种类。

(1)Vitrex-2系列

Vitrex-2系列具有优秀的平台解决方案,这进一步提升了其性能;且内置IP核硬核技术,可以将硬IP核分配到芯片的任何地方,具有比Virtex系列更多的资源和更高的性能。其主要特征如下所示: 采用0.15/0.12 工艺; 核电压为1.5V,工作时钟可以达到420MHz; 支持20多种I/O接口标准; 内嵌了多个 硬核乘法器,提高了DSP处理能力; 具有完全的系统时钟管理功能,多达12个DCM模块。

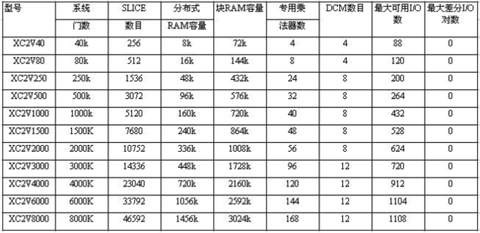

Virtex-2系列产品的主要技术特征如下表所示。

表3-10 Virtex-2系列 FPGA主要技术特征

表3-10 Virtex-2系列 FPGA主要技术特征

(2)Virtex-2Pro系列

Virtex-2 Pro系列在Virtex-2的基础上,增强了嵌入式处理功能,内嵌了PowerPC™405内核,还包括了先进的主动互联(Active Interconnect)技术,以解决高性能系统所面临的挑战。此外还增加了高速串行收发器,提供了千兆以太网的解决方案。其主要特征如下所示: 采用0.13 工艺; 核电压为1.5V,工作时钟可以达到420MHz; 支持20多种I/O接口标准; 增加了2个高性能RISC技术、频率高达400MHz的PowerPC™处理器;增加多个3.125Gbps速率的Rocket串行收发器; 内嵌了多个 硬核乘法器,提高了DSP处理能力; 具有完全的系统时钟管理功能,多达12个DCM模块。

Virtex-2 Pro系列产品的主要技术特征如下表所示。

表3-11 Virtex-2 Pro系列 FPGA主要技术特征

表3-11 Virtex-2 Pro系列 FPGA主要技术特征

(3)Virtex-4系列

Virtex-4器件整合了高达200,000个的逻辑单元,高达500 MHz的性能和无可比拟的系统特性。Virtex-4产品基于新的高级硅片组合模块(ASMBL)架构,提供了一个多平台方式(LX、SX、FX),使设计者可以根据需求选用不同的开发平台;逻辑密度高,时钟频率能够达到500MHz;具备DCM模块、PMCD相位匹配时钟分频器、片上差分时钟网络;采用了集成FIFO控制逻辑的500MHz SmartRAM技术,每个I/O都集成了ChipSync源同步技术的1 Gbps I/O和Xtreme DSP逻辑片。其主要特点如下: 采用了90 工艺,集成了高达20万的逻辑单元;系统时钟500MHz; 采用了集成FIFO控制逻辑的500MHz Smart RAM 技术; 具有DCM模块、PMCD相位匹配时钟分频器和片上差分时钟网络; 每个I/O都集成了ChipSync源同步技术的1Gbps I/O; 具有超强的信号处理能力,集成了数以百计的XtremeDSP Slice,单片最大的处理速率为 。 Virtex-4 LX平台FPGA的特点是密度高达20万逻辑单元,是全球逻辑密度最高的FPGA系列之一,适合对逻辑门需求高的设计应用。

Virtex-4 SX平台提高了DSP、RAM单元与逻辑单元的比例,最多可以提供512个XtremeDSP硬核,可以工作在500MHz,其最大的处理速率为 ,并可以以其创建40多种不同功能,并能多个组合实现更大规模的DSP模块。与Virtex-2 Pro系列相比,还大大降低了成本和功耗,具有极低的DSP成本。SX平台的FPGA非常适合应用于高速、实时的数字信号处理领域。

Virtex-4 FX平台内嵌了1~2个32位RISC PowerPC™处理器,提供了4个1300 Dhrystone MIPS、10/100/1000自适应的以太网MAC内核,协处理器控制器单元(APU)允许处理器在FPGA中构造专用指令,使FX器件的性能达到固定指令方式的20倍;此外,还包含24个Rocket I/O串行高速收发器,支持常用的0.6Gbps、1.25 Gbps、2.5 Gbps、3.125 Gbps、4 Gbps、6.25 Gbps、10 Gbps等高速传输速率。FX平台适用于复杂计算和嵌入式处理应用。

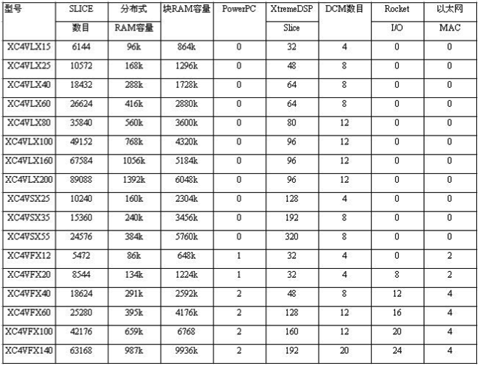

Virtex-4系列产品的主要技术特征如下表所示。

表3-12 Virtex-4系列 FPGA主要技术特征

表3-12 Virtex-4系列 FPGA主要技术特征

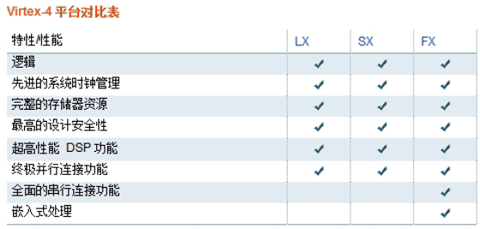

表3-13 Virtex-4系列平台性能对比

表3-13 Virtex-4系列平台性能对比

(5)Virtex-5系列

Virtex®-5 FPGA 是世界上首款 65nm FPGA 系列,采用 1.0v、三栅极氧化层工艺技术制造而成,并且根据所选器件可以提供 330,000 个逻辑单元、1,200 个 I/O 引脚、48 个低功耗收发器以及内置式PowerPC™440、PCIe® 端点和以太网 MAC 模块。已经提供了5种系列平台,分别是LX、LXT 、SXT、FXT、TXT,每种平台都在高性能逻辑、串行连接功能、信号处理和嵌入式处理性能方面实现了最佳平衡。例如LX针对高性能逻辑进行了优化,LXT针对具有低功耗串行连接功能的高性能逻辑进行了优化,SXT针对具有低功耗串行连接功能的DSP 和存储器密集型应用进行了优化。Virtex-5 FXT 则用于实现具有速率最高的串行连接功能的嵌入式处理,Virtex-5 TXT可用于实现超高带宽应用,如有线通信与数据通信系统内的桥接、开关和集聚。

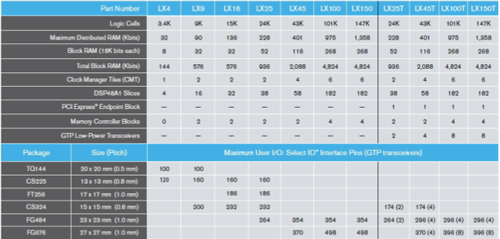

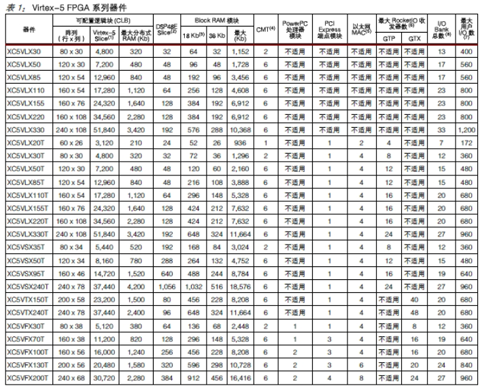

现有的Virtex-5系列产品的主要技术特征如下表所示。

表3-14 Virtex-5系列 FPGA主要技术特征

表3-14 Virtex-5系列 FPGA主要技术特征

其主要特点如下:

采用了最新的65工艺,结合低功耗IP块将动态功耗降低了35%;此外,还利用65nm三栅极氧化层技术保持低静态功耗; 利用65nm ExpressFabric技术,实现了真正的6输入LUT,并将性能提高了2个速度级别。内置有用于构建更大型阵列的FIFO逻辑和ECC的增强型36 Kbit Block RAM带有低功耗电路,可以关闭未使用的存储器。 逻辑单元多达330,000个,可以实现无与伦比的高性能; I/O引脚多达1,200个,可以实现高带宽存储器/网络接口,1.25 Gbps LVDS; 低功耗收发器多达24个,可以实现100 Mbps - 3.75 Gbps高速串行接口; 核电压为1V,550 MHz系统时钟; 550 MHz DSP48E slice内置有25 x 18 MAC,提供352 GMACS的性能,能够在将资源使用率降低50%的情况下,实现单精度浮点运算; 利用内置式PCIe端点和以太网MAC模块提高面积效率 ; 更加灵活的时钟管理管道(Clock Management Tile)结合了用于进行精确时钟相位控制与抖动滤除的新型PLL和用于各种时钟综合的数字时钟管理器(DCM); 采用了第二代sparse chevron封装,改善了信号完整性,并降低了系统成本; 增强了器件配置,支持商用flash存储器,从而降低了成本。

注:一个Virtex-5 Slice具有4个LUT和4个触发器,而一个前文所提及的常规Slice只包含2个LUT个2个触发器。每个DSP48E包含一个25*18位的硬核乘法器、一个加法器和一个累加器。

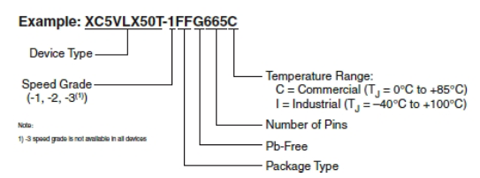

Virtex-5 FPGA 订购信息适用于所有封装,包括无铅封装

Virtex-5 FPGA 订购信息适用于所有封装,包括无铅封装

(6)Virtex-6 FPGA系列

基于采用第三代Xilinx ASMBL™ 架构的40nm制造工艺,Virtex-6 FPGA系列还拥有新一代开发工具和早已针对Virtex-5 FPGA而开发的广泛IP库支持。这些都为多产的开发和设计移植提供了强大的支持。 与竞争厂商提供的40nm FPGA产品相比,新的Virtex-6 FPGA系列器件性能提高15%,功耗降低15%。新器件在1.0v内核电压上操作,同时还有可选的0.9v低功耗版本。 这些使得系统设计师可在设计中采用Virtex-6 FPGA,从而支持建设“绿色”中心办公室和数据中心。对于电信行业这一点特别重要,因为该行业正在扩展对因特网视频和富媒体内容的支持。

Virtex- 6 FPGA系列包括三个面向应用领域而优化的FPGA平台,分别提供了不同的特性和功能组合来更好地满足不同客户应用的需求:

Virtex-6 LXT FPGA—优化目标应用需要高性能逻辑、DSP以及基于低功耗GTX 6.5Gbps串行收发器的串行连接能力。

Virtex-6 SXT FPGA—优化目标应用需要超高性能DSP以及基于低功耗GTX 6.5Gbps串行收发器的串行连接能力。

Virtex-6 HXT FPGA—作为优化的通信应用需要最高的串行连接能力,多达64个GTH串行收发器可提供高达11.2Gbps带宽 。

Virtex-6 FPGA把先进的硬件芯片技术、创新的电路设计技术以及架构上的增强完美结合在一起,与前一代Virtex器件以及竞争FPGA产品相比,功耗大大降低,性能更高并且成本更低。表3-15显示了Virtex-6FPGA系列主要技术特征。

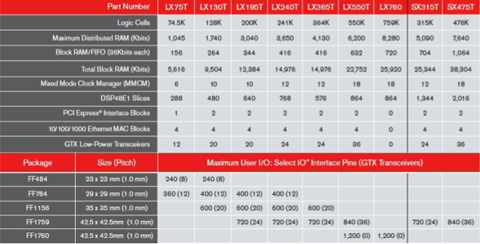

表3-15 Virtex-6 FPGA系列主要技术特征

表3-15 Virtex-6 FPGA系列主要技术特征

(7)Xilinx PROM芯片介绍

赛灵思公司的Platform Flash PROM能为所有型号的Xilinx FPGA提供非易失性存储。全系列PROM的容量范围为1Mbit到32Mbit,兼容任何一款Xilinx FPGA芯片,具备完整的工业温度特性(-40°C 到 +85°C),支持IEEE1149.1所定义的JTAG边界扫描协议。

PROM芯片可以分成3.3V核电压的 系列和1.8V核电压的 系列两大类,前者主要面向底端引用,串行传输数据,且容量较小,不具备数据压缩的功能;后者主要面向高端的FPGA芯片,支持并行配置、设计修订(Designing Revisioning)和数据压缩(Compression)等高级功能,以容量大、速度快著称,其详细参数如下表所示。

表3-16 赛灵思公司PROM芯片总结 (截至2008年11月数据)

表3-16 赛灵思公司PROM芯片总结 (截至2008年11月数据)

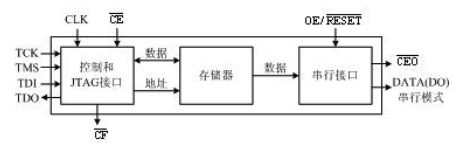

该系列包含XCF01S、XCF02S和XCF04S(容量分别为:1Mb、2Mb和4Mb),其共同特征有3.3V核电压,串行配置接口以及SOIC封装的VO20封装。 内部控制信号、数据信号、时钟信号和JTAG信号的整体结构如图3-2所示。

图3-2 XCF01S/XCF02S/XCF04S PROM结构组成框图

图3-2 XCF01S/XCF02S/XCF04S PROM结构组成框图

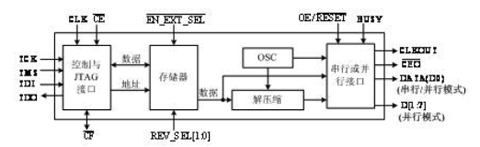

系列有XCP08P、XCF16P和XCF32P(容量分别为:8Mb、16Mb和32Mb),其共同特征有1.8V核电压、串行或并行配置接口、设计修订、内嵌的数据压缩器、FS48封装或VQ48封装和内嵌振荡器。 内部控制信号、数据信号、时钟信号和JTAG信号的整体结构如图3-3所示,其先进的结构和更高的集成度在使用中带来了极大的灵活性。

图3-3 XCP08P/XCF16P/XCF32P PROM结构组成框图

图3-3 XCP08P/XCF16P/XCF32P PROM结构组成框图

值得一提的是系列设计修正和数据压缩这两个功能。设计修订功能在FPGA加电启动时改变其配置数据,根据所需来改变FPGA的功能,允许用户在单个PROM中将多种配置存储为不同的修订版本,从而简化FPGA配置更改,在FPGA内部加入少量的逻辑,用户就能在PROM中存储多达4个不同修订版本之间的动态切换。数据压缩功能可以节省PROM的空间,最高可节约50%的存储空间,从而降低成本,是一项非常实用的技术。当然如果编程时在软件端采用了压缩模式,则需要一定的硬件配置来完成相应的解压缩。