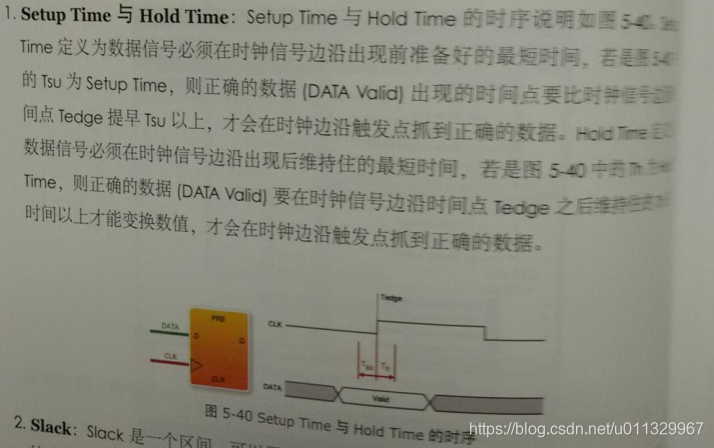

建立保持时间:

亚稳态:metastability

![]()

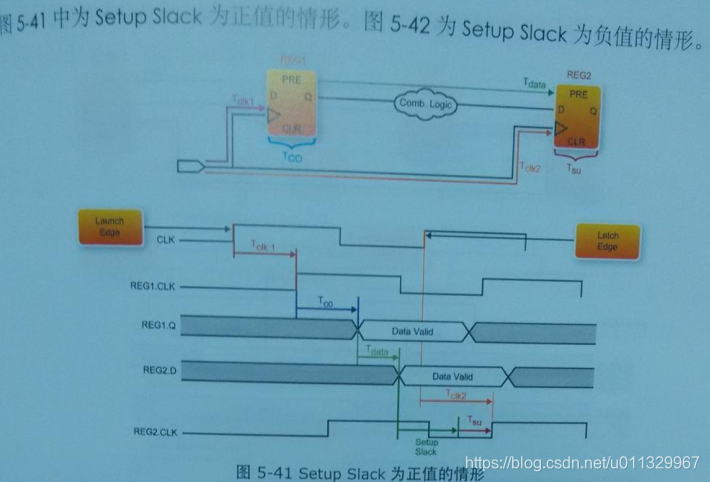

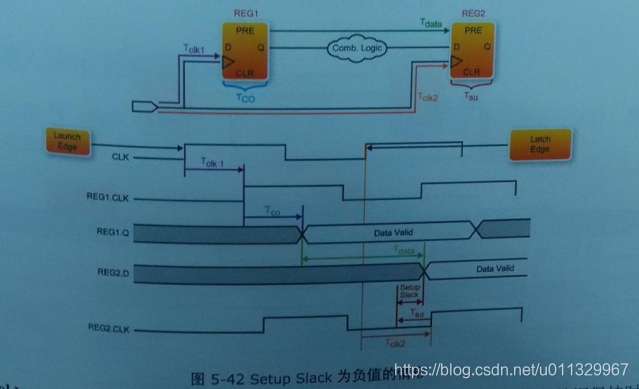

Slack:

Setup Slack

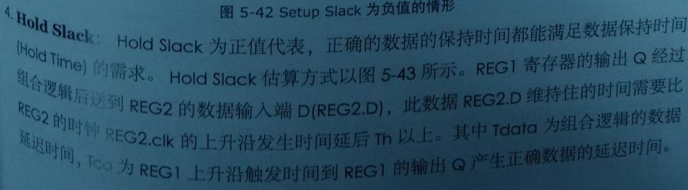

Hold slack:

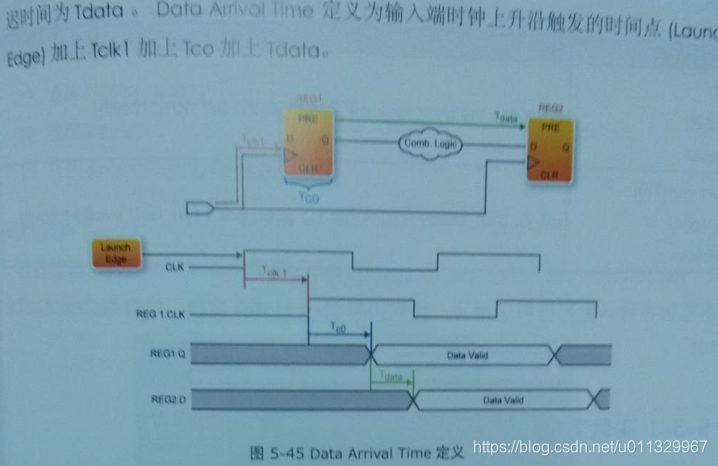

Data Arrival Time

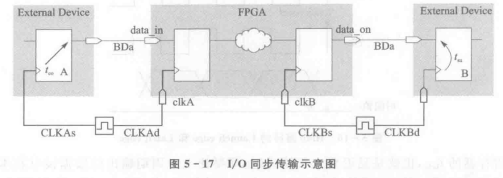

系统同步系统(当时钟和数据一起传时称为源同步系统,比如常见的SPI/I2C都有一个CLK信号):

SDC命令简介:

create_clock

-------------------------------------------------------------------------------------------------

set_clock_groups -logically_exclusive -physically_exclusive -asynchronous -group [get_clocks clkname -include_generated_clocks]

1、逻辑互斥:对于设计中使用MUX时使用

2、物理互斥: 对于设计中没有路径交互、完全独立时使用

3、异步:对于设计中没有相位关系时使用,比如跨时钟域的路径就指定为异步

set_clock_groups 只能指定三个选项中的一个

-------------------------------------------------------------------------------------------------

set_clock_uncertainty

-------------------------------------------------------------------------------------------------

set_max_delay

-------------------------------------------------------------------------------------------------

set_input_delay -max

set_input_delay -min

-------------------------------------------------------------------------------------------------

set_output_delay -max

set_output_delay -min

-------------------------------------------------------------------------------------------------

set_false_path

set_muticycle_path

操作示例

在Quartus工具栏点击小时钟:

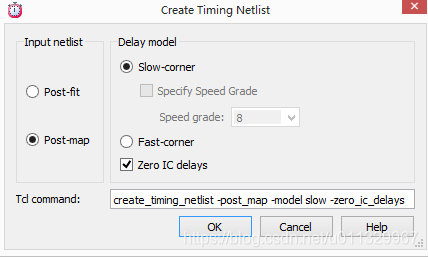

1、建立时序分析网表【第一次选择post-map[初次创建SDC文件],第二次选择post-fit】

2、

整理自:

1、<<FPGA深度分析>>

2、<<逻辑电路设计 DE2-115 实战宝典>>

3、综合与时序分析的设计约束 韩德强等 译

参考: