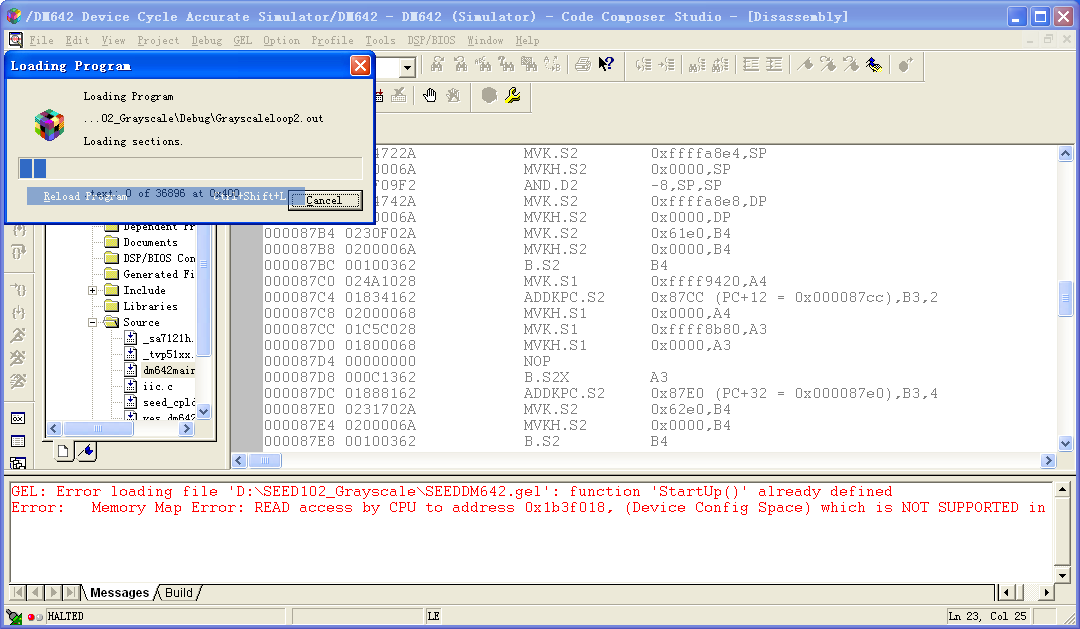

load程序到DM642开发板上之后,点击了run按钮出现了如下的错误:

Memory map error:READ access by cpu to address 0x1b3f018(Device Config Space)which is not supported in simulator

我检查了CMD文件应该是没有问题的,CMD代码内容如下:

1 /* 2 * Copyright (C) 2004 SEED Incorporated 3 * All Rights Reserved 4 */ 5 /* 6 *---------timer1.cmd--------- 7 * 8 */ 9 -l.libcslDM642.lib 10 -l.lib ts6400.lib 11 MEMORY 12 { 13 L2 : o = 00000400h l = 0003fb00h /* all SRAM ,L2,为DSP片内存储器,是第2级存储器 14 [第一级存储器包括独立的程序Cach(L1P)和数据Cach(L1D) ],它是一个统一的空间, 15 部分程序和数据,统称为L2,可以作为普通的SRAM映射到存储空间 */ 16 CE01: o = 80000000h l = 00100000h /* external memory */ 17 CE02: o = 80100000h l = 00f000000h /* external memory */ 18 } 19 20 SECTIONS 21 { 22 .cinit > L2 /*初始化变量和常数表*/ 23 .text > L2 /*可执行代码段的映射*/ 24 .stack > L2 /*为系统堆栈分配存储器。该段用于将变量传递至函数或者用来分配局部变量*/ 25 .bss > L2 /*保留全局和静态变量空间。在启动和导入的时候,C/C++编译器会 26 会启动程序将.cint段中的数据复制出来,以初始化.bss段中的变量*/ 27 .const > L2 /*包含由C/C++限定词const定义的字符常量和数据*/ 28 .data > L2 /*初始化数据段*/ 29 .far > L2 /*供外部文件调用的变量*/ 30 .switch > L2 /*控制语句段映射*/ 31 .sysmem > L2 /*初始化系统空间*/ 32 .tables > L2 /*初始化数据表*/ 33 .cio > L2 /*io口*/ 34 .capChaAYSpace> CE01 35 .capChaACbSpace> CE01 36 /* .capChaACbSpace> L2*/ 37 /* .capChaACrSpace> L2*/ 38 .capChaACrSpace> CE01 39 .disChaAYSpace> CE02 40 .disChaACbSpace> CE02 41 .disChaACrSpace> CE02 42 .external > CE02 /*外部变量的初始化*/ 43 }

这个配置应该是没有问题的,接下来我查看了工程里面的GEL文件,文件内容如下:

1 /*--------------------------------------------------------------*/ 2 /* EVMDM642.gel */ 3 /* Version 1.70 */ 4 /* */ 5 /* This GEL file is designed to be used in conjunction with */ 6 /* CCS 2.20.18 and the TMS320DM642 based EVM. */ 7 /* */ 8 /*--------------------------------------------------------------*/ 9 10 /*--------------------------------------------------------------*/ 11 /* The StartUp() function is called each time CCS is started. */ 12 /* Customize this function to perform desired initialization. */ 13 /*--------------------------------------------------------------*/ 14 15 StartUp() 16 { 17 setup_memory_map(); 18 GEL_Reset(); 19 init_emif(); 20 } 21 22 /*--------------------------------------------------------------*/ 23 /* Setup memory map for DM642 EVM. */ 24 /* */ 25 /*--------------------------------------------------------------*/ 26 setup_memory_map() 27 { 28 29 GEL_MapOn(); 30 GEL_MapReset(); 31 32 /* On-chip memory map */ 33 GEL_MapAdd(0x00000000, 0, 0x00040000, 1, 1); /* Internal Memory */ 34 GEL_MapAdd(0x01800000, 0, 0x00000058, 1, 1); /* EMIFA CTL REGS */ 35 GEL_MapAdd(0x01840000, 0, 0x000082FC, 1, 1); /* INT MEM CTL REGS */ 36 GEL_MapAdd(0x018C0000, 0, 0x0000003C, 1, 1); /* MCBSP0 CTL REGS */ 37 GEL_MapAdd(0x01900000, 0, 0x0000003C, 1, 1); /* MCBSP1 CTL REGS */ 38 GEL_MapAdd(0x01940000, 0, 0x00000008, 1, 1); /* TIMER0 CTL REGS */ 39 GEL_MapAdd(0x01980000, 0, 0x00000008, 1, 1); /* TIMER1 CTL REGS */ 40 GEL_MapAdd(0x019C0000, 0, 0x00000008, 1, 1); /* INT CTL REGS */ 41 GEL_MapAdd(0x01A00000, 0, 0x0000FFFC, 1, 1); /* EDMA REGS AND PARAM */ 42 GEL_MapAdd(0x01A40000, 0, 0x0000003C, 1, 1); /* MCBSP2 CTL REGS */ 43 GEL_MapAdd(0x01A80000, 0, 0x00000058, 1, 1); /* EMIFB CTL REGS */ 44 GEL_MapAdd(0x01AC0000, 0, 0x00000008, 1, 1); /* TIMER2 CTL REGS */ 45 GEL_MapAdd(0x01B00000, 0, 0x00000024, 1, 1); /* GPIO REGS */ 46 GEL_MapAdd(0x01B3F000, 0, 0x00000020, 1, 1); /* Device Configuration */ 47 GEL_MapAdd(0x01B40000, 0, 0x0000003C, 1, 1); /* I2C CTL REGS */ 48 GEL_MapAdd(0x01B4C000, 0, 0x000002A0, 1, 1); /* McASP0 CTL REGS */ 49 GEL_MapAdd(0x01C00000, 0, 0x00000028, 1, 1); /* PCI CTL REGS */ 50 GEL_MapAdd(0x01C20000, 0, 0x0000000C, 1, 1); /* PCI EEPROM REGS */ 51 GEL_MapAdd(0x01C40000, 0, 0x00000270, 1, 1); /* VP0 Control */ 52 GEL_MapAdd(0x01C44000, 0, 0x00000270, 1, 1); /* VP1 Control */ 53 GEL_MapAdd(0x01C48000, 0, 0x00000270, 1, 1); /* VP2 Control */ 54 GEL_MapAdd(0x01C80000, 0, 0x00000680, 1, 1); /* EMAC CTL REGS */ 55 GEL_MapAdd(0x01C81000, 0, 0x00002000, 1, 1); /* EMAC Wrapper */ 56 GEL_MapAdd(0x01C83000, 0, 0x0000000C, 1, 1); /* EWRAP REGS */ 57 GEL_MapAdd(0x01C83800, 0, 0x00000090, 1, 1); /* MDIO CTL REGS */ 58 GEL_MapAdd(0x02000000, 0, 0x00000030, 1, 1); /* QDMA REGS */ 59 GEL_MapAdd(0x30000000, 0, 0x04000000, 1, 1); /* MCBSP0 Data, EDMA map */ 60 GEL_MapAdd(0x34000000, 0, 0x04000000, 1, 1); /* MCBSP1 Data, EDMA map */ 61 GEL_MapAdd(0x74000000, 0, 0x02000000, 1, 1); /* VP0 Channel A Data */ 62 GEL_MapAdd(0x76000000, 0, 0x02000000, 1, 1); /* VP0 Channel B Data */ 63 GEL_MapAdd(0x78000000, 0, 0x02000000, 1, 1); /* VP1 Channel A Data */ 64 GEL_MapAdd(0x7A000000, 0, 0x02000000, 1, 1); /* VP1 Channel B Data */ 65 GEL_MapAdd(0x7C000000, 0, 0x02000000, 1, 1); /* VP2 Channel A Data */ 66 GEL_MapAdd(0x7E000000, 0, 0x02000000, 1, 1); /* VP2 Channel B Data */ 67 68 /* Off-chip memory map */ 69 GEL_MapAdd(0x80000000, 0, 0x02000000, 1, 1); /* 32MB SDRAM EMIF-A, CE0*/ 70 GEL_MapAdd(0x90000000, 0, 0x00080000, 1, 1); /* 4MB Flash EMIF-A, CE1 */ 71 GEL_MapAdd(0x90080000, 0, 0x00080000, 1, 1); /* 4MB FPGA EMIF-A, CE1 */ 72 GEL_MapAdd(0xA0000000, 0, 0x10000000, 1, 1); /* EMIF-A, CE2 EXPANSION */ 73 GEL_MapAdd(0xB0000000, 0, 0x10000000, 1, 1); /* EMIF-A, CE3 EXPANSION */ 74 } 75 76 /*--------------------------------------------------------------*/ 77 /* init_emif() */ 78 /*--------------------------------------------------------------*/ 79 init_emif() 80 { 81 82 #define EMIFA_GCTL 0x01800000 83 #define EMIFA_CE1 0x01800004 84 #define EMIFA_CE0 0x01800008 85 #define EMIFA_CE2 0x01800010 86 #define EMIFA_CE3 0x01800014 87 #define EMIFA_SDRAMCTL 0x01800018 88 #define EMIFA_SDRAMTIM 0x0180001c 89 #define EMIFA_SDRAMEXT 0x01800020 90 #define EMIFA_CE1SECCTL 0x01800044 91 #define EMIFA_CE0SECCTL 0x01800048 92 #define EMIFA_CE2SECCTL 0x01800050 93 #define EMIFA_CE3SECCTL 0x01800054 94 95 /* EMIFA */ 96 *(int *)EMIFA_GCTL = 0x00052078; 97 *(int *)EMIFA_CE0 = 0xffffffd3; /* CE0 SDRAM */ 98 *(int *)EMIFA_CE1 = 0x73a28e01; /* CE1 Flash + CPLD */ 99 *(int *)EMIFA_CE2 = 0x22a28a22; /* CE2 Daughtercard 32-bit async */ 100 *(int *)EMIFA_CE3 = 0x22a28a42; /* CE3 Daughtercard 32-bit sync */ 101 *(int *)EMIFA_SDRAMCTL = 0x57115000; /* SDRAM control */ 102 *(int *)EMIFA_SDRAMTIM = 0x0000081b; /* SDRAM timing (refresh) */ 103 *(int *)EMIFA_SDRAMEXT = 0x001faf4d; /* SDRAM extended control */ 104 *(int *)EMIFA_CE0SECCTL= 0x00000002; /* CE0 Secondary Control Reg. */ 105 *(int *)EMIFA_CE1SECCTL= 0x00000002; /* CE1 Secondary Control Reg. */ 106 *(int *)EMIFA_CE2SECCTL= 0x00000002; /* CE2 Secondary Control Reg. */ 107 *(int *)EMIFA_CE3SECCTL= 0x00000073; /* CE3 Secondary Control Reg. */ 108 } 109 110 /*--------------------------------------------------------------*/ 111 /* clear_memory_map() */ 112 /*--------------------------------------------------------------*/ 113 clear_memory_map() 114 { 115 GEL_MapOff(); 116 } 117 118 /*--------------------------------------------------------------*/ 119 /* FlushCache() */ 120 /*--------------------------------------------------------------*/ 121 FlushCache() 122 { 123 /* Invalidate L1I and L1D */ 124 *(int *)0x01840000 = (*(int *)0x01840000 | 0x00000300); 125 126 /* Clean L2 */ 127 *(int *)0x01845004 = 0x1; 128 } 129 130 131 /*--------------------------------------------------------------*/ 132 /* OnReset() */ 133 /*--------------------------------------------------------------*/ 134 OnReset(int nErrorCode) 135 { 136 init_emif(); 137 } 138 139 140 /*--------------------------------------------------------------*/ 141 /* OnPreFileLoaded() */ 142 /* This function is called automatically when the 'Load Program'*/ 143 /* Menu item is selected. */ 144 /*--------------------------------------------------------------*/ 145 OnPreFileLoaded() 146 { 147 /* GEL_Reset(); -- Commented out for CCS 2.20 */ 148 FlushCache(); 149 IER = 0; 150 IFR = 0; 151 init_emif(); 152 } 153 154 /*--------------------------------------------------------------*/ 155 /* OnRestart() */ 156 /* This function is called by CCS when you do Debug->Restart. */ 157 /* The goal is to put the C6x into a known good state with */ 158 /* respect to cache, edma and interrupts. */ 159 /* Failure to do this can cause problems when you restart and */ 160 /* run your application code multiple times. This is different */ 161 /* then OnPreFileLoaded() which will do a GEL_Reset() to get the*/ 162 /* C6x into a known good state. */ 163 /*--------------------------------------------------------------*/ 164 OnRestart(int nErrorCode ) 165 { 166 /* Turn off L2 for all EMIFA CE spaces. App should 167 * manage these for coherancy in the application. 168 * GEL_TextOut("Turn off cache segment "); 169 */ 170 *(int *)0x1848200 = 0; /* MAR0 */ 171 *(int *)0x1848204 = 0; /* MAR1 */ 172 *(int *)0x1848208 = 0; /* MAR2 */ 173 *(int *)0x184820c = 0; /* MAR3 */ 174 175 /* Disable EDMA events and interrupts and clear any 176 * pending events. 177 * GEL_TextOut("Disable EDMA event "); 178 */ 179 *(int *)0x01A0FFA8 = 0; /* CIERH */ 180 *(int *)0x01A0FFB4 = 0; /* EERH */ 181 *(int *)0x01A0FFB8 = 0XFFFFFFFF; /* ECRH */ 182 183 *(int *)0x01A0FFE8 = 0; /* CIERL */ 184 *(int *)0x01A0FFF4 = 0; /* EERL */ 185 *(int *)0x01A0FFF8 = 0xFFFFFFFF; /* ECRL */ 186 187 /* Disable other interrupts */ 188 IER = 0; 189 IFR = 0; 190 } 191 192 /*--------------------------------------------------------------*/ 193 /* RESET MENU */ 194 /*--------------------------------------------------------------*/ 195 menuitem "Resets"; 196 197 hotmenu Reset_BreakPts_and_EMIF() 198 { 199 GEL_BreakPtReset(); 200 GEL_Reset(); 201 init_emif(); 202 } 203 204 hotmenu Flush_Cache() 205 { 206 FlushCache(); 207 } 208 209 /*--------------------------------------------------------------*/ 210 /* MEMORY MAP MENU */ 211 /*--------------------------------------------------------------*/ 212 menuitem "Memory Map"; 213 214 hotmenu SetMemoryMap() 215 { 216 setup_memory_map(); 217 } 218 219 hotmenu ClearMemoryMap() 220 { 221 clear_memory_map(); 222 } 223 224 /*--------------------------------------------------------------*/ 225 /* BOARD OPTIONS MENU */ 226 /*--------------------------------------------------------------*/ 227 menuitem "Board Options"; 228 229 #define CPLD_REVISION 0x9008001F 230 231 hotmenu CheckFPGARevision() 232 { 233 GEL_TextOut(" FPGA Revision %d ","Output",1,1,1, *(char *)CPLD_REVISION); 234 GEL_TextOut(" Note: Revision only valid if FGPA DONE LED is on (DS9) ","Output",1,1,1); 235 }

我的硬件的配置时 CCS3.3+SEED-DKT-VPM642+SEED-XDS560PLUS Emulator

下面是工程run过程的Message:

解决办法:

已经解决了:问题如下

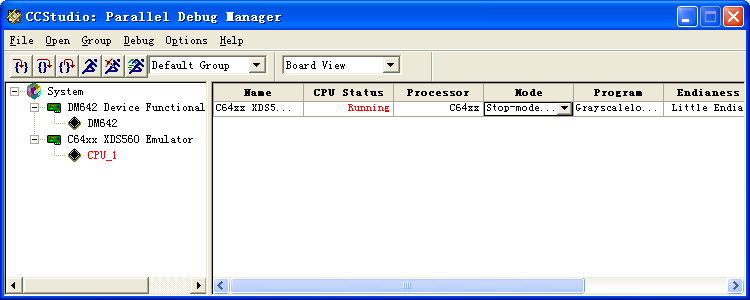

1.我在CCS3.3启动的Parallel Debug Manager里面选择出了问题:

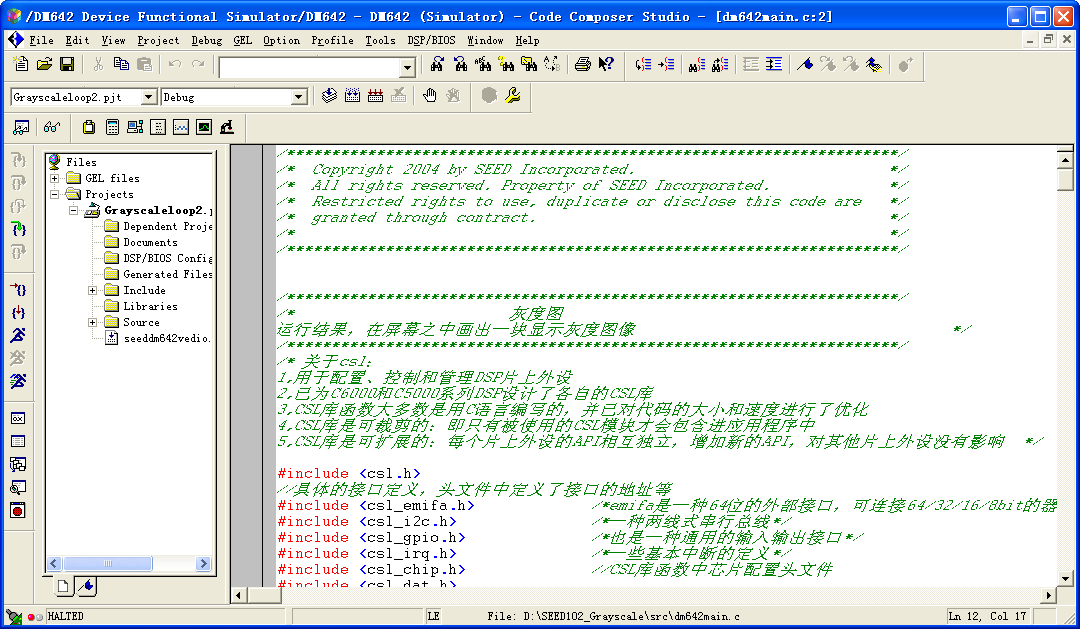

在这里我们需要选择的是C64xx XDS560 Emulator所连接的CPU_1,而不是上面的DM642 Device Functional Simulator 所连接的DM642的 模拟核,当我选择第一个Simulator的选项并打开导入工程之后建立的就是DM642的软件仿真程序而不是硬件仿真!(这个状态我们也很清楚的在CCS3.3的最上面的图表中看到为:DM642 Device Functional Simulator。所以这也是我还未能很好的使用CCS这款软件导致的。)

当我们点击编译Compile+建立Build+加载load Program+Run时出现的错误,程序被加载到了虚拟核中,但是在虚拟核上仿真DM642并不支持,所以就会出现上面的错误!

2.当我弄清楚这个问题之后,我打开了下面的Emulator的CPU_1的工程,按步骤加载并运行了程序,发现还是没能在显示器上得到我要的视频数据,后面检查了半天发现是BNC的视频输出线存在接触不良的情况导致的~(真是机缘巧合找到的原因,所以说大家也要多多注意这种硬件的问题吧!)