FPGA逻辑代码重要的是理解其中的时序逻辑,延时与各种时间的记忆也是一件头疼的事,这里把我最近看到的比较简单的几类总结起来,共同学习。

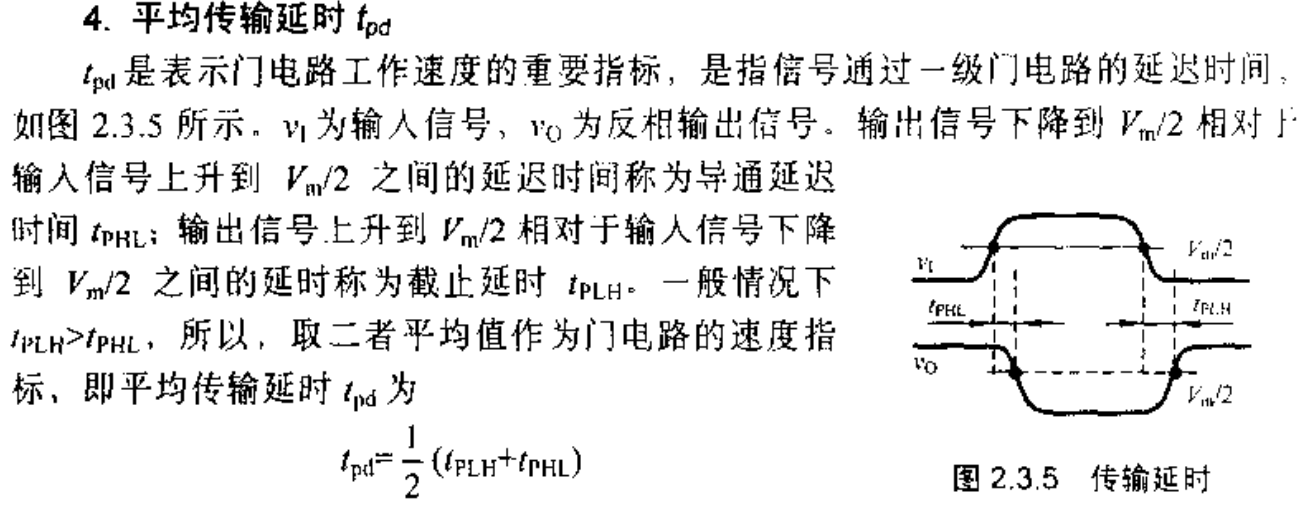

一、平均传输延时

平均传输延时

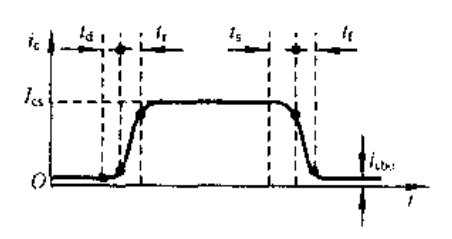

二、开启时间与关闭时间

开启时间与关闭时间

三极管Td 延迟时间 Tr上升时间 合称开启时间

三极管Ts存储时间 Tf下降时间 合称关闭时间

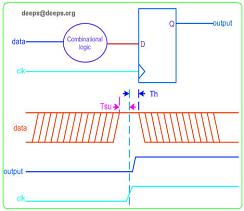

三、触发器建立时间与保持时间

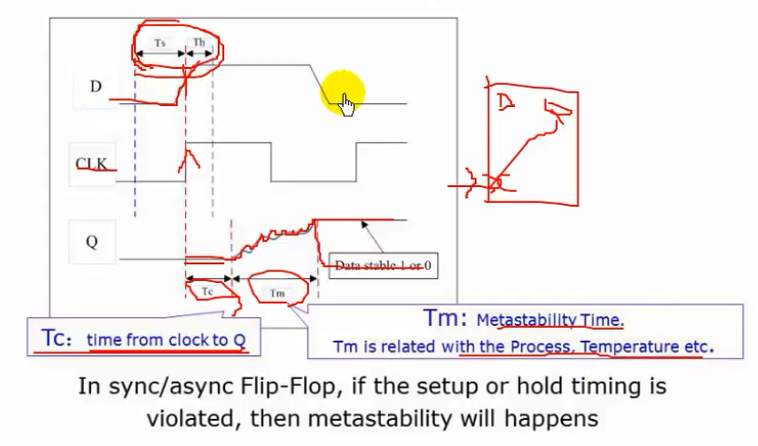

建立时间(Tsu:set up time)是指在时钟沿到来之前数据从不稳定到稳定所需的时间,如果建立的时间不满足要求那么数据将不能在这个时钟上升沿被稳定的打入触发器;保持时间(Th:hold time)是指时钟信号到来之后数据稳定保持的时间,如果保持时间不满足要求那么数据同样也不能被稳定的打入触发器。

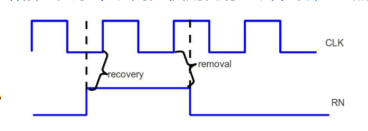

四、锁存器 恢复时间和移除时间

在时钟沿到来之前的 recovery time 之前,异步信号必须释放 (变无效),在时钟沿到来之后的 removal time 之后,异步信号才能变有效,也就是说在从 recovery time 到 removal time 这段时间内,异步信号是不能有效的。异步信号中的recovery time和removal time类似setup 和 hold time,可以考虑为异步复位信号。

输出响应时间(Tco) :触发器输出的响应时间,也就是触发器的输出在clk时钟上升沿到来之后多长的时间内发生变化,也即触发器的输出延时。

五、Tc与Tm

Tc: time from clock to Q

Tc: time from clock to Q

Tm: Metastability Time