继上面介绍了setup文件的基本书写,简单介绍下时钟设置及简单地时序,面积,PVT设置约束。

DC的约束是基于路径的,这里所谓的路径起点是input port 或者clock port of flip-flop或者纯组合逻辑的寄存器输入,终点是output port或者任意时序逻辑的输入.

时钟:

虽然DC无法最终综合时钟树,但是我们可以加入一些约束让此时的时钟更加接近实际的工作情况。可以通过create_clock –period 10 [get_ports clk1]建立时钟,这句话意思是建立一个名为clk周期为10单位的时钟,这里的单位一般是ns,可以通过list_lib查看。这句命令默认占空比50%。如想设置其他占空比为 create_clock –period 10 –waveform {0 3} [get_prots clk2].这行命令设置占空比为3:7(第一个为上升沿时间,第二个为下降沿时间)。另外由于pre-layout时得不到准确的时钟参数,所以此时不对clocks进行综合,因此用命令set_dont_touch_network [get_ports clk1] 实现上述要求(且默认此时clock为ideal ,驱动能力无限大 无上升沿下降沿。下面会进行一定的预估值)。也可以在以后得对ports命令中set_input_delay 0.1 -max -clock Clk [remove_from_collection [all_inputs] [get_ports Clk]] 进行设置。

set_clock_latency #模拟clk到寄存器的延迟 network latency

set_clock_latency -source #模拟晶振到clk port的延迟 source latency

set_clock_transition #将ideal时钟模拟成有一定斜率的上升沿下降沿时钟。

set_clock_uncertainty –setup Tu [get_ports clk] #模拟时钟偏差(Clock Skew)时钟到各个触发器的时间不是一样的 Tu包括skew jitter margin

//以上两组数据,可咨询板级工程师和APR工程师。

如果已经从后端CTS的获取了准确的时钟树参数,那么可以用set_propagated_clock clk1,此时source latency还是依旧要有的。

以上的命令均是单时钟单沿触发。特殊情况还有同步多时钟、异步多时钟、多周期路径。

当纯组合逻辑时就要设置虚拟时钟,

create_clock –name clk2 –period 10

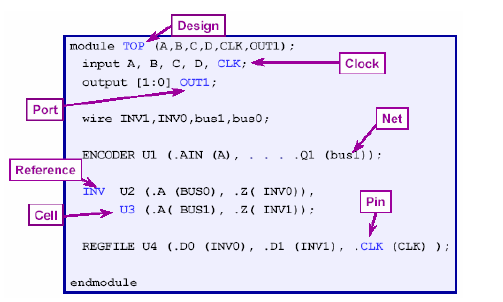

上面所说的port为DC中六大object之一,design、clock、port、cell、pin、net。

Design:设计名称,理解为***.v中的***;

Clock:时钟;

Port:design的input,output;

Cell:design中调用的模块或低一层design;

Pin:例化cell的输入输出

Net:cell间内部互联线

//从上面描述可知 design和cell有时候可以相互转换。

输入驱动:

如果不对工程进行输入驱动,DC默认无穷大即,translation time为0。

set_driving_cell –lib_cell inv1 [get_ports A] #这句命令是将port A的输入驱动模拟成cell FD1的Q脚连接。

set_driving_cell –lib_cell FD1 –pin Q [get_ports B]#这句命令是将port B的输入驱动模拟成cell FD1的Q脚连接。这句话对比上面那句是因为FD1除了Q还有一个Q’的输出。要固定其哪一个输出模拟接到B。

set_driving_cell -library $lib_name -lib_cell inv1 [all_inputs] #此命令是让所有input的输入驱动为前面所定义的lib_name中的inv1 cell。

set_driving_cell [expr [load_of $lib_name/an02d0/A1] * 15] [all_inputs] #均是假想一个驱动单元在输入端口之前,据此单元计算。

输出负载:

默认为0,但是太过于乐观。同样如果设置太大又会增加translation time进而影响性能。

Set_load 5 [get_ports OUT1] #设置OUT1为5pf,输出负载默认为pf也可report_lib查看单位

set_load [load lib_name/ an01d0/A1] [get_ports OUT2]

set_load [expr [load_of $lib_name/an01d0/A1] * 15] [get_ports OUT3] #这个是使OUT3输出负载为定义的lib_name中an01d0的A1脚的负载电容15倍。

此处提一下,如果先后两次对一个端口进行约束,那么最终保存的是最后一次的约束。

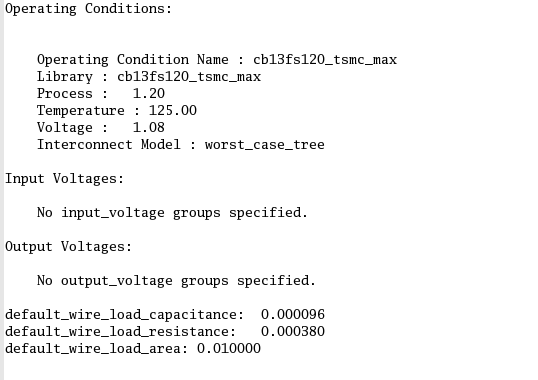

PVT设置

工艺、电压、温度。这些情况一般只考虑最差ss和最好ff。只考虑setup可以测ss,只考虑hold 可以测ff。如果setup文件只读入了一个target_library那么只有一个工作条件,可以不用做这一步。如果读入多个仍需设置。

Set_operating_conditions –max “ ss***”/

-min “fast***”

线负载模型

set_wire_losd_model #跟工艺厂多沟通获取具体值

以上设置完成后,可以用check_timing check_design 等语言查看。