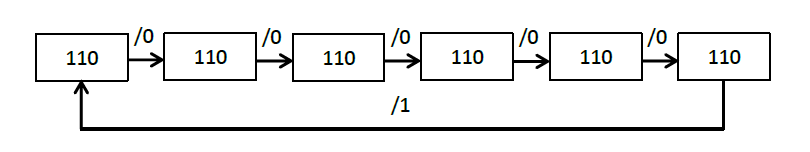

基于触发器的三位二进制同步减法计数器无效态000/110

1 课程设计的目的与作用

掌握用multisim 的电路仿真程序

熟悉同步计数器工作原理和逻辑功能

熟悉计数器电路的分析和设计方法

掌握161 芯片集联成任意进制同步加法计数器

2 设计任务

三位二进制减法计数器(无效态: 000 011)

3设计过程

三位二进制减法计数器(无效态: 000 011)

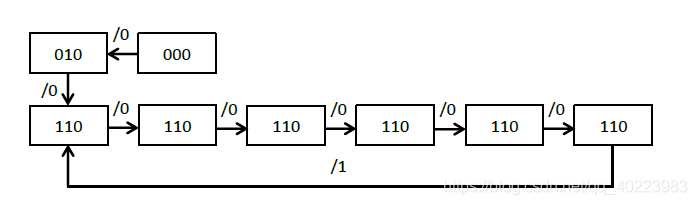

3.1 状态转换图

3.2 求时钟方程

CP0 =CP 1 =CP 2 =CP

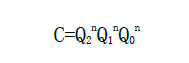

3.3 求输出方程

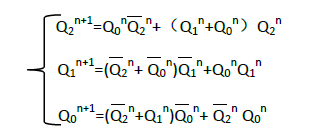

3.4 求状态方程

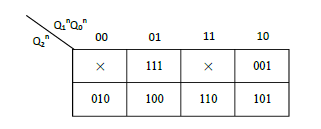

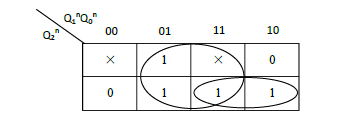

三位二进制同步加法计数器次态的卡诺图

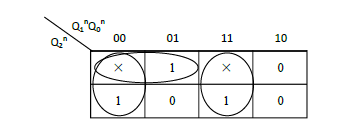

Q 2 n+1 的卡诺图

Q 1 n+1 的卡诺图

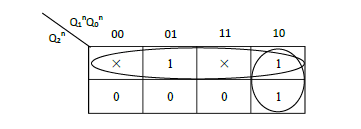

Q 0 n+1 的卡诺图

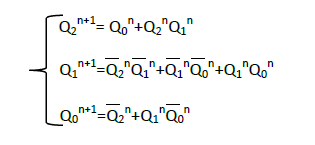

根据卡诺图得到次态方程

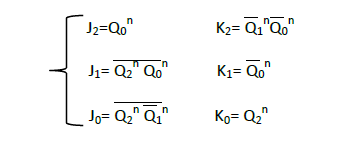

3.5 求驱动方程

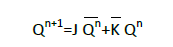

JK触发器的特性方程为

变换状态方程的形式:

根据上式,即可得下列驱动方程:

3.6 自启动验证及检验

该逻辑电路能够自启动

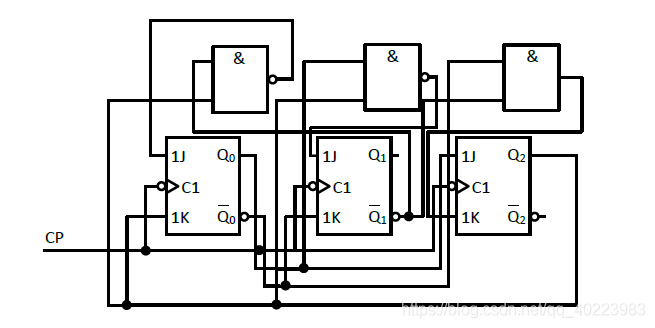

3.7 画逻辑电路图

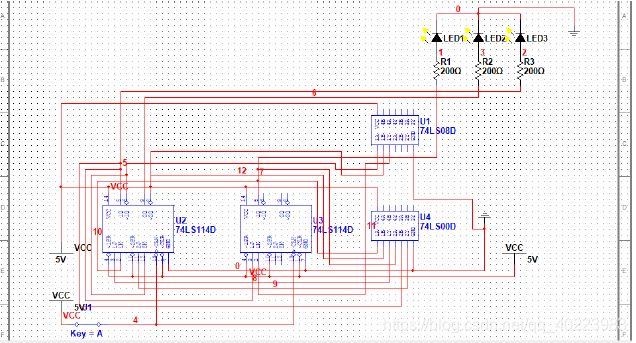

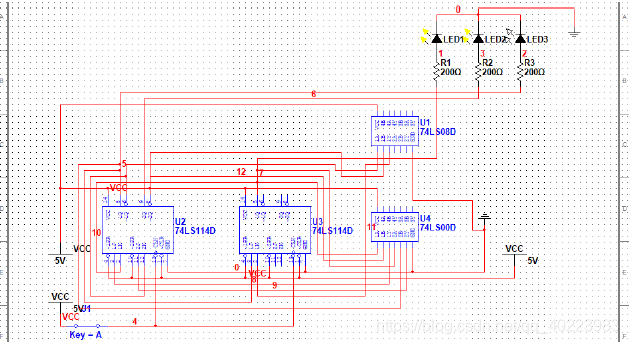

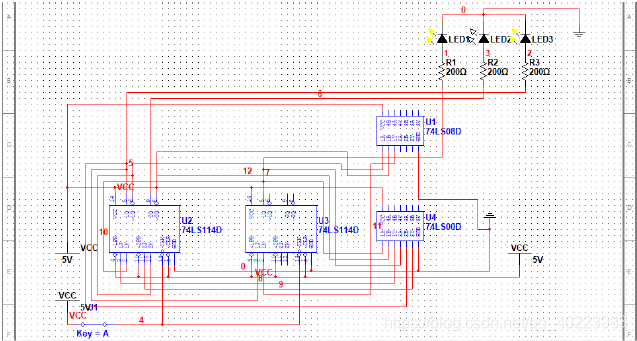

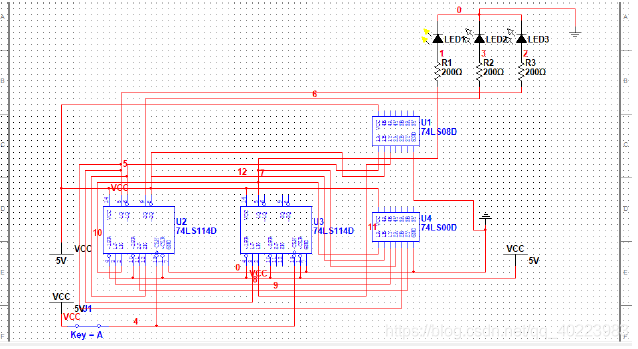

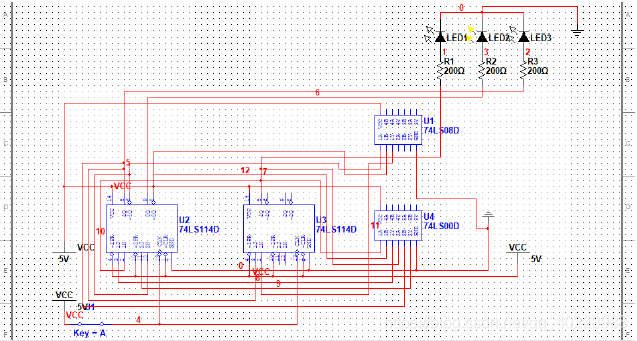

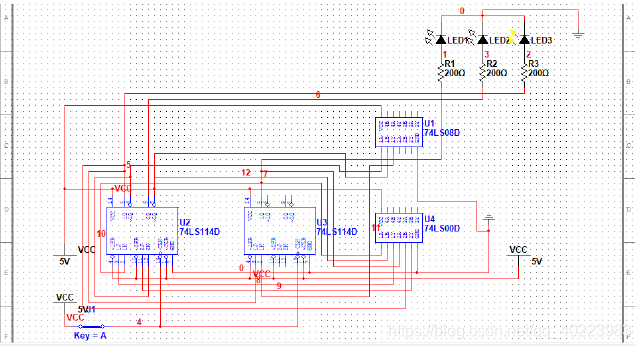

4 仿真结果分析

4.1 三位二进制减法计数器(无效态: 000 011)

三位二进制减法计数器(状态: 111)

三位二进制减法计数器(状态: 110)

三位二进制减法计数器(状态: 101)

三位二进制减法计数器(状态: 100)

三位二进制减法计数器(状态: 010)

三位二进制减法计数器(状态: 001)

5 设计总结

通过这次数次电路课程设计的学习与实践,我初步了解简单数字电路设计过程以及仿真应用,熟悉了以 multisim 为软件载体的数字电路仿真。其次,锻炼了我的科学探索精神。在这次课设中,我尝试了不同的设计思路,把所学的知识结合在一起,仿真出自己设计的电路。当然,在不断尝试的过程中,也遇到了不少的问题,独立思考是必不可少的,同时借鉴网上,书本等材料以及和同学讨论也是不可或缺的,也这次的课程设计,也培养了我的科学素养。

针对课题,是简单的三位二进制加减法计数器的设计,我了解了最基本的数字电路的设计过程,解决简单的时序问题。熟悉了通过卡诺图,用简单的触发器,设计逻辑电路的过程。

同时掌握了 根据自己通过理论设计出来的数字电路,用 multisim 仿真验证自己的电路 。 Multisim 这个软件中的器件很齐全,而我只是简单的了解,应用了其中的一些元器件。相信在以后的学习过程中,我能更加的熟悉 multisim 这个软件的应用。

最后,我相信这次的课程设计不会是我学习数字电路的结束,而是我学习数字电路的开始,我将会用这次学到的知识,用在以后的 设计逻辑电路中。

6 参考文献

[1]清华大学电子教研组 编 . 余孟尝 主编 . 数字电子技术基础简明教程 第三

版 [M]. 北京:高等教育出版社, 2006

[2]信息学院数字逻辑实验室 编 . 张利萍 张群芳 主编 . 数字逻辑实验指导书

[M]. 沈阳理工大学