1 绪论

1.1 设计背景

集成电路设计(Integrated circuit design, IC design),亦可称之为超大规模集成电路设计(VLSI design),是指以集成电路、超大规模集成电路为目标的设计流程。集成电路设计涉及对电子器件(例如晶体管、电阻器、电容器等)、器件间互连线模型的建立。所有的器件和互连线都需安置在一块半导体衬底材料之上,这些组件通过半导体器件制造工艺(例如光刻等)安置在单一的硅衬底上,从而形成电路。

近些年来,集成电路技术发展迅猛,促使半导体技术不断地发展,半导体技术正在进入将整个系统整合在单一晶片上的时代。故对VLSI的版图设计的要求也越来越高。Tanner软件可提供完整的集成电路设计环境,帮助初学者进入VLSI设计领域。本设计采用Tanner Tools Pro 工具,对逻辑为Y=AB+C进行电路设计与仿真、版图设计与仿真,在报告中给出电路图、版图与仿真结果。

1.2 设计目标

设计目标逻辑:Y=AB+C

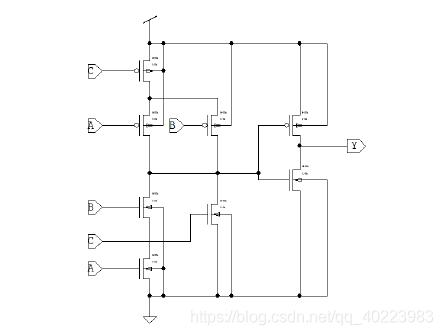

用CMOS工艺设计逻辑为Y=AB+C的电路和版图。因为CMOS是天然的反逻辑输出,所以需要先设计出逻辑为/Y=/(AB+C)的电路,再将输出接入一个CMOS反相器实现逻辑功能。

设计电路图(Schematic)时,N网络A与B串联且与C并联,P网络A与B并联且与C串联,在N和P网络的交界节点接入反相器后引出输出Y。

设计版图(Layout)时,在P型衬底(P-Sub)上进行制作,所以N-MOS管可以直接掺杂制作,而P-MOS管需要先制作一个N阱(N-Well),并在N阱里制作P-MOS管。整个设计比较简单,仅仅使用单层金属布线(Meteal)。

导出电路和版图网表(spice)文件,用Tspice软件进行仿真波形,分析电路和版图是否设计正确性以及其性能如何。在LVS验证中匹配电路原理图和版图逻辑和尺寸匹配性,完成整个设计过程。

2 Y=AB+C 的电路原理图设计与仿真

2.1 电路原理图设计

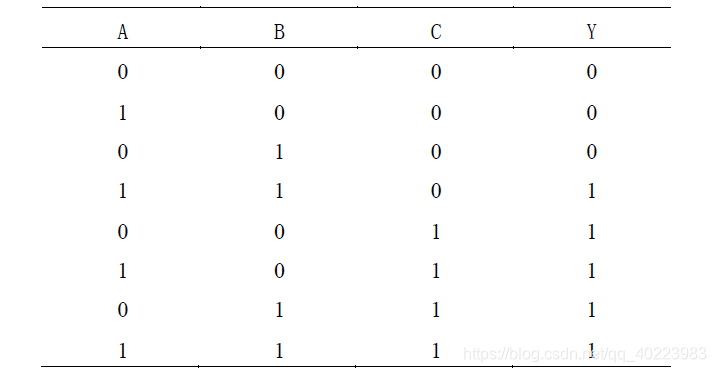

目标逻辑Y=AB+C,设计电路其功能为当C=1时,Y=1;当C=0而B和C不同时为1时,Y=0;当C=0,A和B都为1时,Y=1。

以上电路功能符合设计的目标逻辑Y=AB+C,所以此电路图(Schematic)设计正确,下面给出其真值表,如下表所示:

使用S-Edit软件进行电路图(Schematic)绘制,在Schematic Model下绘制电路图(Schematic),首先从Symbol Browser中导出N-MOS管和P-MOS管,然后绘制InputPort和OutPort,最后通过Wire线进行连接,如下图所示;

2.2 电路仿真

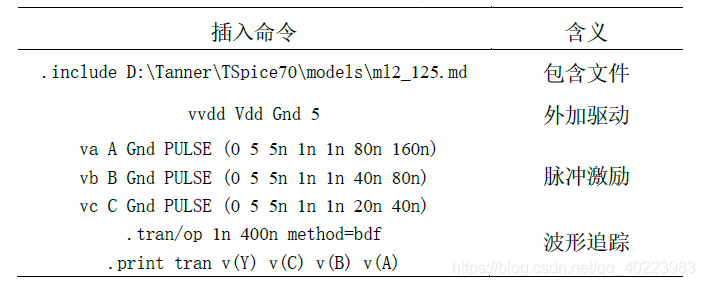

通过以上电路原理图(Schematic)和符号图的绘制,导出spice网表,用Tspice软件进行仿真波形,分析电路是否设计正确性以及其性能如何。

仿真需要在spice网表中添加额外的命令来完成仿真,需要添加包含文件(Include file)、外加电压(Constant Voltage source)、外加脉冲激励(Pulse Voltage source)、波形追踪(.tran)和打印波形(.print)命令。以下给出这些命令,如下表所示:

插入命令 含义

.include D:TannerTSpice70modelsml2_125.md 包含文件

vvdd Vdd Gnd 5 外加驱动

va A Gnd PULSE (0 5 5n 1n 1n 80n 160n)

vb B Gnd PULSE (0 5 5n 1n 1n 40n 80n)

vc C Gnd PULSE (0 5 5n 1n 1n 20n 40n) 脉冲激励

.tran/op 1n 400n method=bdf

.print tran v(Y) v© v(B) v(A) 波形追踪

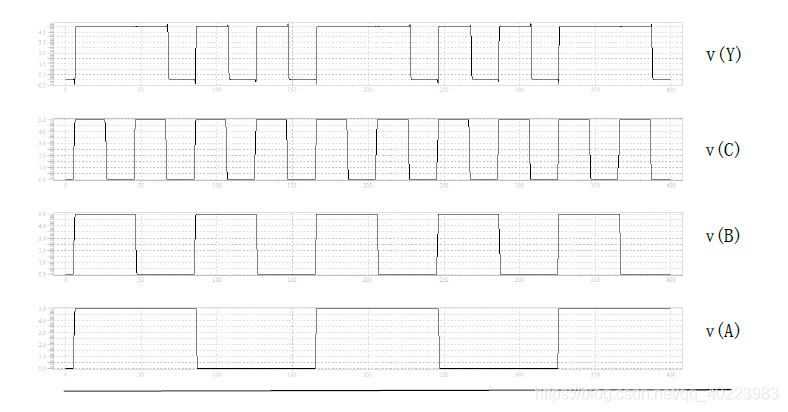

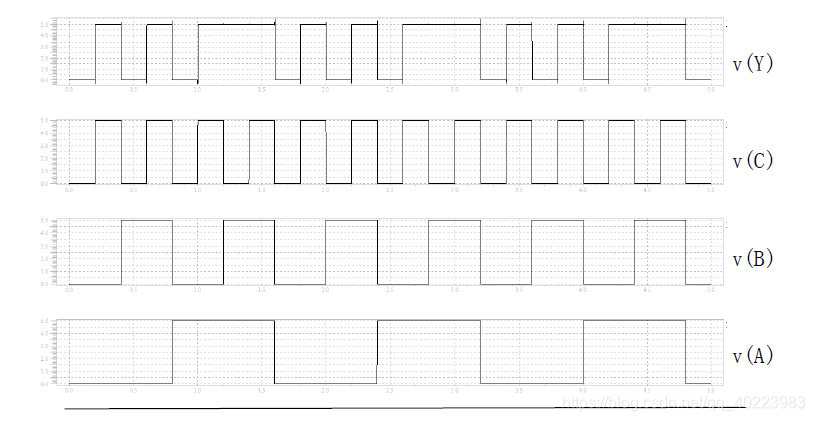

下面给出电路原理图的仿真波形结果图,如下图所示:

输入激励以C的周期为基础,B翻一倍,A翻两倍,这样做可以将所有情况遍历出来,进而可以和真值表进行对比验证其准确性。

3 Y=AB+C的版图设计与仿真

3.1 版图设计

首先需要先制作一个N阱(N-Well),并在N阱里制作P-MOS管,由于在P型衬底(P-Sub)上进行制作,所以N-MOS管可以直接掺杂制作。整个设计比较简单,仅仅使用单层金属布线(Meteal)即可实现。

首先导入设计规则(lights.ext)文件,绘制两个有源区为PN网络,再绘制栅极横跨上下两个有源区,然后依照电路原理图合理分配源漏区,绘制有源区接触孔(Active Contact)并连线,再绘制衬底区,使用P-Select和N-Select、N-Well遮罩有源区,最后绘制端口(Port),每一步进行DRC电气规则检查从而保证当前设计符合设计和生产规则。

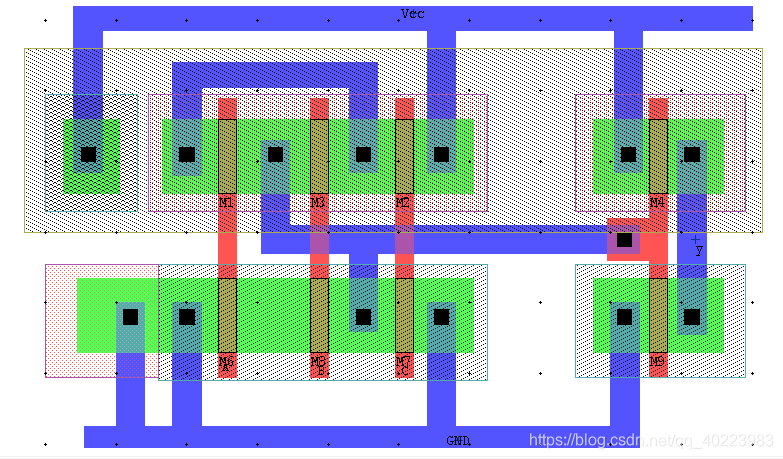

下面给出版图设计,如下图所示:

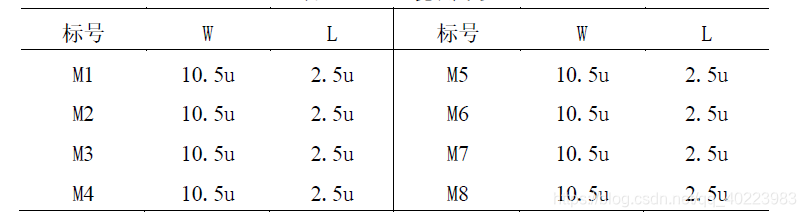

其中M1-M8管的宽和长(W和L),如下表所示:

3.2 DRC检查

DRC检查,即设计规则检查,是在进行版图设计中必要的一步,通过带有可选参数的DRC检查,可以保证设计尺寸和布局的准确性。

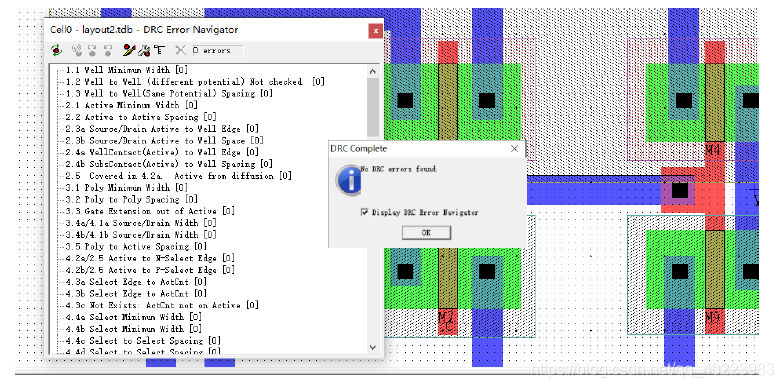

在进行DRC检查之前需要导入设计规则MOSIS/ORBIT 2.0U SCNA Design Rules,在绘制过程中需要不断进行检查,若有错误可以及时的修改更正。下面给出本设计的DRC检查结果,如下图所示:

经过检查,本设计版图符合设计规则,能够用于生产。图3.2图中的DRC Error Navigator窗口为DRC检查的内容,每一项都需要符合设计规则。

3.3 版图仿真

在绘制完版图后,可以导出spice网表,用Tspice软件进行仿真波形,来分析版图是否设计正确以及其性能如何。

导出spice网表需要在添加支持文件下进行,Import Mask Data选项下导入lights.ext文件。

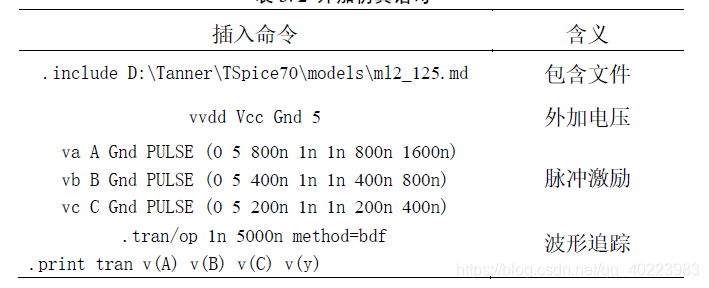

仿真需要在spice网表中添加额外的命令来完成仿真,需要添加的命令如电路导出的spice网表一样包括包含文件(Include file)、外加电压(Constant Voltage source)、外加脉冲激励(Pulse Voltage source)、波形追踪(.tran)和打印波形(.print)命令。以下给出这些命令,如表所示:

插入命令 含义

.include D:TannerTSpice70modelsml2_125.md 包含文件

vvdd Vcc Gnd 5 外加电压

va A Gnd PULSE (0 5 800n 1n 1n 800n 1600n)

vb B Gnd PULSE (0 5 400n 1n 1n 400n 800n)

vc C Gnd PULSE (0 5 200n 1n 1n 200n 400n) 脉冲激励

.tran/op 1n 5000n method=bdf

.print tran v(A) v(B) v© v(y) 波形追踪

在Tspice软件中打开版图中导出的spc网表文件,加入上述激励命令,再进行波形的仿真,如图所示:

通过版图仿真出来的波形,再结合之前生成的电路图仿真的波形以及电路原理图和真值表,能够验证版图绘制过程中的正确性。因为输入信号只有三个,所以可以将输入激励以C的周期为基础,B增加一倍,A增加两倍,这样做的好处是能够将所有的输入情况进行遍历,可以完整的检验设计逻辑的正确性。

由给出的激励如va A Gnd PULSE (0 5 800n 1n 1n 800n 1600n)可知A输入信号激励初始为0电平,其峰值为5V,初始电平延时时间为800ns,电平上升和下降时间为1ns,峰值保持时间为800ns,周期为1600ns可知,该输入信号频率较低,从而保证输出的波形十分规整,无明显的毛刺现象。

4 版图与电路图验证

将版图和电路图直接进行对比验证,可以很直接的判断设计的统一性,将原理设计和版图设计统一为一个整体,同时,也可以检查出单一设计中的一些问题,比如MOS的宽长比例是否一致,金属孔类型是否正确等。

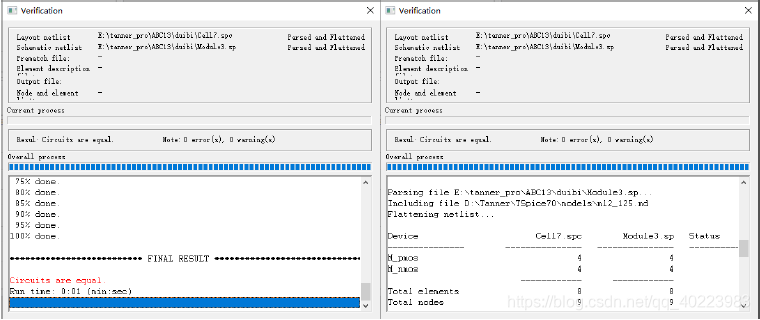

启动LVS软件,新建立一个项目(LVS setup)分别将版图的spc网表和电路图的sp网表文件导入进去,添加包含的文件命令:.include “D:TannerTSpice70modelsml2_125.md”。这里需要注意的是上述仿真添加的激励命令需要注释掉,否则会产生一些不必要的警告,如图所示:

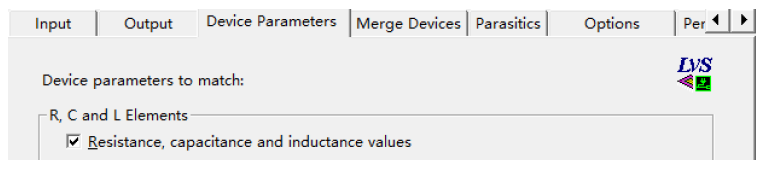

配置LVS对比的的设置,在Output选项卡里勾选Output file和Node and element list并分别添加之前仿真产生的文件,在Device Parameters里勾选R,C and L Elements中唯一的一项Resistance,capacitance and inductance value选项,以上图4.1为LVS配置界面

下面给出LVS对比的结果,如图所示:

通过对比的结果可以看出,电路图和版图的各种参数保持一致,从而再次验证了本次设计的正确性。

5 总结

通过这段时间的课程设计的学习,综合运用所学的知识完成了设计任务。使我更深的的了解版图工艺的艺术,并深入掌握仿真方法和工具Tanner、同时为以后从事本专业工作打下坚实的基础。进一步熟悉设计中使用的主流工具,版图设计属于集成电路的后端设计,通过绘制电路版图,发现了理论与现实有着很大的差别,特别是绘制版图,需要很大的耐心和毅力。由逻辑表达式到电路原理图绘制再到版图的绘制,突破一个个问题然后是成功从设计到实现。

课程设计是一门很严谨的的课程,给了我很多专业知识,同时在一定程度上提高了我的专业技能,还教给我许多的道理。通过课程设计,我不仅学到了知识,而且从中领悟到了一些解决问题的方法,为以后的学习打下了坚实的基础。

参考文献

[1] 姜岩峰编著.现代集成电路版图设计.北京:化学工业出版社,2010

[2] 尹飞飞编著.CMOS模拟集成电路版图设计与验证:基于Cadence Virtuoso与Mentor Calibre. 北京:电子工业出版社,2016

[3] 曾庆贵、姜玉稀编著.集成电路版图设计教程.上海:上海科学技术出版社,2012

附录一:电路原理图网表

* SPICE netlist written by S-Edit Win32 7.03

* Written on Jun 17, 2019 at 20:44:53

* Waveform probing commands

.probe

.options probefilename="E: anner_proABC13dianlutuModule2.dat"

+ probesdbfile="E: anner_proABC13dianlutudemo2.sdb"

+ probetopmodule="Module0"

* Main circuit: Module0

M1 N1 B N4 Gnd NMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u

M2 N1 C Gnd Gnd NMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u

M3 N4 A Gnd Gnd NMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u

M4 Y N1 Gnd Gnd NMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u

M5 N1 A N8 Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u

M6 N1 B N8 Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u

M7 N8 C Vdd Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u

M8 Y N1 Vdd Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u

* End of main circuit: Module0

vvdd Vdd Gnd 5

.tran/op 1n 400n method=bdf

.print tran v(A) v(B) v(C) v(Y)

.include "D: annerTSpice70modelsml2_125.md"

va A Gnd PULSE (0 5 5n 1n 1n 80n 160n)

vb B Gnd PULSE (0 5 5n 1n 1n 40n 80n)

vc C Gnd PULSE (0 5 5n 1n 1n 20n 40n)

附录二:版图网表

* Circuit Extracted by Tanner Research's L-Edit Version 9.00 / Extract Version 9.00 ;

* TDB File: E: anner_proABC13antulayout2.tdb

* Cell: Cell0 Version 1.27

* Extract Definition File:

D:TannerLEdit90SamplesSPRexample1lights.ext

* Extract Date and Time: 06/18/2019 - 13:15

* NODE NAME ALIASES

* 1 = Vcc (642,-1409)

* 3 = Gnd (648.5,-1469.5)

* 5 = y (682,-1441)

* 6 = A (615,-1459.5)

* 7 = C (640.5,-1460)

* 8 = B (628.5,-1460)

M9 y 2 Gnd Gnd NMOS L=2.5u W=10.5u

M8 2 B 9 Gnd NMOS L=2.5u W=10.5u

M7 Gnd C 2 Gnd NMOS L=2.5u W=10.5u

M6 9 A Gnd Gnd NMOS L=2.5u W=10.5u

M4 y 2 Vcc Vcc PMOS L=2.5u W=10.5u

M3 4 B 2 Vcc PMOS L=2.5u W=10.5u

M2 Vcc C 4 Vcc PMOS L=2.5u W=10.5u

M1 2 A 4 Vcc PMOS L=2.5u W=10.5u

* Total Nodes: 9

* Total Elements: 8

* Total Number of Shorted Elements not written to SPICE file: 1

* Extract Elapsed Time: 0 seconds

.END

vvdd Vcc Gnd 5

.tran/op 1n 5000n method=bdf

.print tran v(A) v(B) v(C) v(y)

.include "D:TannerTSpice70modelsml2_125.md"

va A Gnd PULSE (0 5 800n 1n 1n 800n 1600n)

vb B Gnd PULSE (0 5 400n 1n 1n 400n 800n)

vc C Gnd PULSE (0 5 200n 1n 1n 200n 400n)