- Makefile可以使用变量代替

命令行:make -f Makefile2 说明开始make一个名为Makefile2的文件

###############定义变量################## CC:=gcc CFLAGS:=-Iinclude CFLAGS+= -c TARGET:=bin/mymath_test DEPEND:=obj/mymath.o DEPEND+=obj/mymath_test.o $(TARGET):$(DEPEND) $(CC) -o $@ $^ obj/mymath.o:src/mymath.c $(CC) -o $@ $(CFLAGS) $^ obj/mymath_test.o:src/mymath_test.c $(CC) -o $@ $(CFLAGS) $^ clean: rm -rf $(TARGET) $(DEPEND) cd ..

其中下面 目标:=依赖列表 都是变量定义

CC:=gcc

CFLAGS:=-Iinclude

CFLAGS+= -c

TARGET:=bin/mymath_test

DEPEND:=obj/mymath.o

DEPEND+=obj/mymath_test.o

第二:

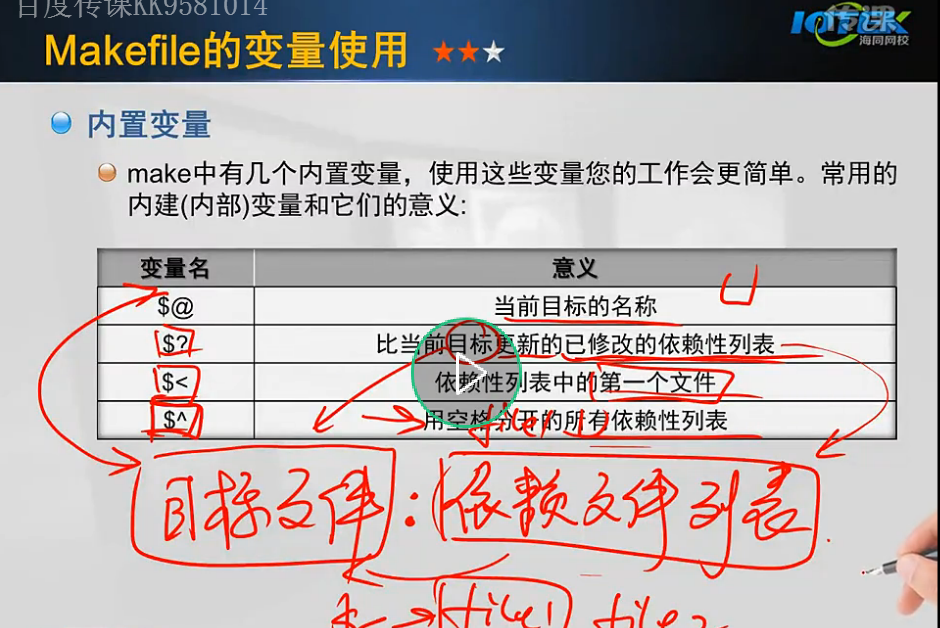

$@ 表示当前目标文件

$^表示当前要目标要依赖的全部文件

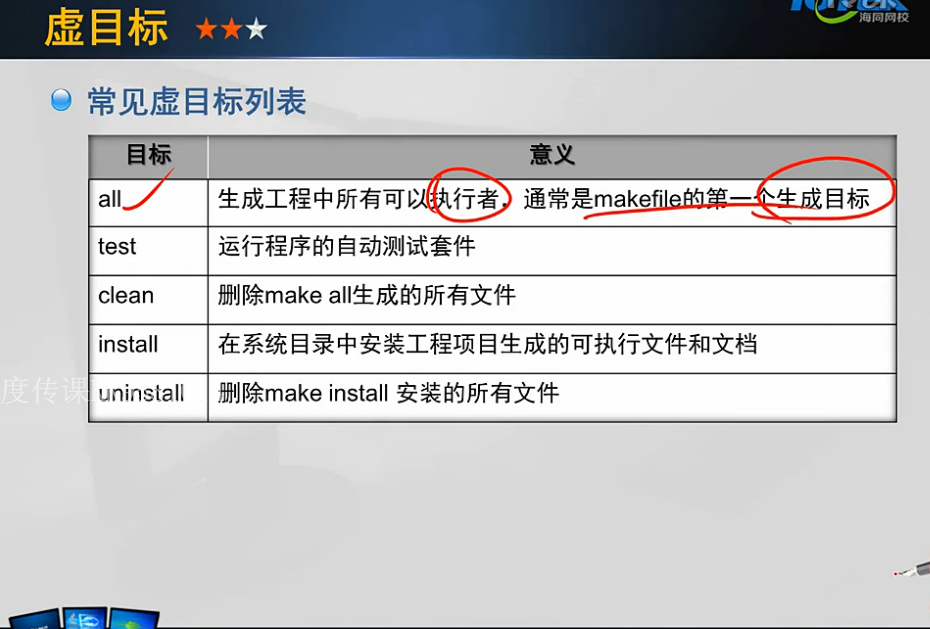

- 常见的虚目标

主要说明clearn这个虚目标

make -f Makefile2 clean 表示清除刚才make编译好的文件;就是说删除刚才编译好的可执行文件和目标.o的文件

clean: rm -rf $(TARGET) $(DEPEND) cd ..

daokr@ubuntu:/mnt/hgfs/mystudy/clession10$ make -f Makefile2 gcc -o obj/mymath.o -Iinclude -c src/mymath.c gcc -o obj/mymath_test.o -Iinclude -c src/mymath_test.c gcc -o bin/mymath_test obj/mymath.o obj/mymath_test.o daokr@ubuntu:/mnt/hgfs/mystudy/clession10$ make -f Makefile2 clean rm -fr bin/mymath_test obj/mymath.o obj/mymath_test.o

###############定义变量##################

CC:=gcc

CFLAGS:=-Iinclude

CFLAGS+= -c

TARGET:=bin/mymath_test

DEPEND:=obj/mymath.o

DEPEND+=obj/mymath_test.o

$(TARGET):$(DEPEND)#开始执行

$(CC) -o $@ $^

obj/mymath.o:src/mymath.c

$(CC) -o $@ $(CFLAGS) $^

obj/mymath_test.o:src/mymath_test.c

$(CC) -o $@ $(CFLAGS) $^

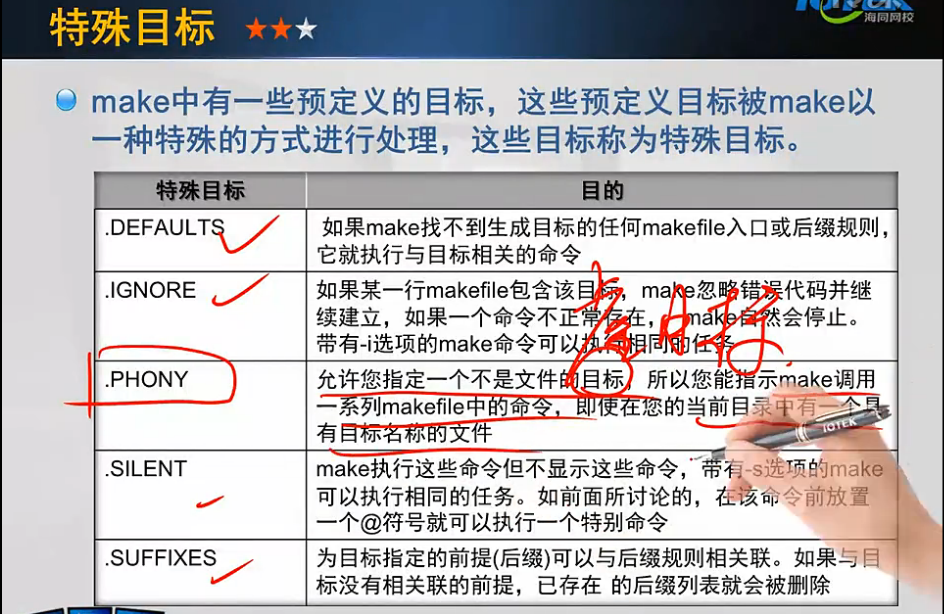

.PHONY:clean#指定clean是虚目标

clean:

rm -fr $(TARGET) $(DEPEND)