这部分讲解的是Main PLL和 PLL Controller的配置,主要介绍怎样提供DSP核 C66X CorePac需要的工作时钟;C6678除了Main PLL,还有 DDR3 PLL、PASS PLL。

1、Keystone1架构 C6678: Main PLL and PLL Controller结构图:

2、 CLKIN 是提供的参考时钟,即输入时钟,经过Main PLL后时钟输出为 PLLOUT,再输入到PLL Controller中,PLL Controller可以通过设置相关寄存器对输入的PLLOUT时钟进行分频,来获取多种不同频率的时钟,满足核心和外设的时钟需求,由图可以看出PLL Controller一共输出了16种不同的时钟;

3、16种不同的时钟中,SYSCLK1时钟用来作为核C66X CorePac的工作时钟,SYSCLK1时钟频率直接等于PLLOUT,不进行分频,所以C66X CorePac的工作时钟直接等于PLLOUT;其它时钟都具有不同的分频系数,其中只有PLLDIV2、PLLDIV5、PLLDIV8三个分频系数可以通过寄存器进行调整,其它的分频系数都是固定的;这些时钟的具体作用参考data manual;

4、如何设置核C66X CorePac的工作时钟?例如:输入时钟为100MHZ,怎样设置核C66X CorePac的工作时钟为1000MHZ,即核的工作时钟为输入参考时钟的10倍?

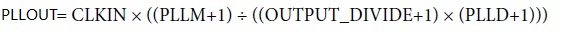

(1)、核C66X CorePac的工作时钟为SYSCLK1,即等于PLLOUT;当MAIN PLL工作在Bypass Mode时,PLLOUT的值直接等于输入的参考时钟CLKIN;当MAIN PLL工作在PLL Mode时,PLLOUT的值由输入时钟CLKIN、Main PLL的分频系数PLLD、倍增系数PLLM、以及OUTPUTDIVIDE值共同决定,公式如下: