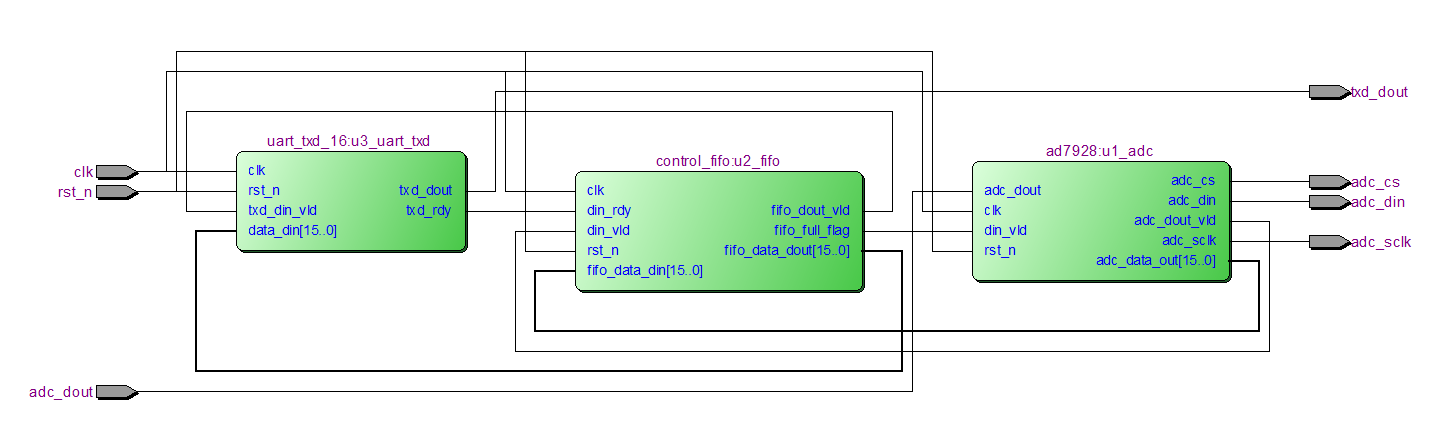

RTL视图

设计目标: 通过FPGA控制,轮流切换通道进行ADC读数据,并将数据暂存到FIFO中,同时读FIFO中的数据,通过串口打印到PC机端。FIFO采用的是16位宽的,深度用的256个字节。

1、串口设计要点:串口发送模块,采用连续不间断的发送两个字节,这样一共需要发出20个bit数据,这样就避免FIFO读出16位宽的数据进行分段发 。

(1)、首先需要设计第一个计数器,对位宽进行计数,也就是波特率,这里采用921600的波特率,1bit位宽的时间就是1/921600 s = 1085ns ,FPGA外接的时钟是50MHz,一个周期是20ns,顾1085/20 = 54.25,需要计数54个时钟周期。计数器cnt0

(2)、其次设计第二个计数器,对bit进行计数,就是准备要发送多少个bit数据出去,设计目标是连续发送两个字节,所以计数20个bit。计数器cnt1

(3)、串口发送模块还需要产出一个信号,得告诉上游模块,我已经准备好接收数据了,txd_rdy

assign txd_rdy = (cnt0_vld || txd_din_vld )? 1'b0: 1'b1; //注意两个条件不能少,尤其是txd_din_vld ,否则相对读使能信号会延迟两拍,导致读使能连续会出两个数据。详情请看上篇文章的介绍。

(4)、串口要发送数据,得需要上游给个信号,收到有效信号后,才开始启动计数器(位宽计数),txd_din_vld.

串口发送模块完整代码:

1 module uart_txd_16( 2 clk, 3 rst_n, 4 txd_din_vld, 5 data_din, 6 txd_rdy, 7 txd_dout 8 ); 9 10 parameter DATA_W = 16; 11 parameter BAUD_RATE = 54; 12 13 input clk; 14 input rst_n; 15 input txd_din_vld; 16 input [DATA_W-1:0]data_din; 17 18 output txd_rdy; 19 output txd_dout; 20 21 wire add_cnt0/* synthesis keep*/; 22 wire end_cnt0/* synthesis keep*/; 23 24 wire add_cnt1; 25 wire end_cnt1; 26 27 wire [20-1:0]data_temp; 28 29 reg cnt0_vld; 30 always @(posedge clk or negedge rst_n)begin 31 if(!rst_n)begin 32 cnt0_vld <= 0; 33 end 34 else if(txd_din_vld)begin 35 cnt0_vld <= 1; 36 end 37 else if(end_cnt1)begin 38 cnt0_vld <= 0; 39 end 40 end 41 42 reg [8:0] cnt0; 43 always @(posedge clk or negedge rst_n)begin 44 if(!rst_n)begin 45 cnt0 <= 0; 46 end 47 else if(add_cnt0)begin 48 if(end_cnt0)begin 49 cnt0 <= 0; 50 end 51 else begin 52 cnt0 <= cnt0 + 1; 53 end 54 end 55 end 56 57 assign add_cnt0 = cnt0_vld == 1; 58 assign end_cnt0 = add_cnt0 && cnt0 == BAUD_RATE - 1; 59 60 reg [5:0] cnt1; 61 always @(posedge clk or negedge rst_n)begin 62 if(!rst_n)begin 63 cnt1 <= 0; 64 end 65 else if(add_cnt1)begin 66 if(end_cnt1)begin 67 cnt1 <= 0; 68 end 69 else begin 70 cnt1 <= cnt1 + 1; 71 end 72 end 73 end 74 75 assign add_cnt1 = end_cnt0; 76 assign end_cnt1 = add_cnt1 && cnt1 == 20 - 1; //数据位宽+起始位+停止位 , 连续发送两个字节 77 78 reg[DATA_W-1 : 0] data_buf; 79 always @(posedge clk or negedge rst_n)begin 80 if(!rst_n)begin 81 data_buf <= 0; 82 end 83 else if(txd_din_vld)begin //在检测FIFO输出的有效信号时,把数据进行锁存,避免在发送过程中,data_buf 数据发生变化 84 data_buf <= data_din; 85 end 86 end 87 88 assign data_temp = {1'b1, data_buf[7:0], 1'b0, 1'b1, data_buf[15:8], 1'b0}; // 停止位 + 8bit数据 + 起始位, 低位先发 89 90 reg txd_dout; 91 always @(posedge clk or negedge rst_n)begin 92 if(!rst_n)begin 93 txd_dout <= 1; 94 end 95 else if(add_cnt0 && cnt0 == 0 && cnt1 >=0 && cnt1 < 20)begin 96 txd_dout <= data_temp[cnt1]; 97 end 98 end 99 100 assign txd_rdy = (cnt0_vld || txd_din_vld )? 1'b0: 1'b1; 101 102 endmodule

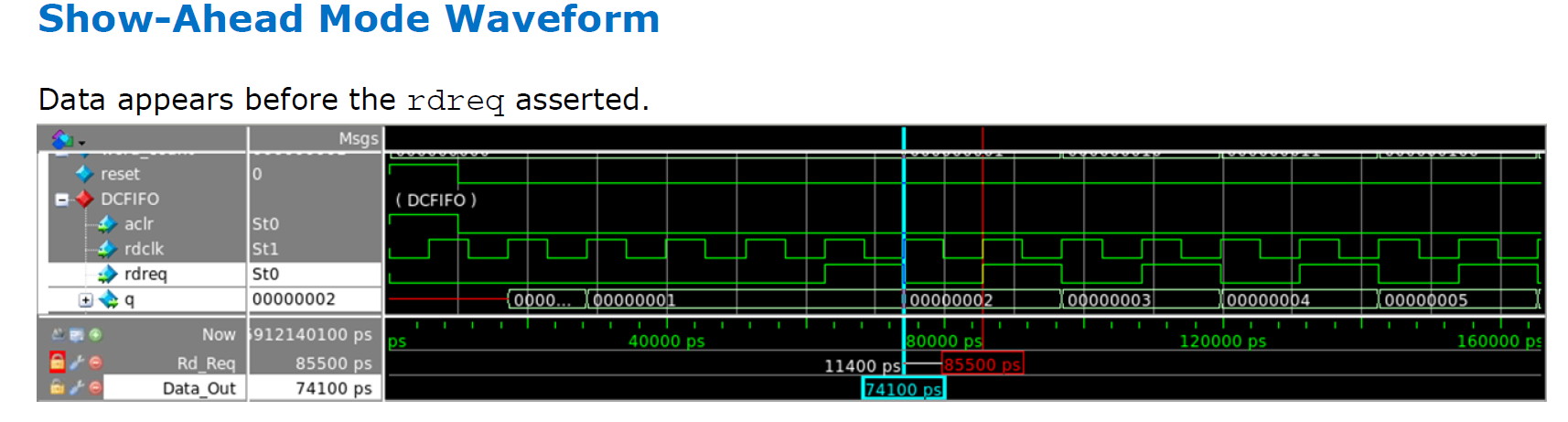

2、FIFO设计要点:

(1)、FIFO采用的是show-ahead模式,位宽是16bit,深度256,因为ADC7928采集的数据是16bit的,方便写入FIFO,所以选择16bit的位宽,由于串口模块采用的连续发送两个字节,所以读FIFO的数据不用进行分割发。

(2)、深度是256,所以在写入之前先判断写入的数量是否大于250,大于250的就暂停写入,同时会通知上游模块不要再进行ADC采集数据了。fifo_full_flag

(3)、上游ADC模块,当收完一个完整数据后,告诉FIFO可以写入了,din_vld

(4)、产生读使能,读使能采用的是组合逻辑(因为用的是show-ahead模式),同时判断FIFO是否为空empty ,且下游模块是否准备好din_rdy

assign rdreq = (empty == 0) && (din_rdy == 1);

(5)、产生读使能后,同时拿到了FIFO的数据,需要产生一个信号告诉下游模块,准备接收数据了fifo_dout_vld

记住关键点:注意数据对齐,在读使能有效期间,数据也是在同一拍

FIFO控制模块完整代码:

1 module control_fifo( 2 clk, 3 rst_n, 4 din_vld, 5 fifo_data_din, 6 din_rdy,//下游模块准备好信号 7 fifo_dout_vld, //通知下游模块准备收数据 8 fifo_data_dout, 9 fifo_full_flag 10 ); 11 parameter DATA_WRW = 16; 12 input clk; 13 input rst_n; 14 input din_vld; 15 input [DATA_WRW-1:0] fifo_data_din; 16 input din_rdy; 17 18 output fifo_dout_vld; 19 output[DATA_WRW-1:0] fifo_data_dout; 20 output fifo_full_flag; 21 22 reg fifo_full_flag; 23 wire rdreq; 24 reg wrreq; 25 wire [DATA_WRW-1:0] q/* synthesis keep*/; 26 wire [7:0]usedw/* synthesis keep*/; 27 my_fifo my_fifo_inst ( 28 .clock ( clk ), 29 .data ( fifo_data_din ), 30 .rdreq ( rdreq ), 31 .wrreq ( wrreq ), 32 .empty ( empty ), 33 .full ( full), 34 .q ( q ), 35 .usedw ( usedw) 36 ); 37 38 //assign wrreq = full? 1'b0 : din_vld; 39 40 always @(*)begin 41 if(usedw >= 250)begin 42 wrreq = 0; 43 fifo_full_flag = 0; 44 end 45 else begin 46 wrreq = din_vld; 47 fifo_full_flag = 1; 48 end 49 50 end 51 52 assign rdreq = (empty == 0) && (din_rdy == 1); 53 54 reg [DATA_WRW-1:0] fifo_data_dout; 55 always @(posedge clk or negedge rst_n)begin 56 if(!rst_n)begin 57 fifo_data_dout <= 0; 58 end 59 else begin 60 fifo_data_dout <= q; 61 end 62 end 63 64 reg fifo_dout_vld; 65 always @(posedge clk or negedge rst_n)begin 66 if(!rst_n)begin 67 fifo_dout_vld <= 0; 68 end 69 else begin 70 fifo_dout_vld <= rdreq; 71 end 72 end 73 74 endmodule

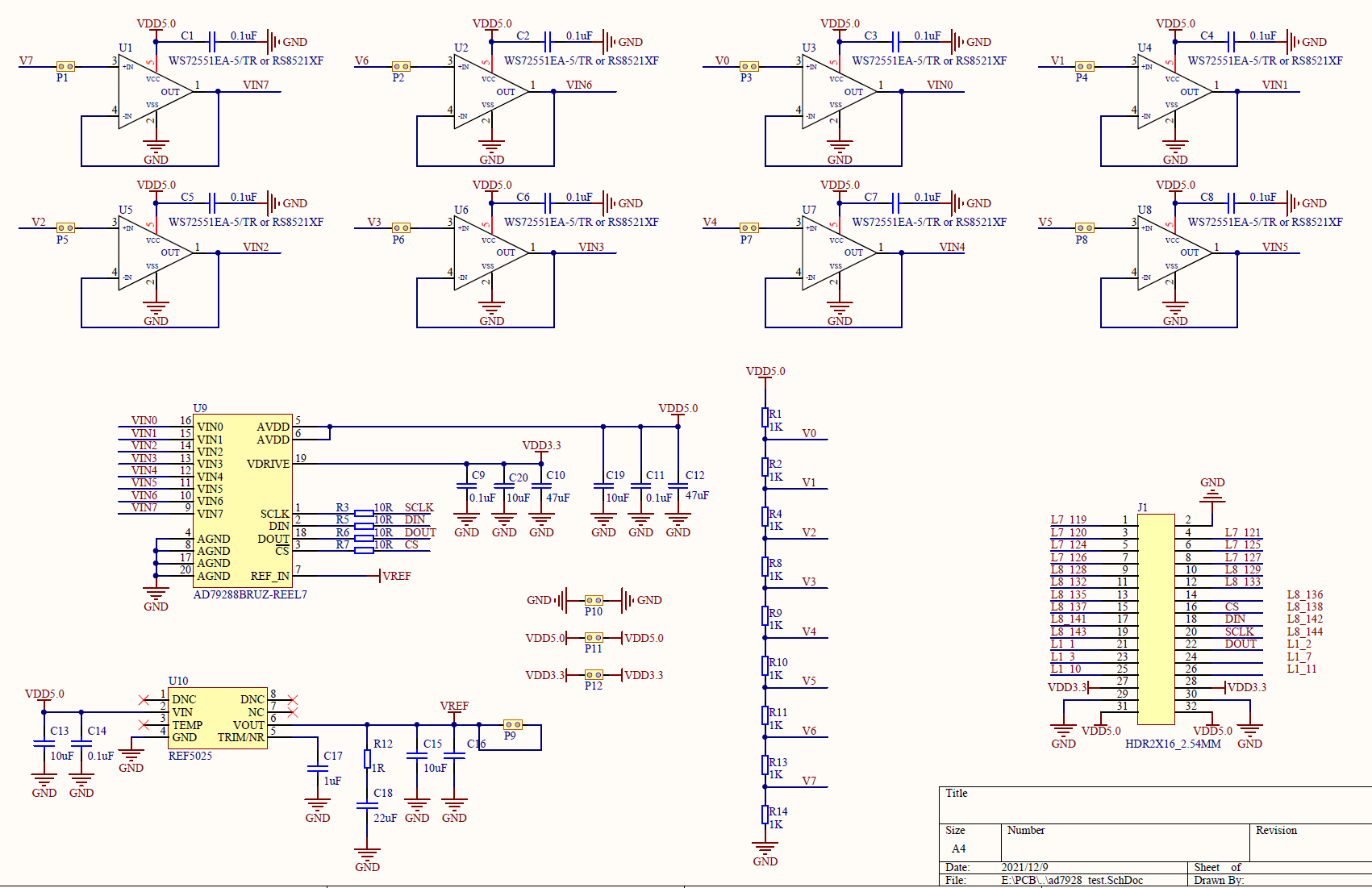

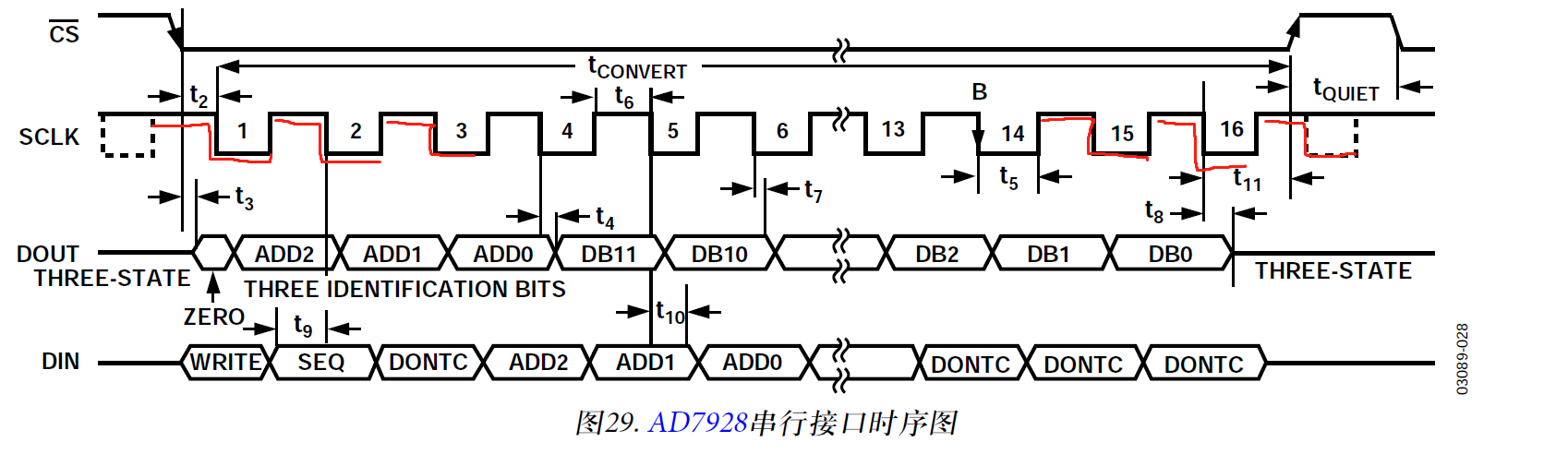

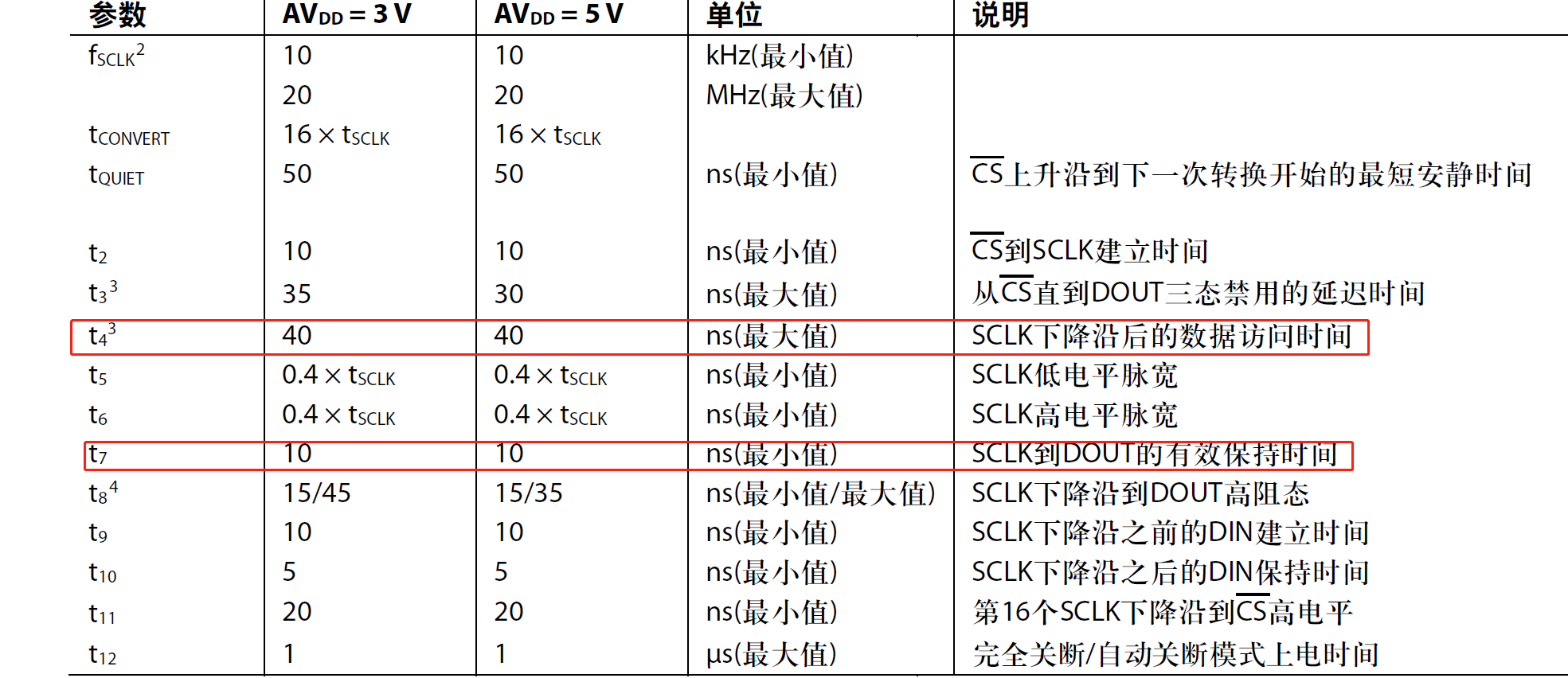

3、ad7928设计要点:

首先查看手册时序图,第一次看这种时序图,第一感觉,时钟从哪里开始数比较好,就让人拿不定注意,是从前头的虚线那开始,结尾虚线结束吗? 就会有各种疑问,网上搜资料教程也没具体详细将这一点。所以干脆不要想那么多,按自己的思路来

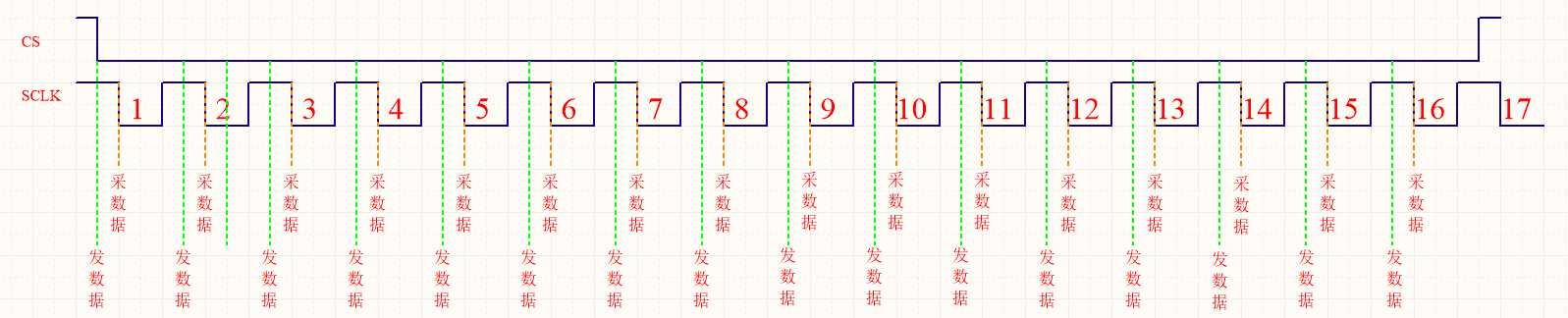

我是这样数时钟的,如下图红色线,意味着要产生17个这样的完整时钟,接下就设计数器了:

(1)、第一个计数器,产生sclk时钟,也就是位宽,这里采用4分频,sclk也就是50/4 = 12.5MHz,查看手册,该时钟最大可以到20MHz,计数cnt0

(2)、第二个计数器,对bit数量进行计数,发数据和收数据都需要借助这个计数器cnt1

(3)、我们可以知道在哪个阶段发数据,何时收数据,所以需结合两个计数器进行操作。

(4)、产生CS信号,可以在第一个时钟的高电平中间拉低CS信号,在第17个时钟的高电平中间位置拉高就行。

(5)、产生din 信号,也就是发出数据给AD7928,看时序图,又有点蒙了,到底是在sclk的上升沿发,还是高电平期间发数据呢,因为第一个数据是在sclk高电平期间就发出了,所以后面都采用在高电平期间将数据送到din上,

也就是CS拉低的同时,发出数据。

(6)、接收dout上的数据,看时序图还是蒙了,到底是高电平期间采数据,还是下降沿采数据,可以查看t4和 t7说明,t4是sclk下降沿到dout的访问时间,数据保持时间是t7,说明是在下降沿时采数据(其实我有点纳闷,为啥不是在高电平期间采样,在高电平期间,我看dout时序应该是最稳的)

OK 我们还是按要求来,在sclk时钟下降沿采数据。

采数据 、发数据、 CS拉低拉高位置就都已经确认下来了,如下图所示,绿色虚线位置发 送数据 , 橘黄色虚线位置是 采数据 ,CS 是在第一个时钟周期的高电平期间(绿色虚线)拉低,在第17个时钟周期的高电平期间拉高。知道了关键节点,就可以写代码了。

ad7928的完整代码:

1 module ad7928( 2 clk, 3 rst_n, 4 adc_dout, 5 adc_cs, 6 adc_sclk, 7 adc_din, 8 din_vld, 9 adc_dout_vld, 10 adc_data_out 11 ); 12 13 parameter WRITE = 1'b1 ; 14 parameter SEQ = 1'b0 ; 15 parameter PM1 = 1'b1 ; 16 parameter PM0 = 1'b1 ; 17 parameter SHADOW = 1'b0 ; 18 parameter RANGE = 1'b0 ; 19 parameter CODING = 1'b1 ; 20 parameter ADDRES = 3'b010; 21 22 input clk ; 23 input rst_n ; 24 input adc_dout; 25 input din_vld ; 26 27 output adc_cs ; 28 output adc_sclk; 29 output adc_din ; 30 output adc_dout_vld; 31 output [16-1:0] adc_data_out; 32 33 wire add_cnt0; 34 wire end_cnt0; 35 36 wire add_cnt1; 37 wire end_cnt1; 38 39 wire add_cnt2; 40 wire end_cnt2; 41 42 wire [15:0] data; 43 44 reg [2:0] cnt0; 45 always @(posedge clk or negedge rst_n)begin 46 if(!rst_n)begin 47 cnt0 <= 0; 48 end 49 else if(add_cnt0)begin 50 if(end_cnt0)begin 51 cnt0 <= 0; 52 end 53 else begin 54 cnt0 <= cnt0 + 1; 55 end 56 end 57 end 58 59 assign add_cnt0 = din_vld; 60 assign end_cnt0 = add_cnt0 && cnt0 == 4-1; 61 62 63 reg [4:0] cnt1; 64 always @(posedge clk or negedge rst_n)begin 65 if(!rst_n)begin 66 cnt1 <= 0; 67 end 68 else if(add_cnt1)begin 69 if(end_cnt1)begin 70 cnt1 <= 0; 71 end 72 else begin 73 cnt1 <= cnt1 + 1; 74 end 75 end 76 end 77 78 assign add_cnt1 = end_cnt0; 79 assign end_cnt1 = add_cnt1 && cnt1 == 17-1; 80 81 reg [3:0] cnt2; 82 always @(posedge clk or negedge rst_n)begin 83 if(!rst_n)begin 84 cnt2 <= 0; 85 end 86 else if(add_cnt2)begin 87 if(end_cnt2)begin 88 cnt2 <= 0; 89 end 90 else begin 91 cnt2 <= cnt2 + 1; 92 end 93 end 94 end 95 96 assign add_cnt2 = end_cnt1; 97 assign end_cnt2 = add_cnt2 && cnt2 == 8-1; 98 99 100 reg adc_sclk; 101 always @(posedge clk or negedge rst_n)begin 102 if(!rst_n)begin 103 adc_sclk <= 1; 104 end 105 else if(add_cnt0 && cnt0 >= 2 && cnt0 < 4)begin 106 adc_sclk <= 0; 107 end 108 else if(add_cnt0 && cnt0 >= 0 && cnt0 < 2)begin 109 adc_sclk <= 1; 110 end 111 end 112 113 reg adc_cs; 114 always @(posedge clk or negedge rst_n)begin 115 if(!rst_n)begin 116 adc_cs <= 1; 117 end 118 else if(add_cnt0 && cnt0 == 2-1 && cnt1 == 1-1)begin 119 adc_cs <= 0; 120 end 121 else if(add_cnt0 && cnt0 == 2-1 && cnt1 == 17-1)begin 122 adc_cs <= 1; 123 end 124 end 125 126 reg [2:0] channel_sel; 127 always @(posedge clk or negedge rst_n)begin 128 if(!rst_n)begin 129 channel_sel <= 3'b000; 130 end 131 else begin 132 case(cnt2) 133 0 : channel_sel <= 3'b000; 134 1 : channel_sel <= 3'b001; 135 2 : channel_sel <= 3'b010; 136 3 : channel_sel <= 3'b011; 137 4 : channel_sel <= 3'b100; 138 5 : channel_sel <= 3'b101; 139 6 : channel_sel <= 3'b110; 140 7 : channel_sel <= 3'b111; 141 default : channel_sel <= 3'b000; 142 endcase 143 end 144 end 145 146 reg adc_din; //给ADC送数据,进行通道切换 147 always @(posedge clk or negedge rst_n)begin 148 if(!rst_n)begin 149 adc_din <= 1; 150 end 151 else if(add_cnt0 && cnt0 == 2-1 && cnt1 >=0 && cnt1 < 16)begin 152 adc_din = data[15-cnt1]; 153 end 154 end 155 156 assign data = {WRITE, SEQ, 1'b0, channel_sel, PM1, PM0, SHADOW, 1'b0, RANGE, CODING, 4'b0000}; 157 158 reg [16-1:0] data_temp; //从ADC上读数据 159 always @(posedge clk or negedge rst_n)begin 160 if(!rst_n)begin 161 data_temp <= 15'b000_0000_0000_0000; 162 end 163 else if(add_cnt0 && cnt0 == 3-1 && cnt1 >= 0 && cnt1 < 16)begin 164 data_temp[15-cnt1] <= adc_dout; 165 end 166 end 167 168 reg [16-1:0] adc_data_out; //将收到的完整数据进行锁存 169 always @(posedge clk or negedge rst_n)begin 170 if(!rst_n)begin 171 adc_data_out <= 0; 172 end 173 else if(end_cnt1)begin 174 adc_data_out <= data_temp; 175 end 176 end 177 178 reg adc_dout_vld; //数据有效时,同时产生一个有效标志 179 always @(posedge clk or negedge rst_n)begin 180 if(!rst_n)begin 181 adc_dout_vld <= 0; 182 end 183 else if(end_cnt1)begin 184 adc_dout_vld <= 1; 185 end 186 else begin 187 adc_dout_vld <= 0; 188 end 189 end 190 191 endmodule

顶层设计代码:

1 module ad7928_fifo_top( 2 clk, 3 rst_n, 4 adc_dout, 5 6 adc_cs, 7 adc_sclk, 8 adc_din, 9 txd_dout 10 ); 11 12 input clk; 13 input rst_n; 14 input adc_dout; 15 16 output adc_cs; 17 output adc_sclk; 18 output adc_din; 19 output txd_dout; 20 21 wire [16-1 : 0] fifo_data_dout; 22 wire [16-1 : 0] adc_data_out; 23 wire adc_dout_vld; 24 wire txd_rdy; 25 wire fifo_dout_vld; 26 wire fifo_full_flag; 27 28 ad7928 u1_adc( 29 .clk (clk), 30 .rst_n (rst_n), 31 .adc_dout (adc_dout), 32 .adc_cs (adc_cs), 33 .adc_sclk (adc_sclk), 34 .adc_din (adc_din), 35 .din_vld (fifo_full_flag), 36 .adc_dout_vld (adc_dout_vld), 37 .adc_data_out (adc_data_out) 38 ); 39 40 control_fifo u2_fifo( 41 .clk(clk), 42 .rst_n(rst_n), 43 .din_vld(adc_dout_vld), 44 .fifo_data_din(adc_data_out), 45 .din_rdy(txd_rdy),//下游模块准备好信号 46 .fifo_dout_vld(fifo_dout_vld), //通知下游模块准备收数据 47 .fifo_data_dout(fifo_data_dout), 48 .fifo_full_flag(fifo_full_flag) 49 ); 50 51 uart_txd_16 u3_uart_txd( 52 .clk(clk), 53 .rst_n(rst_n), 54 .txd_din_vld(fifo_dout_vld), 55 .data_din(fifo_data_dout), 56 .txd_rdy(txd_rdy), 57 .txd_dout(txd_dout) 58 ); 59 60 endmodule

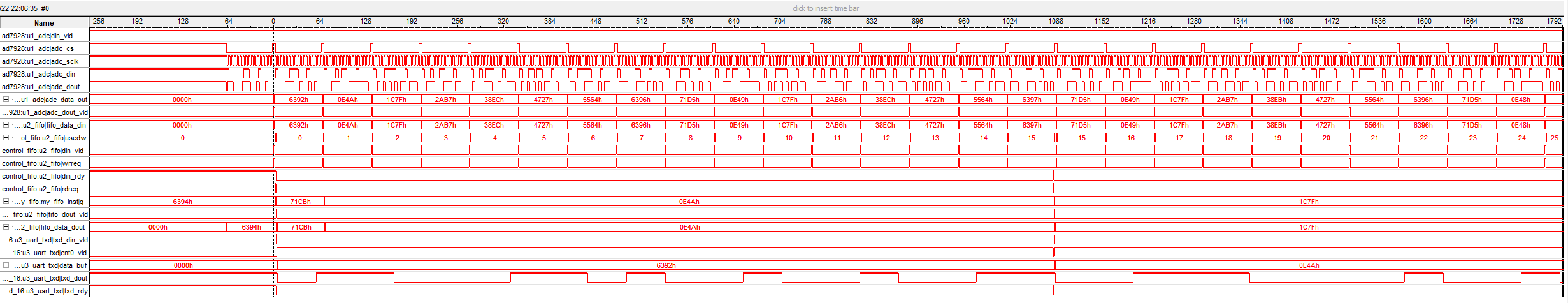

signal TAB波形:

串口打印的数据:测试时,先按住复位按键,然后点开始运行仿真触发,释放复位按键,然后迅速关闭串口,拉到最开始的位置对比数据,因为串口会一直在打印数据,且速率还是满块的。

可以对比下,第一个数据是6392 ,0E4A ,1C7F, 2AB7, 38EC, 4727, 5564 , 6396 , 71D5, ...和仿真上的数据是完全对的,第一个数据6392 其实是第6个通道的数据。由于第一次发数据时,ADC同时也会送出数据,而此时送出的数据我们并没有配置通道,所以ADC估计会根据上一回的配置进行送出数据。

0E4A ,1C7F, 2AB7, 38EC, 4727, 5564 , 6396 , 71D5 从这数据上来看, 可以明显看出是哪个通道的,0E4A 是0通道,1C7F是1通道的,2AB7是2通道的,具体可以看手册上的dout数据说明。

0通道电压:0E4A , E4A 转十进制 3658,

3658 * 5 /4096 = 4.46533V = 4.5V ,

从原路图上计算:V0 = (R2+R4+R8+R9+R10+R11+R13+R14) / (R1 +R2+R4+R8+R9+R10+R11+R13+R14) * 5 = 8 / 9 * 5 = 4.444V, 这是理论计算电压,用万用实测的是4.5V,说明ADC测试的电压还是蛮准的。

其他通道可以以此类推进行计算。